纯是博客,供大家参考。

原理

三输入表决器是一种数字电路,用于根据三个输入信号的状态进行投票决策,通常用于冗余系统中,以提高可靠性和容错能力。它的基本原理是:

1. **输入**:

- 三个输入信号,通常标记为 A、B 和 C。这些信号可以代表不同的来源或传感器的输出。

2. **投票机制**:

- 表决器通过投票机制决定最终的输出。具体来说,如果至少有两个输入信号相同,那么输出将为该相同的值;如果三个输入信号都不相同,通常会选择一个默认值(例如 0)。

3. **逻辑实现**:

- 表决器的输出 Y 可以通过以下逻辑表达式来描述:

- \( Y = (A \& B) | (A \& C) | (B \& C) \)

- 这里的逻辑运算符表示:

- `&` 是与运算(AND),

- `|` 是或运算(OR)。

4. **示例**:

- 输入组合:

- 输入 A = 1, B = 1, C = 0 → 输出 Y = 1

- 输入 A = 0, B = 1, C = 1 → 输出 Y = 1

- 输入 A = 0, B = 0, C = 1 → 输出 Y = 0

- 输入 A = 0, B = 0, C = 0 → 输出 Y = 0

原理介绍完了,我们接下来将用Quartus II和里面自带的Modelsim进行联合仿真实验。

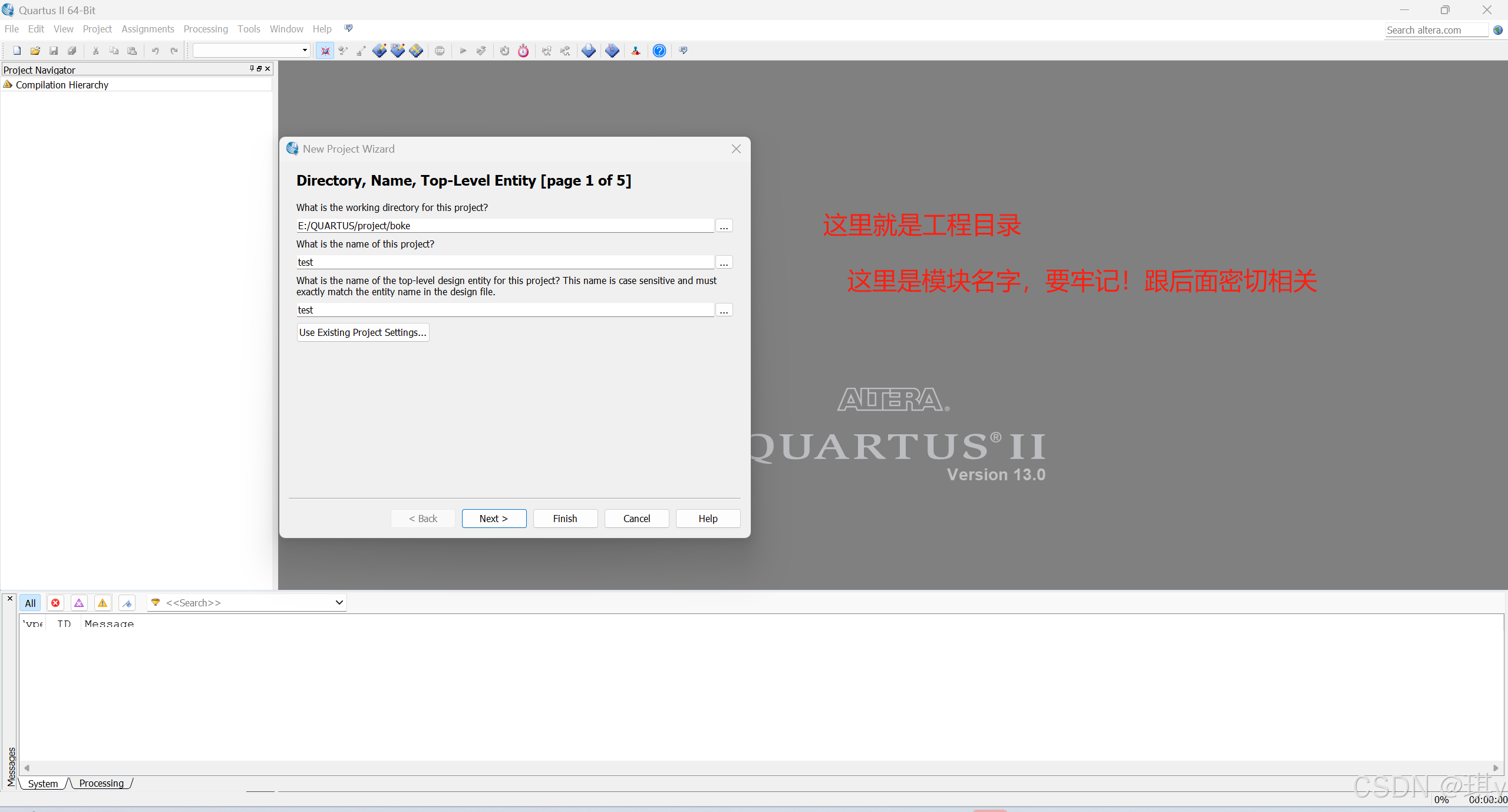

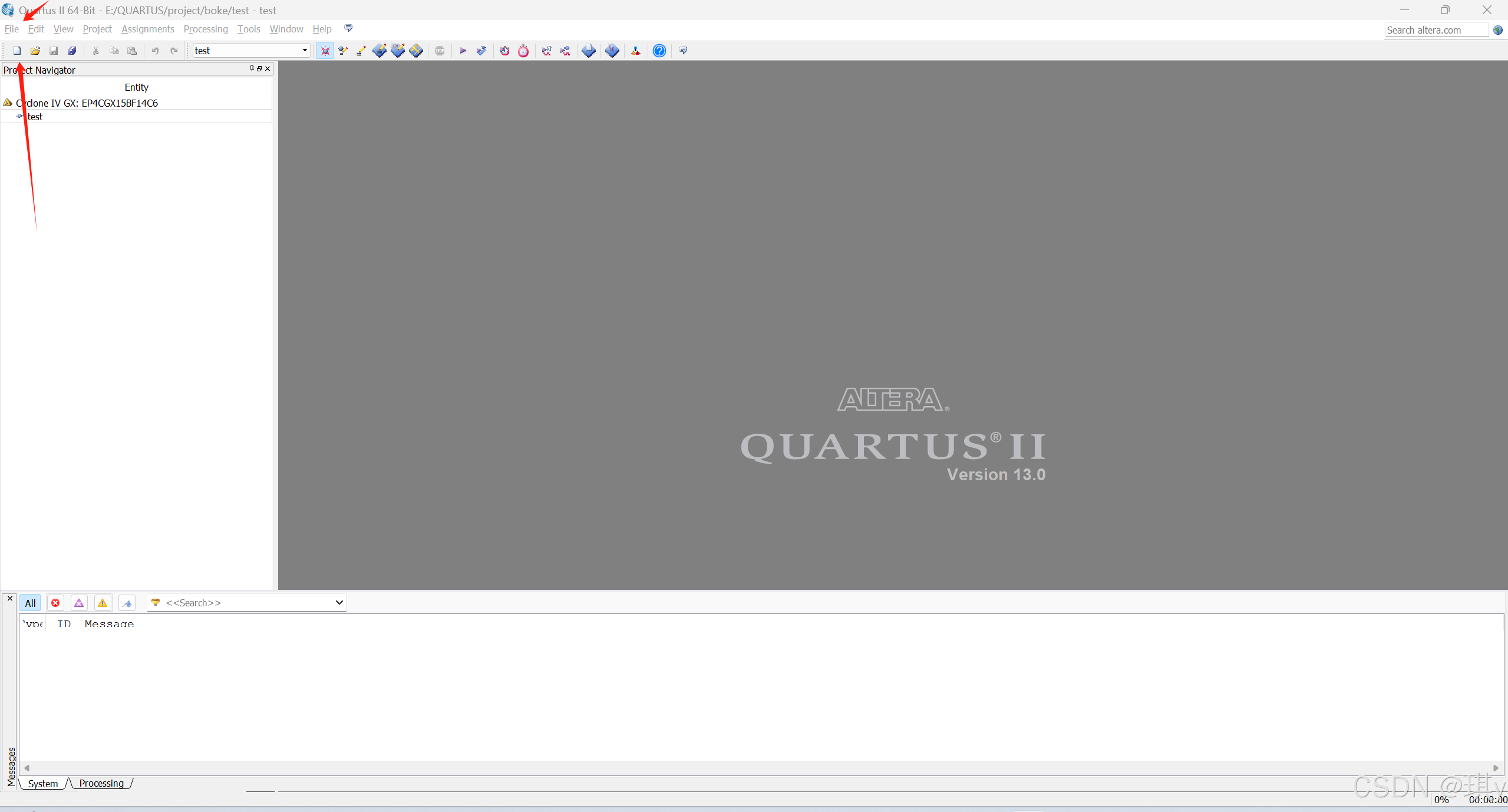

1创建程序

在这里模块名字比较重要,对于初学者来讲,常常容易忽视的一个点!

2

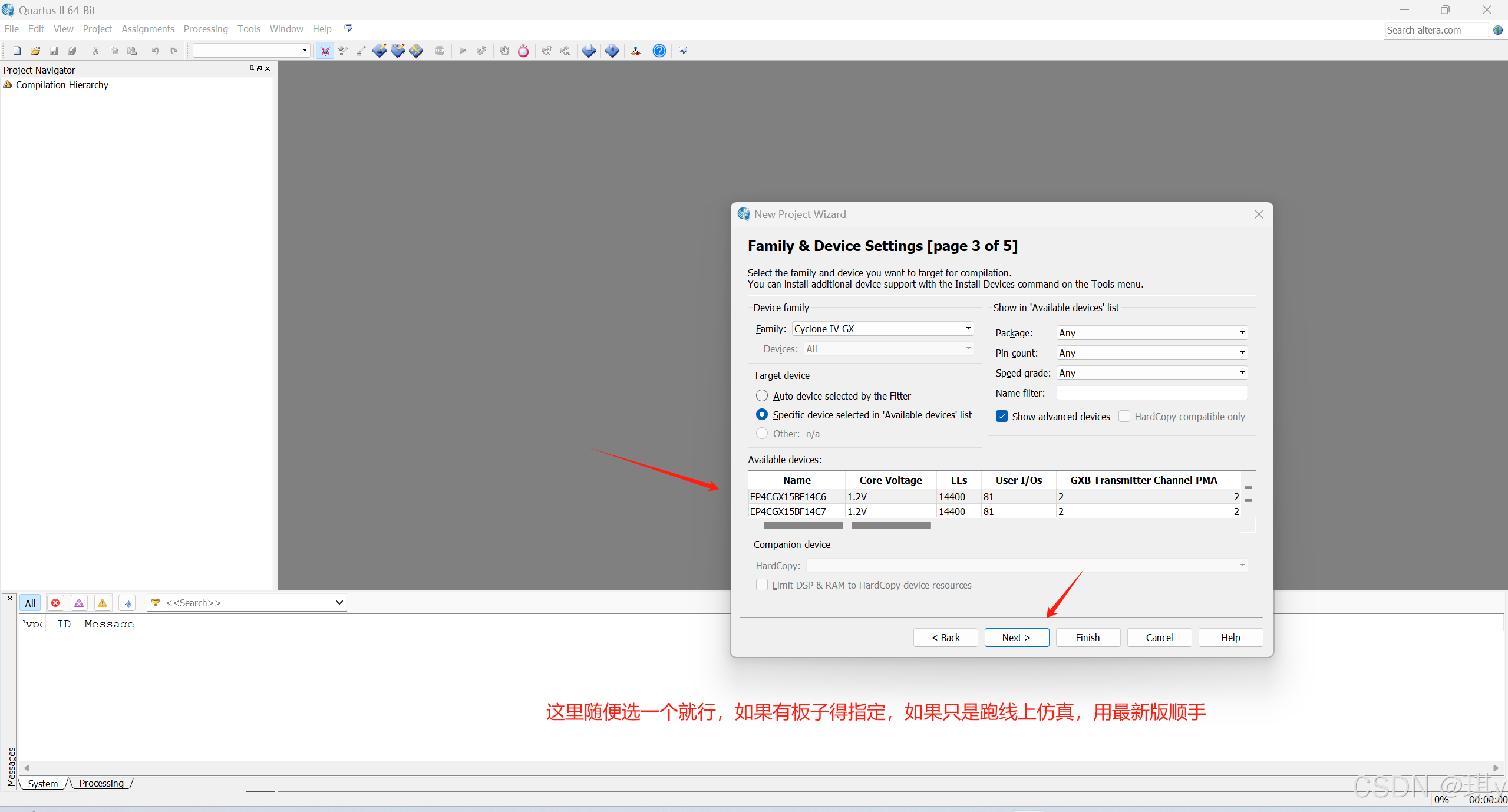

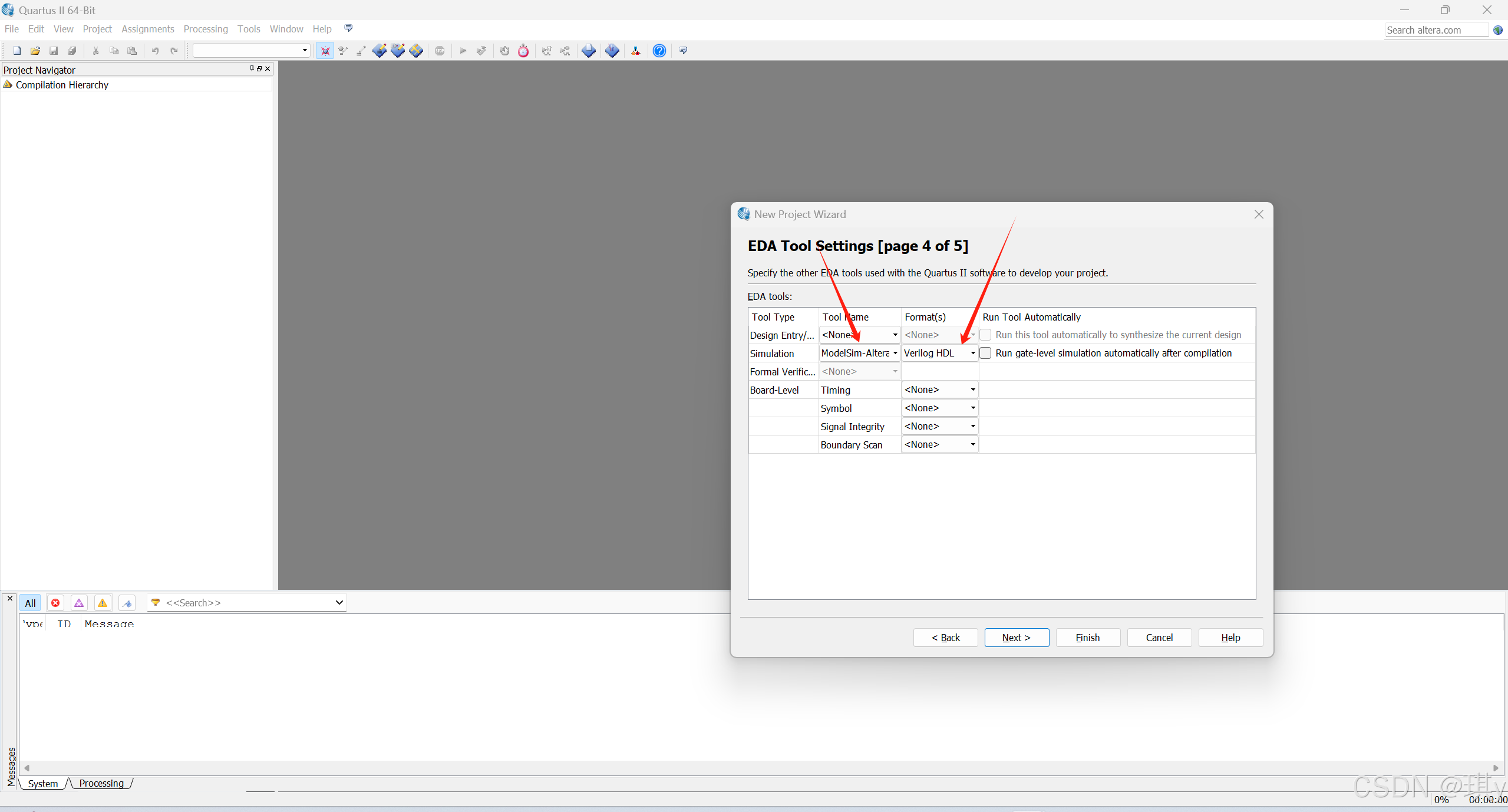

3这里选择Verilog hdl语言,以及modelsim-altera或者modelsim。(作者是两个都有,后面会贴图)

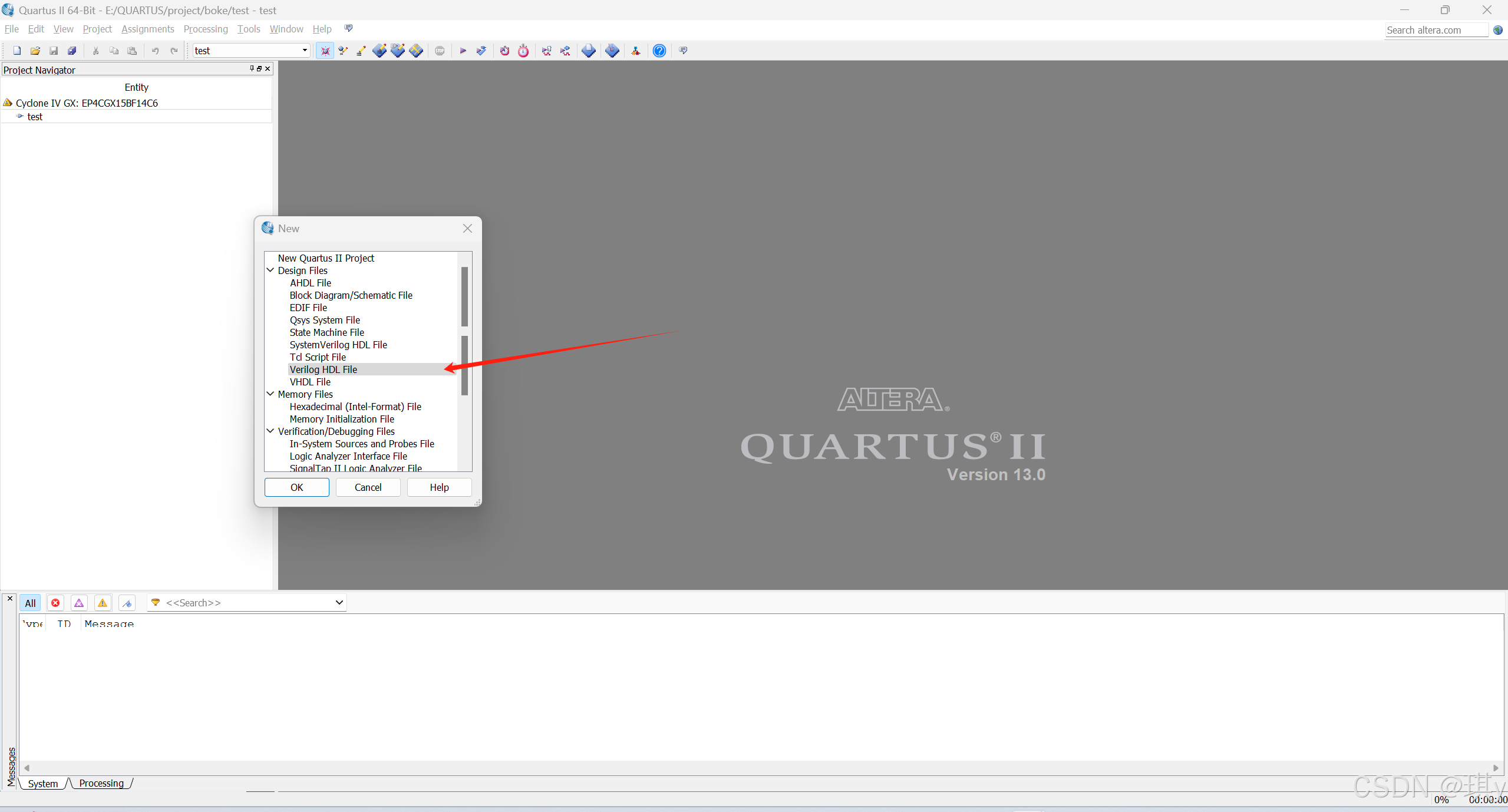

4:创建完成之后,点击白色或者 File->new,创建空白文档——>选择Verilog hdl语言

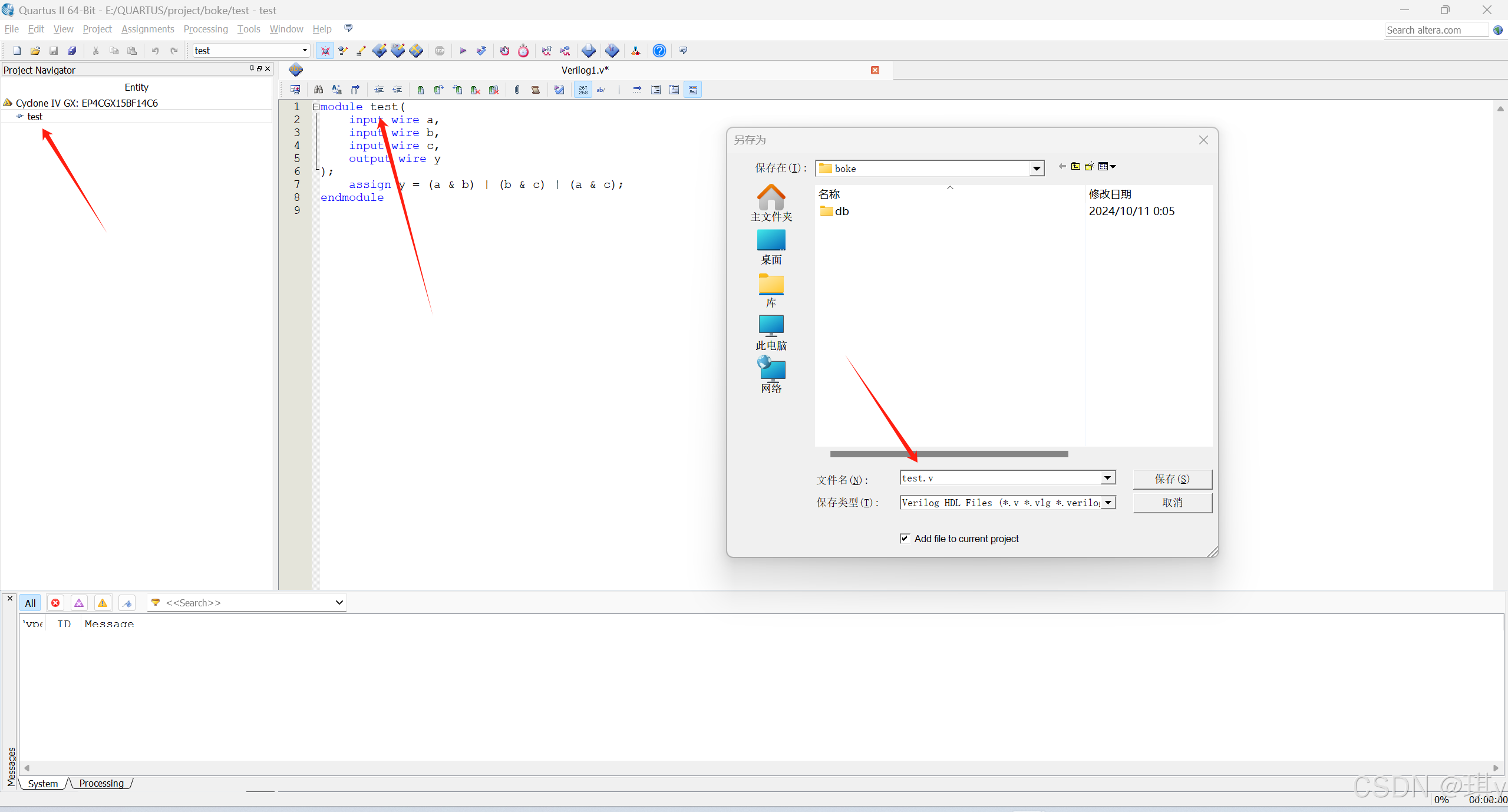

5:ctrl+s 保存

文件,要保证这三块地方一样!必须!

代码贴图

module test(

input wire a,

input wire b,

input wire c,

output wire y

);

assign y = (a & b) | (b & c) | (a & c);

endmodule

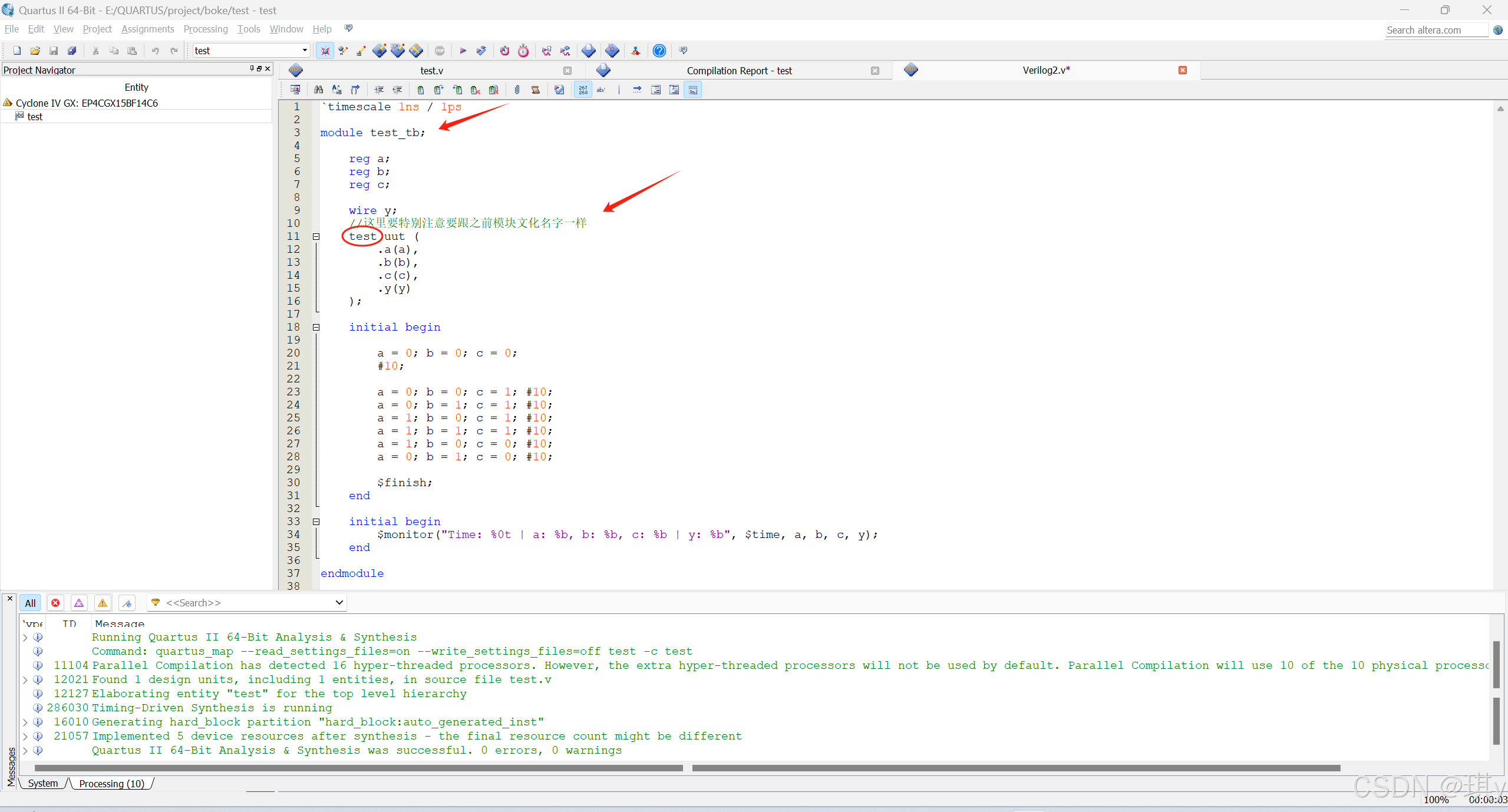

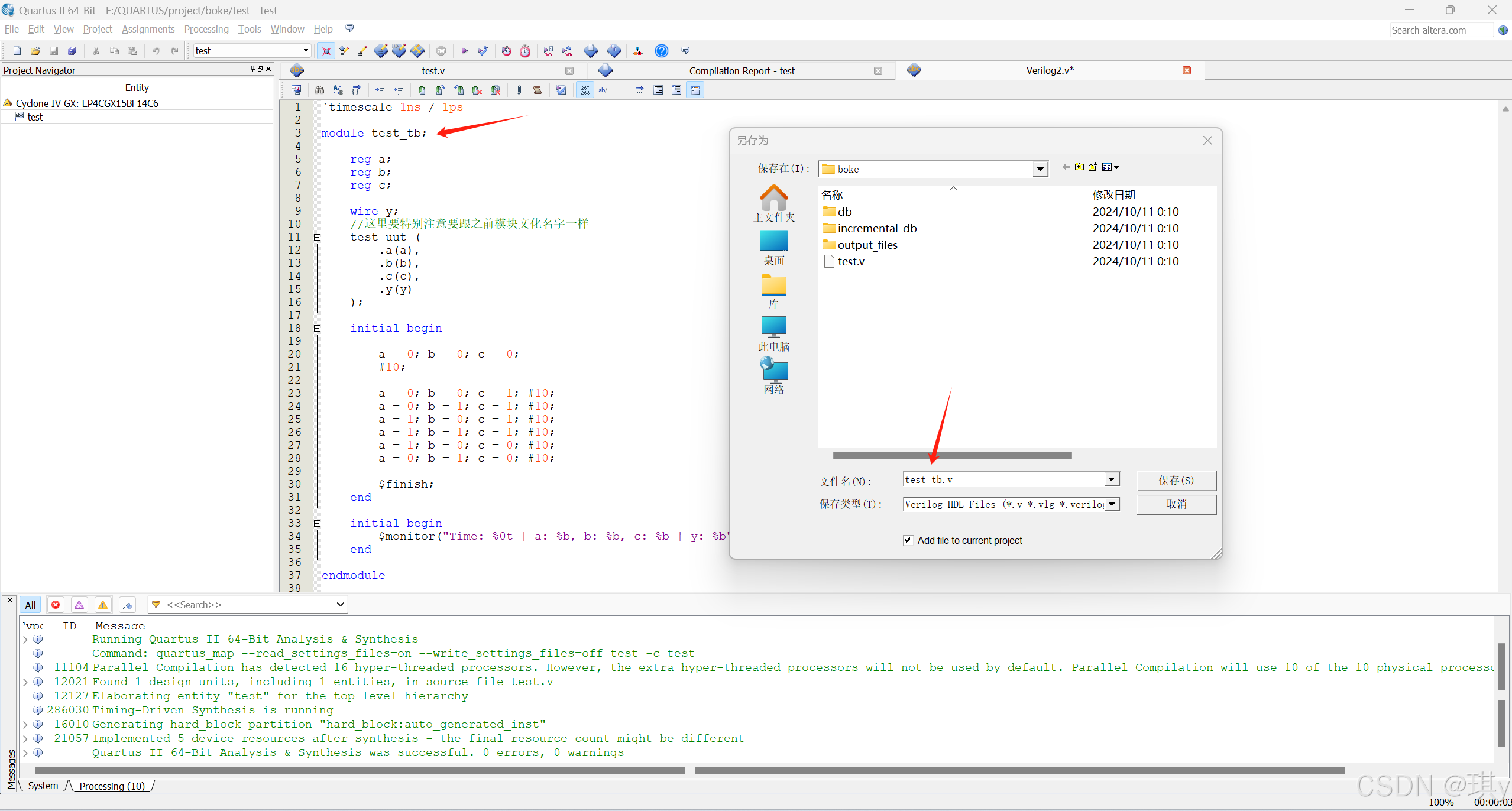

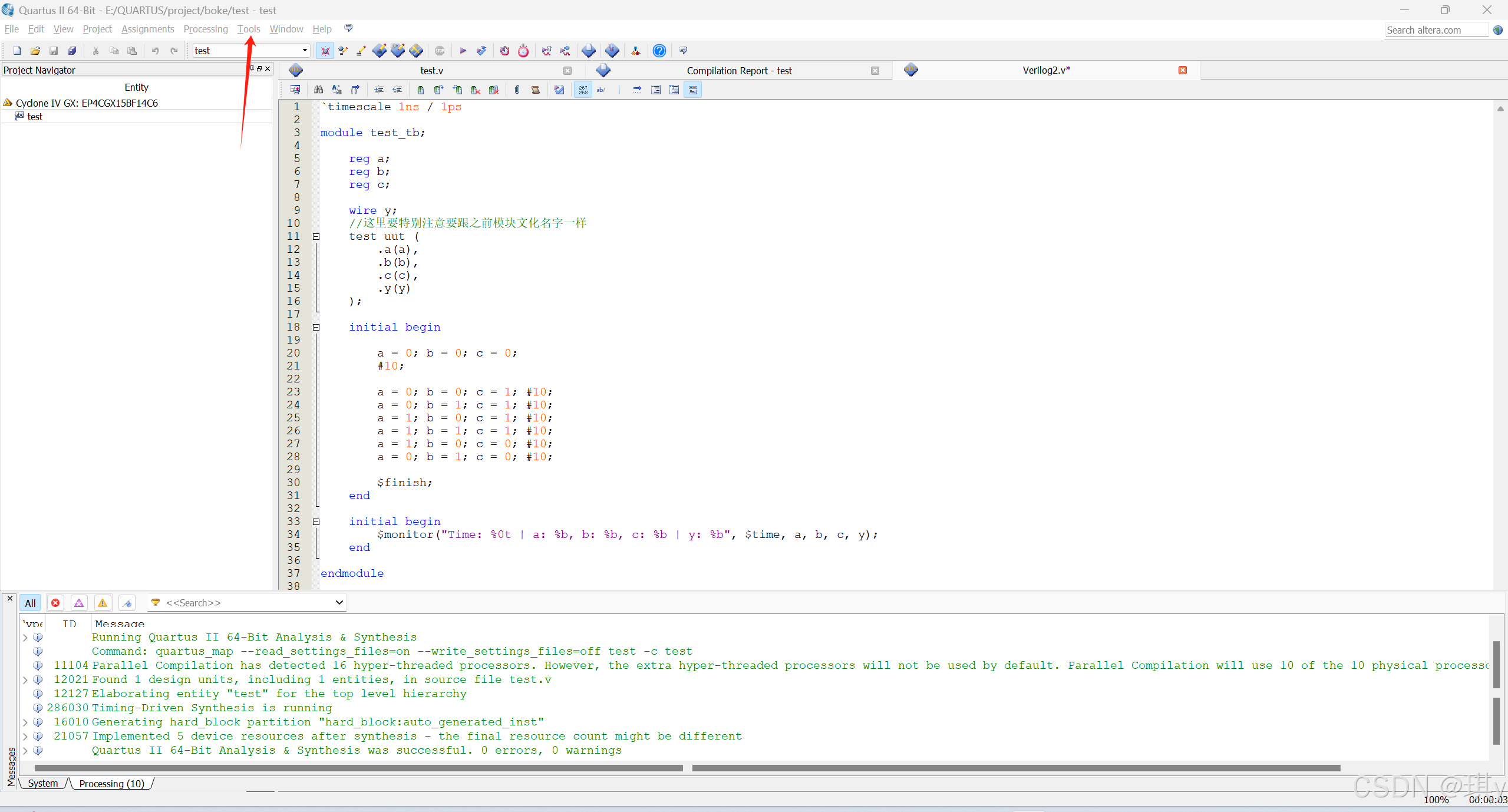

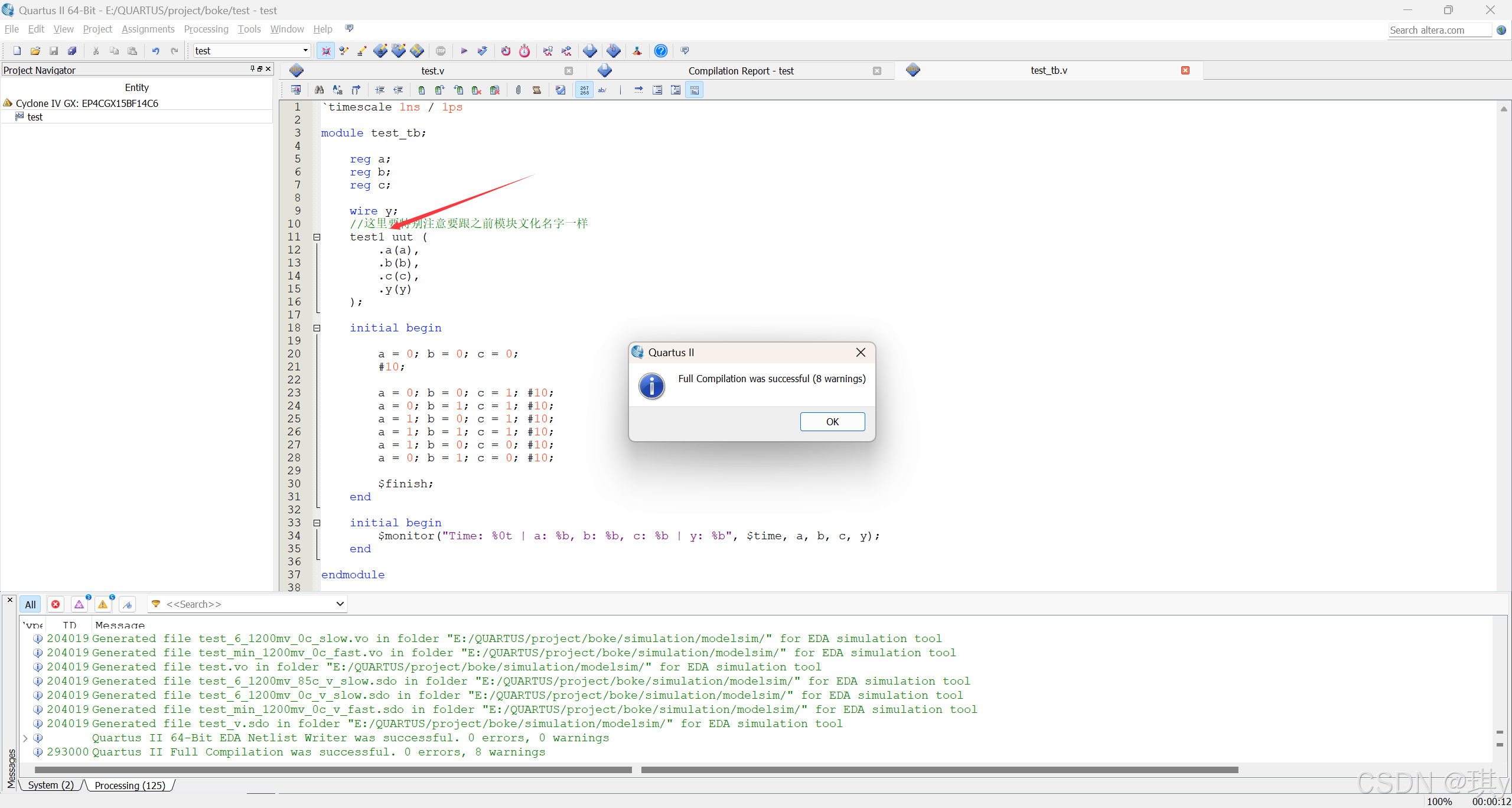

6.重复上述操作 建一个测试文件

温馨提示!!这里需要保证跟之前模块名字一样,也不能乱取!所有要求保证文件名一定不能出错。否则仿真的时候会出现

# Error: Error loading design #Pausing macro execution

这种错误。作者亲测(特别是会cv的小伙伴们,狗头哈哈

7. CTRL + S ,保存,保证这两块地方文件名相同!

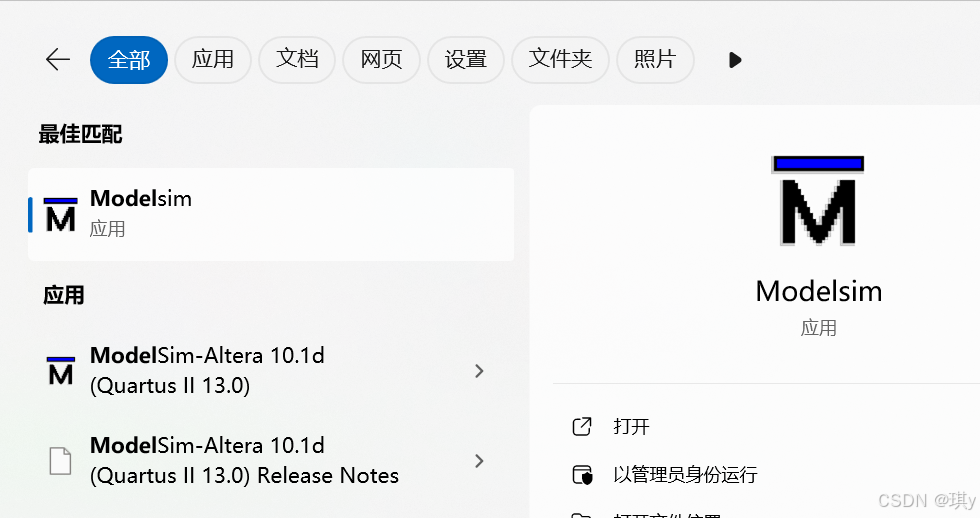

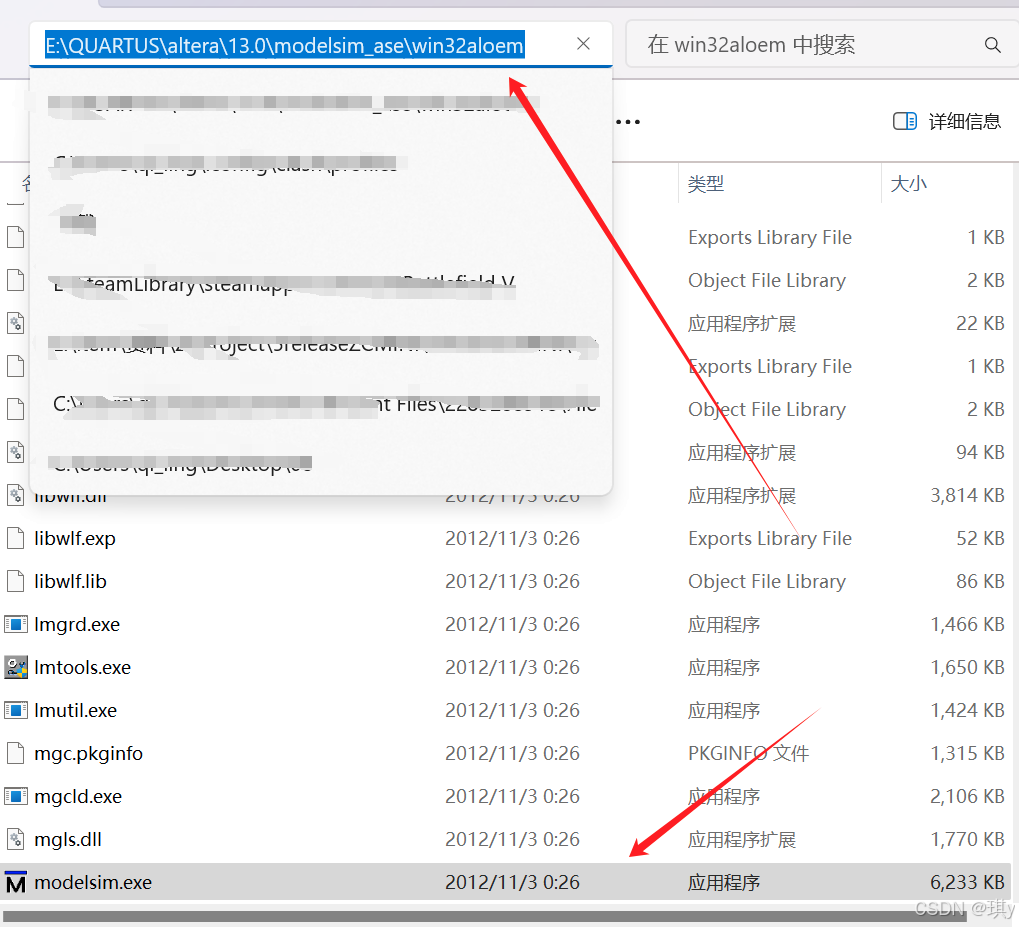

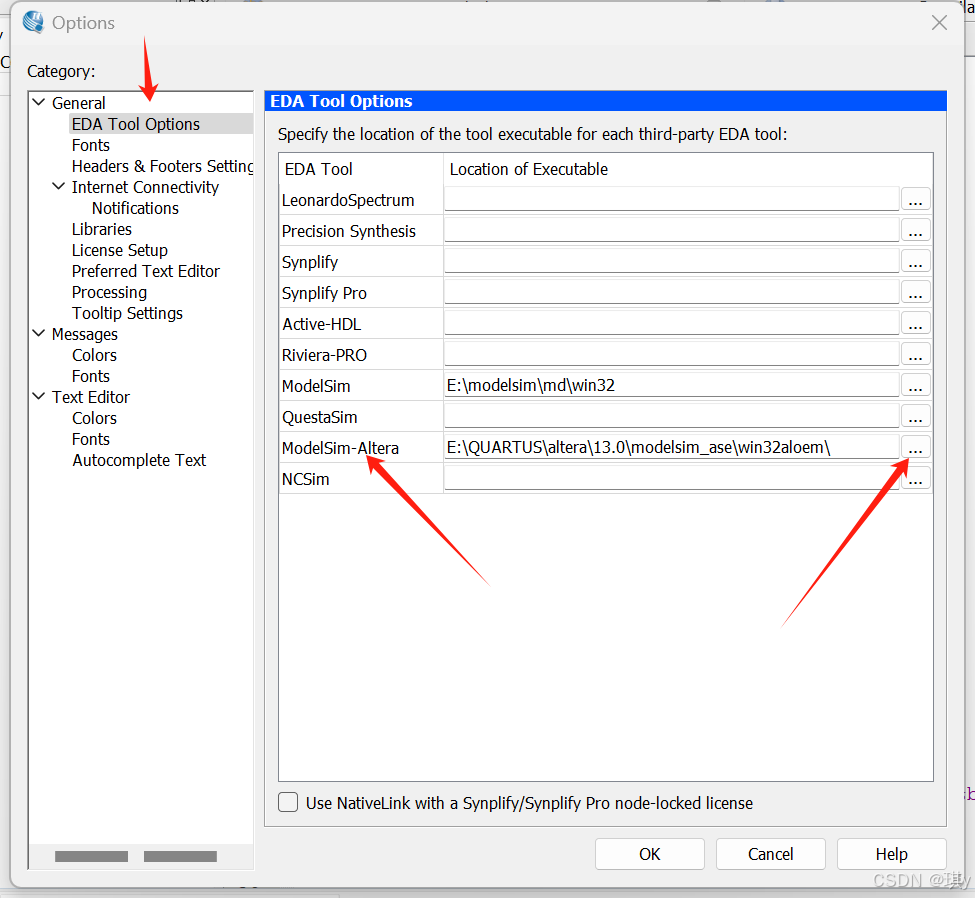

8.我们开始查看modelsim的配置,作者有modelsim 以及 modelsim-Altera。当初下载quartus 他是自带 后者的,所以前面步骤我们选择的是modelsim-Altera。我们找到他的路径

我们将这个地址复制下来,跟着图片顺序走。

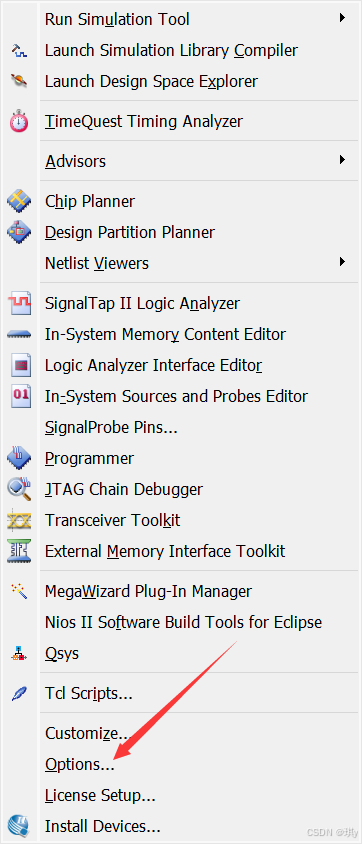

到这步modelsim-Altera 就配置好了!我们进行下一步配置

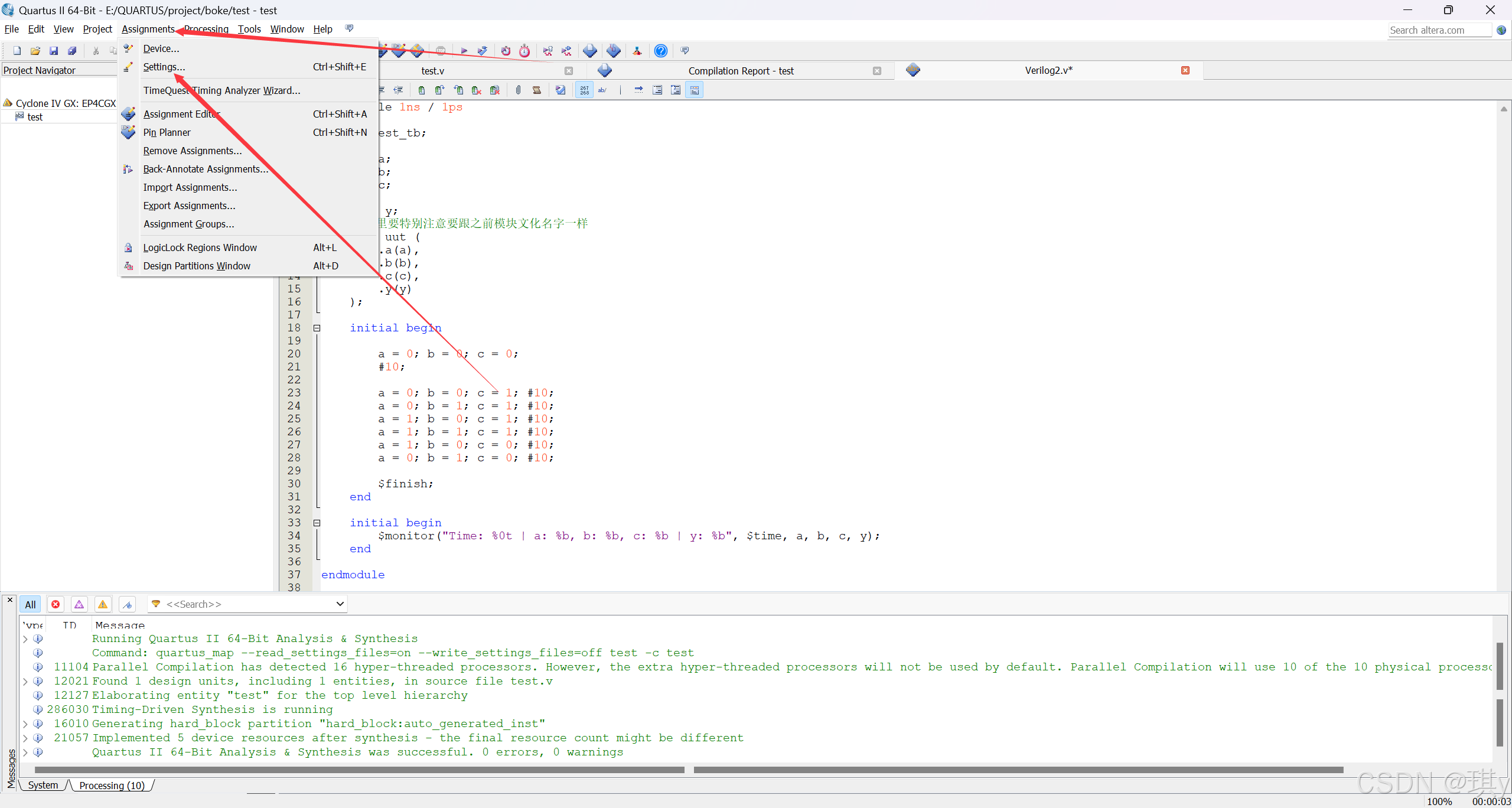

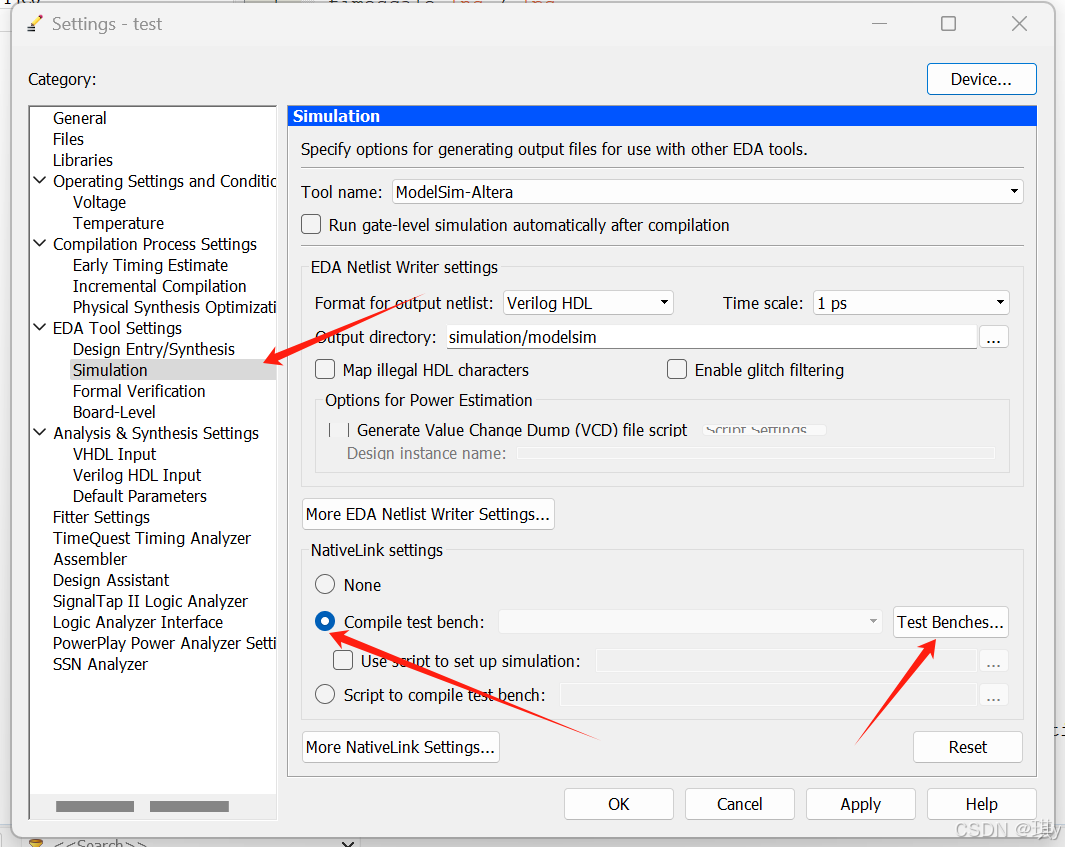

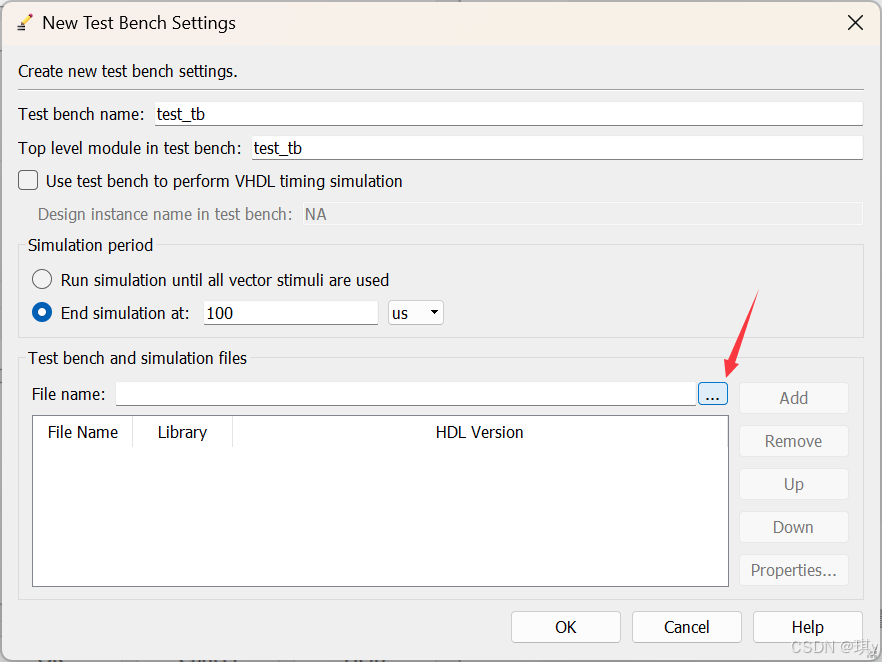

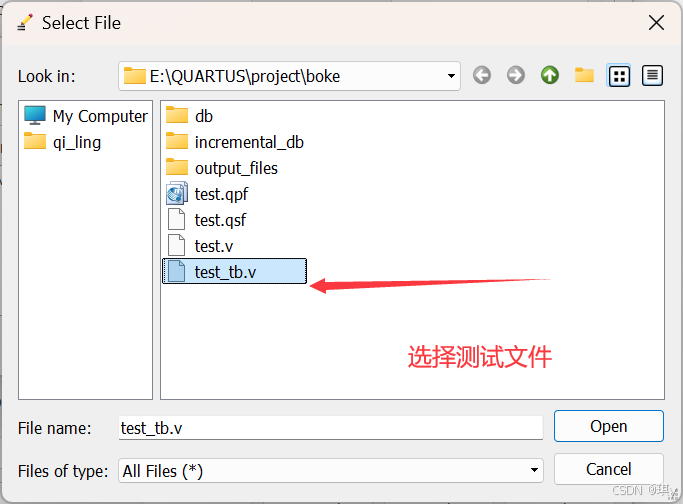

8.点击这里的Setting

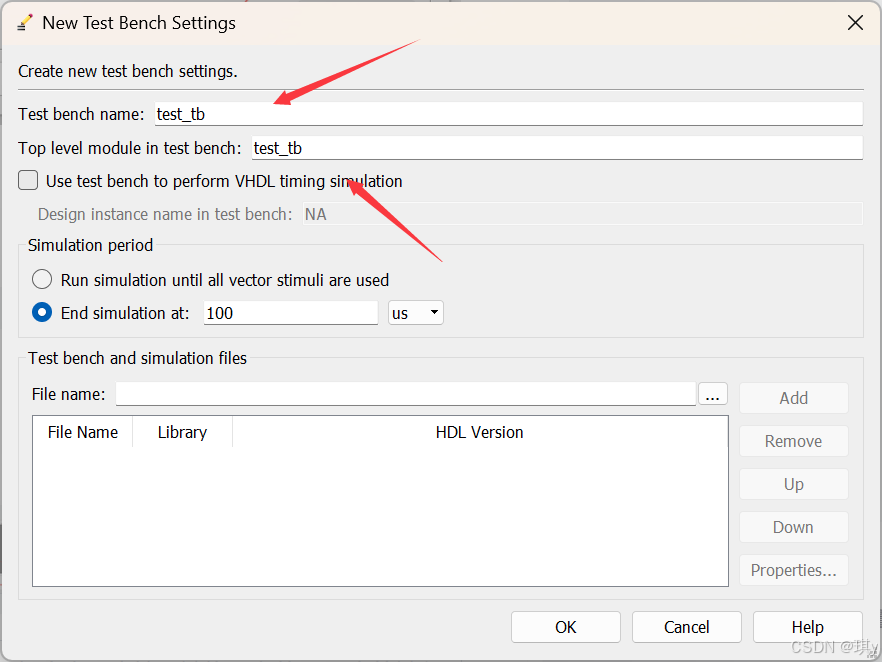

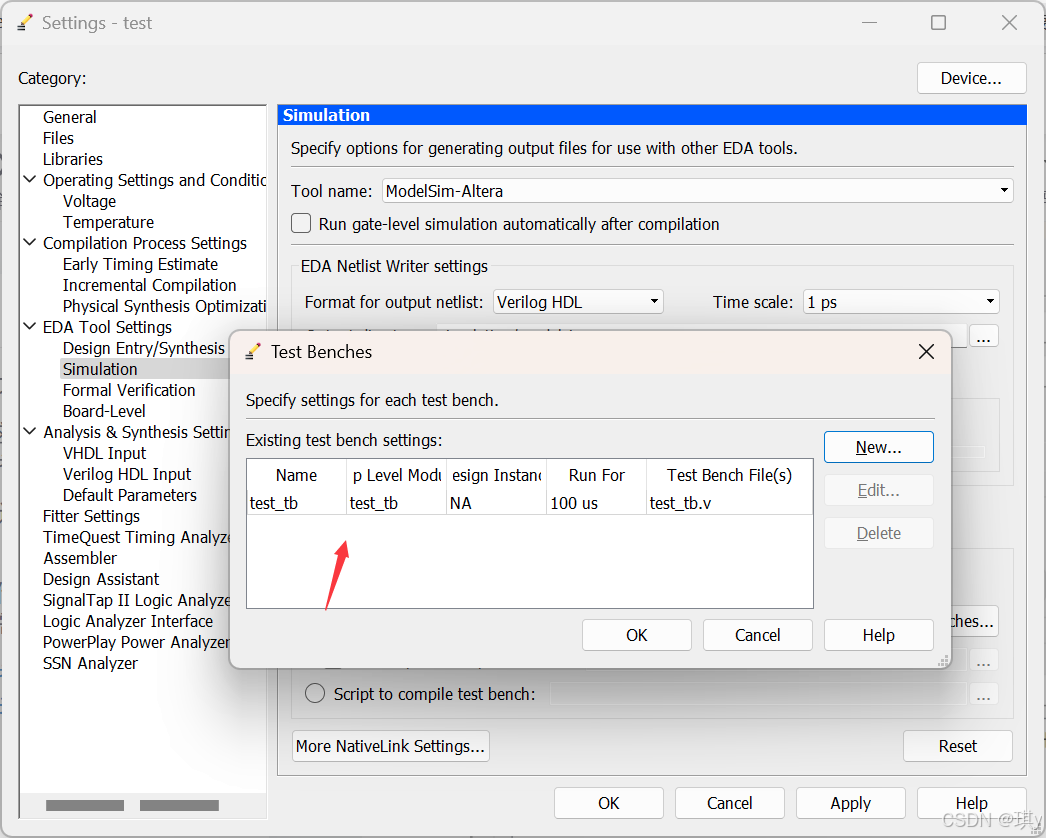

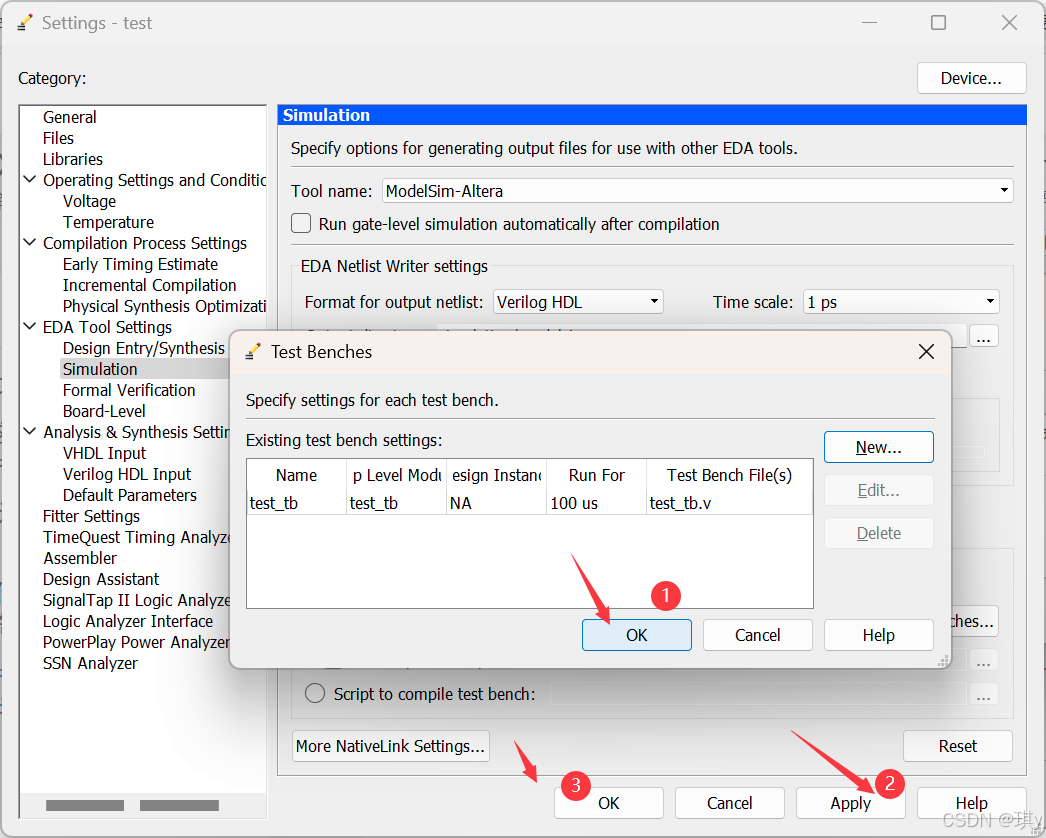

点击Test Bench 进行测试文件的配置,这里要跟测试文件名字保持一致!,再一次提醒文件名字一定要一样!

返回这里发现有添加成功了

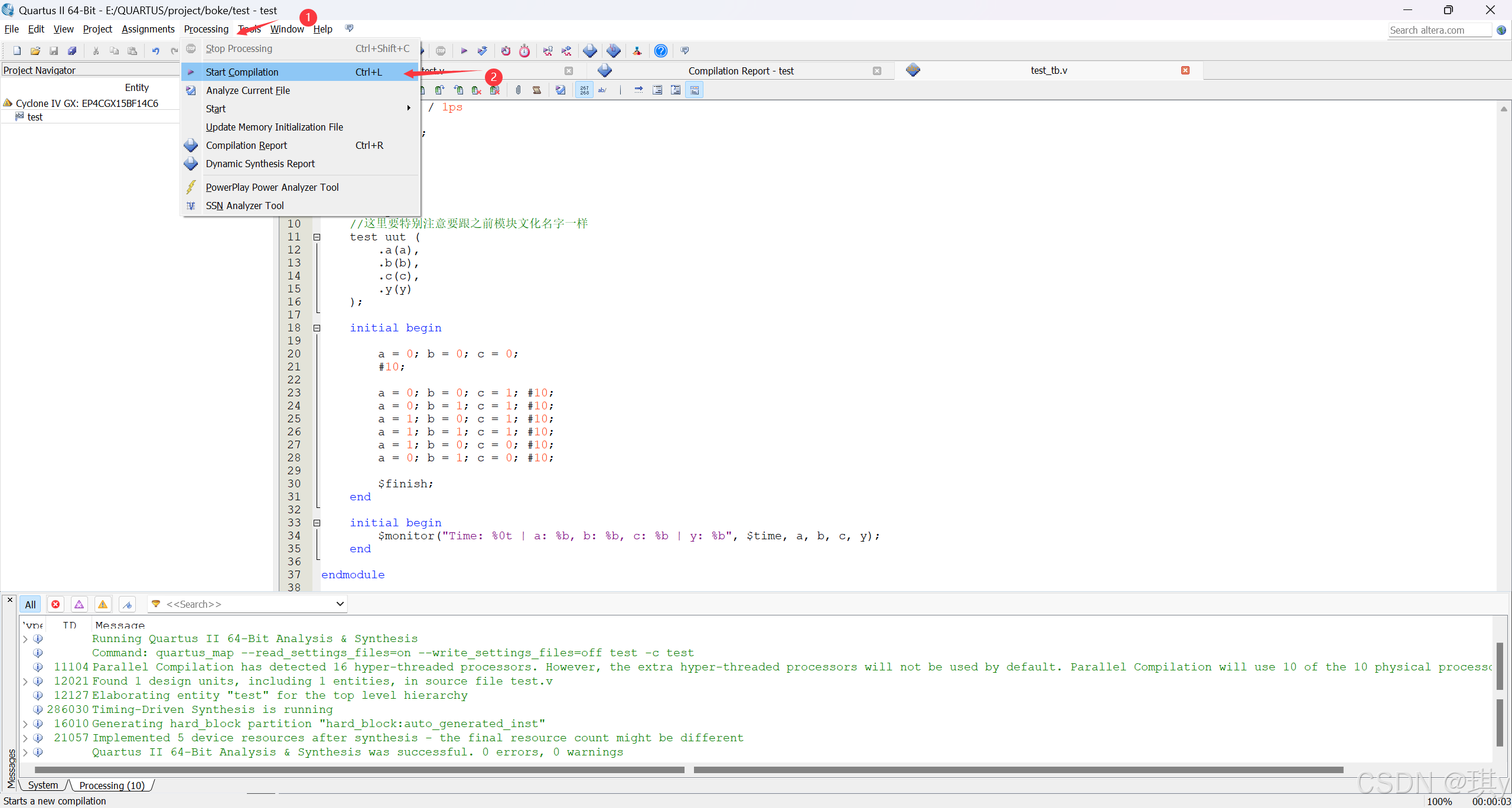

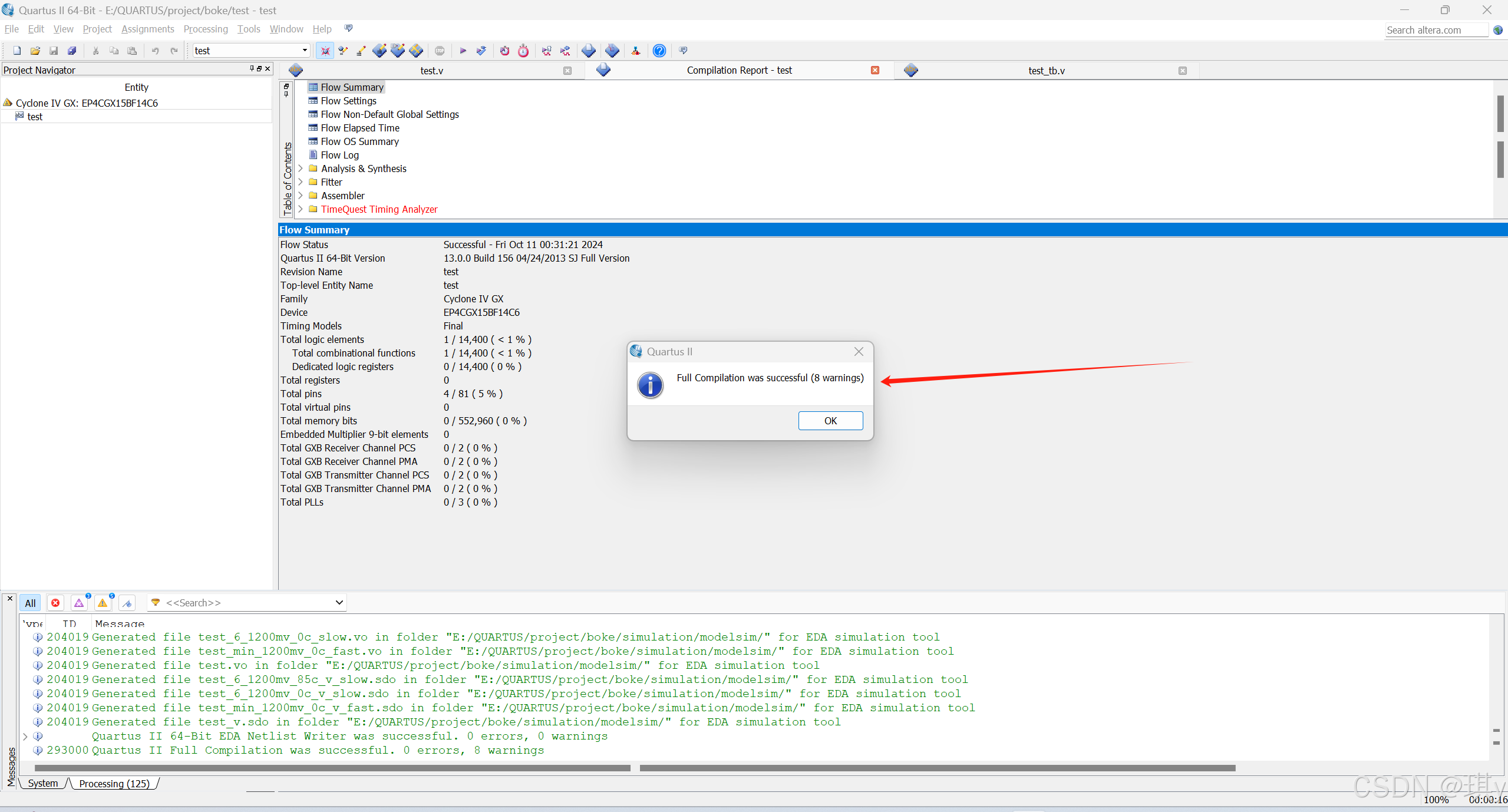

9.接下来我们开始编译运行了 ~等待编译通过

弹出警告来,不管它,只要不是error 就行,到这步不是说就可以正确仿真了,只能说代码语法没用问题!跟大部分软件一样

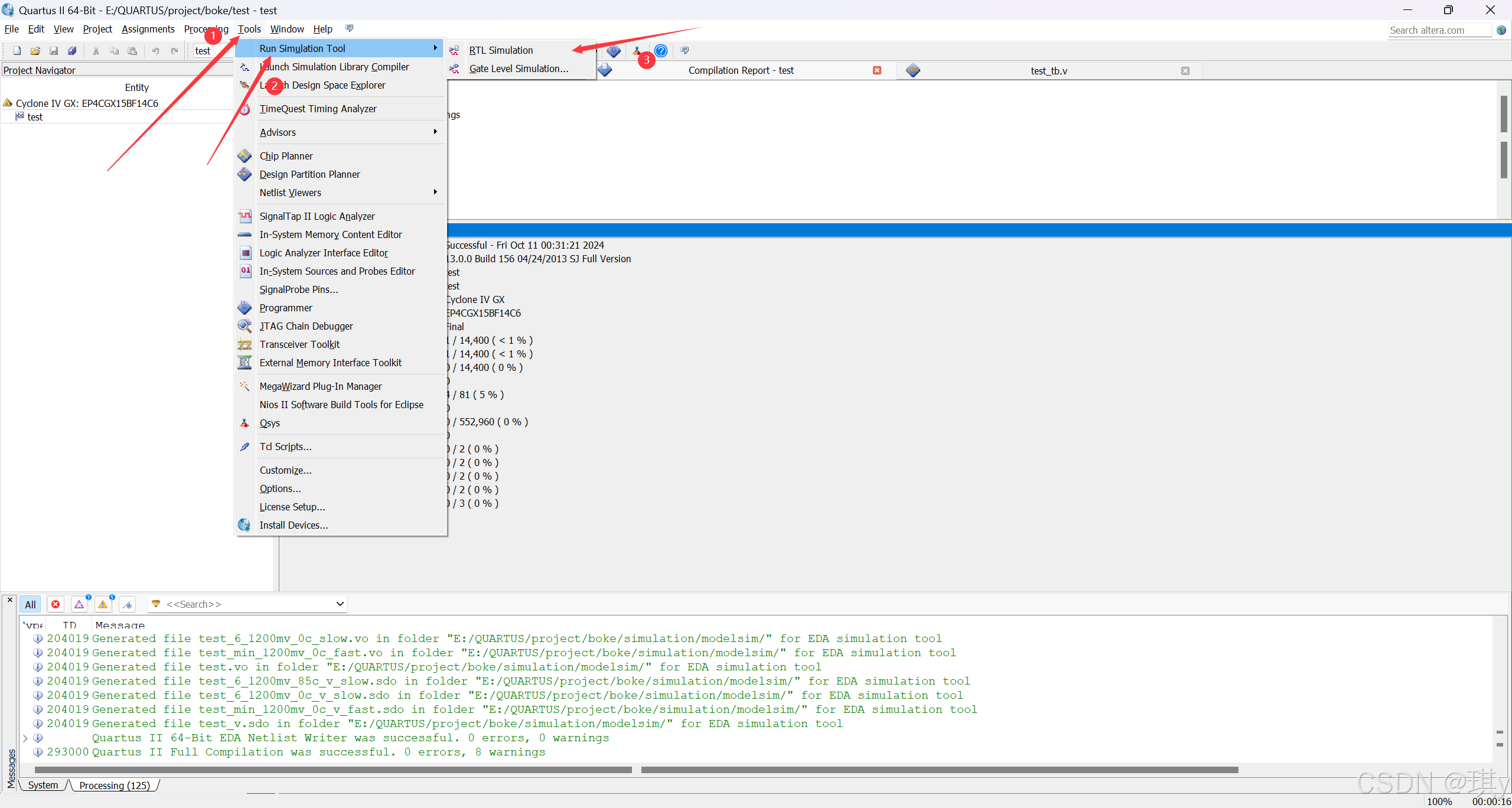

10.我们选择开始打开波形软件它会自动打开modelsim,

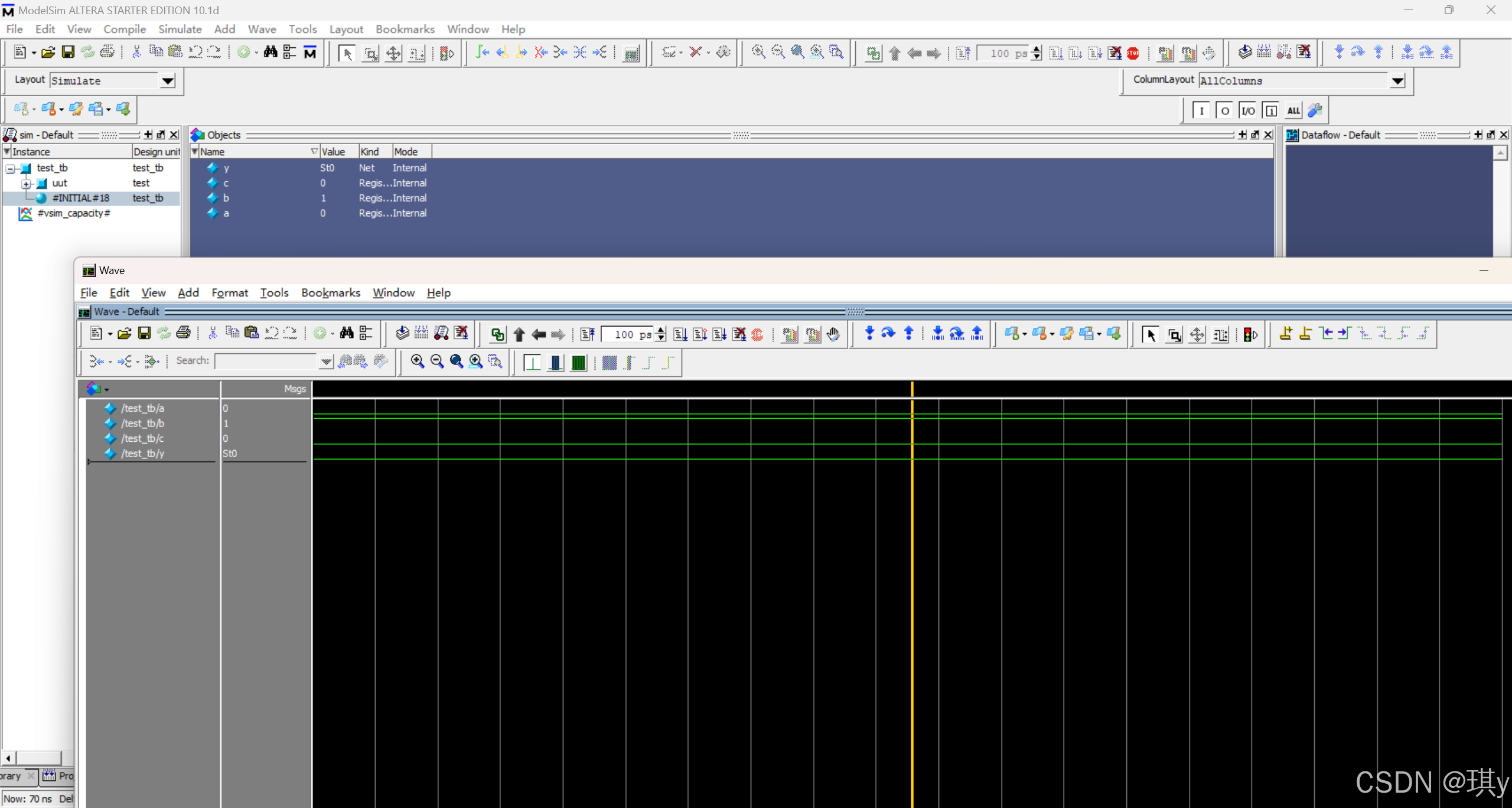

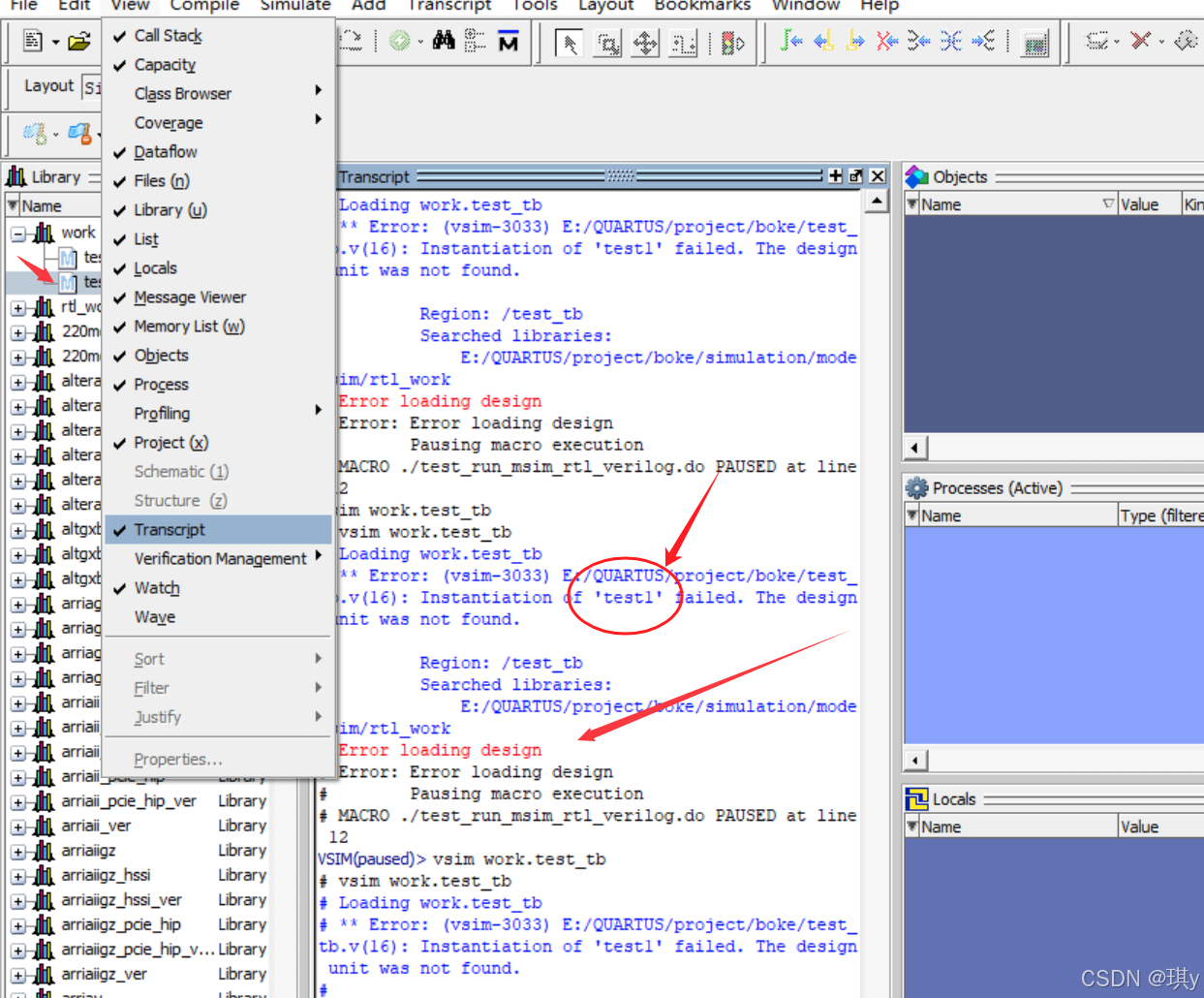

等待一会儿发现是会自动变成如图所示,如果没用波形或者别的,大家一定要看看错误点

例子!我这里模块名字不一致,我再重复刚才的操作,这里只告诉我语法没有错误。但是不代表我能跑出波形

我们双击test_tb的文件,我们会发现弹出一开始说的错误我们看蓝色的字体,其实已经告诉你错误点了。发现没有!

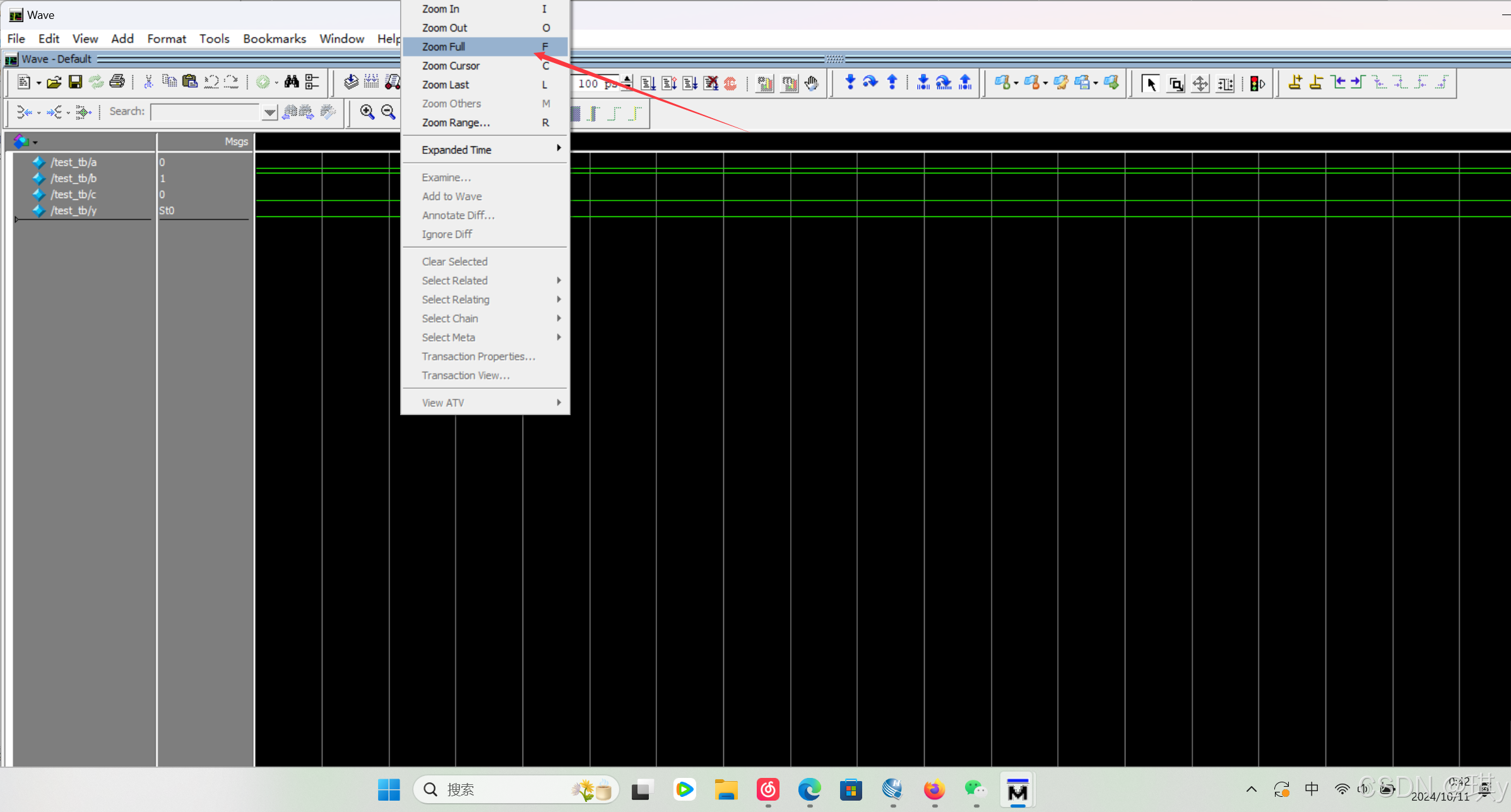

11.回归正题。我们接下 鼠标右键波形黑色地方,选择ZOOM FULL

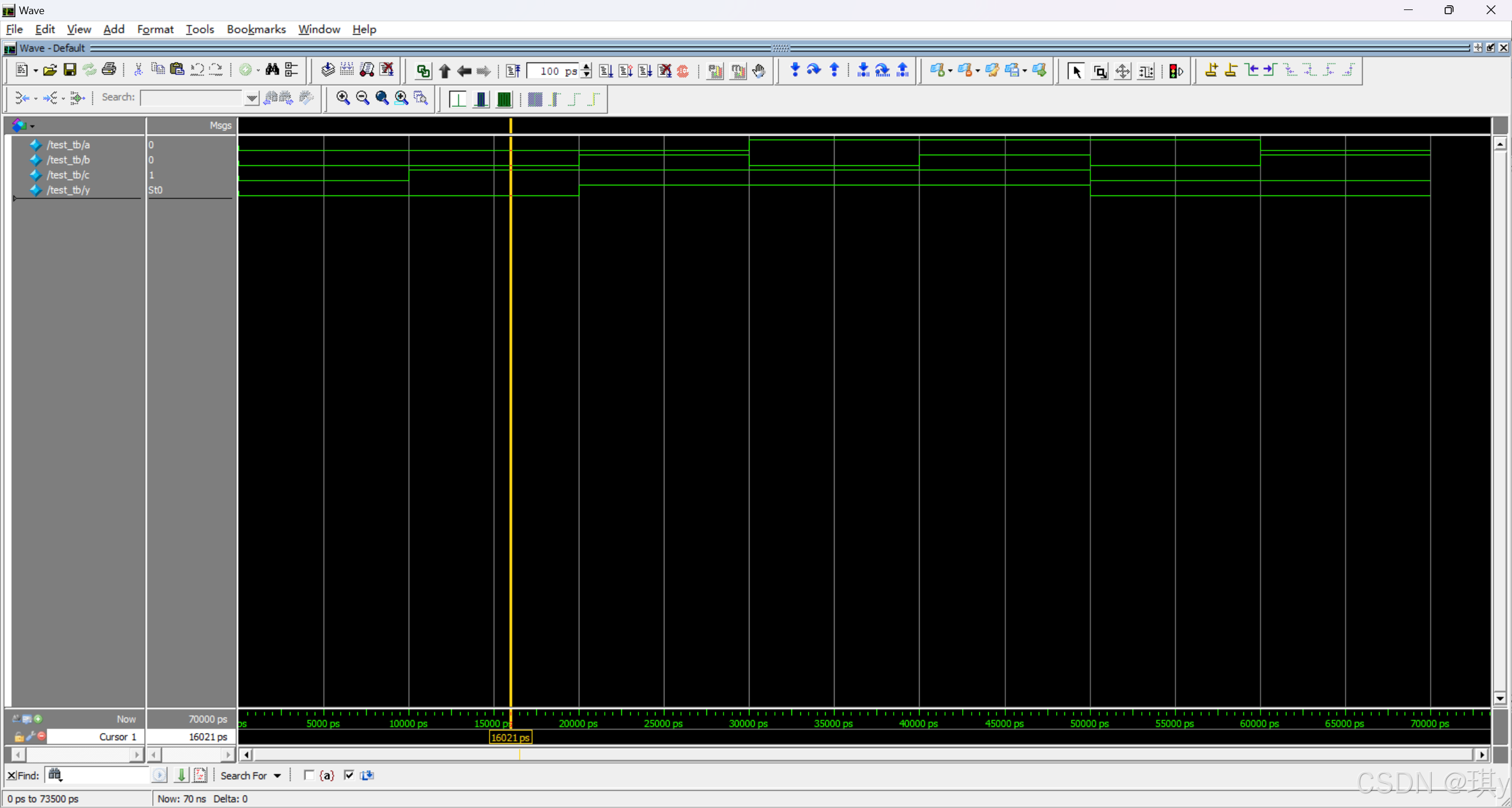

波形就出来了,看高低电平就跟三输入表决器的真值表一样

| 输入A | 输入B | 输入C | 输出OUT |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

在这里特别感谢一位大佬的帖子带来的经验

https://blog.csdn.net/lizao_three/article/details/116944272?spm=1001.2014.3001.5501

4267

4267

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?