本文转载自CSDN博主「孤独的单刀」的原创文章,原文链接:https://blog.csdn.net/wuzhikaidetb/article/details/126266612

1、组合逻辑与时序逻辑

数字电路根据逻辑功能的不同特点,可以分成两大类:组合逻辑电路与时序逻辑电路。

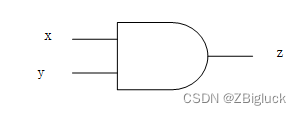

组合逻辑电路 的最大特点是 输出是实时跟随输入变化的 。如下面的组合逻辑,如果两个输入之间到达的路径延时不一致的话,则很容易产生毛刺。偏偏 FPGA 又不是理想器件,在资源被大量使用的情况下,要做到不同的路径达到门电路的延时一致几乎是不可能的,所以可以说纯组合逻辑电路的毛刺现象几乎是不可避免的。毛刺的产生很多时候都是个灾难,因为它并不是你预期设计的一部分,这相当于你的设计遇上了没有预料到的输入情况,所以输出在很大程度上也会变得不可控。

简单的组合逻辑电路

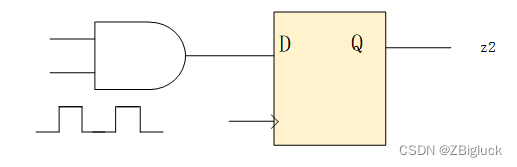

时序逻辑电路 的最大特点是 输出不是实时跟随输入变化的 ,而是在时钟的上升沿(或下降沿,一般以上升沿为主流)统一发生变化(诚然这个变化也不是瞬时的,还需要一定的Tco时间)。在时钟的上升沿之前,只要输入满足建立时间和保持时间的要求,则任你如何有毛刺也不会对输出造成影响,这很容易理解,因为在非上升沿不会发生采样,自然也不会有输出。

简单的时序逻辑电路

时序逻辑电路解决了组合逻辑电路无法解决的毛刺问题,将电路的行动全部置于统一的行动之下 —— 时钟。在时钟信号的控制下,整个电路可以有条不紊的运行。当然,组合逻辑电路并不是被替代,因为我们仍然需要其实现逻辑功能。所以 组合逻辑与时序逻辑可以说是共生,你中有我我中有你 —— 组合逻辑实现逻辑功能,而时序逻辑则将电路的运行置于统一的管理之下。

2、同步电路和异步电路

基于 FPGA 的设计几乎都是时序逻辑电路,极少会有设计纯组合逻辑电路的情况。因此,时序逻辑电路在 FPGA 的设计中占有非常重要的地位。对于时序逻辑,按信号间关系来看,又可分为同步时序逻辑和异步时序逻辑,简称同步逻辑和异步逻辑。

简单来讲,FPGA 设计中寄存器全部使用一个时钟的设计是同步设计电路,FPGA 设计寄存器使用多个时钟的设计是异步设计电路。我们说的所有时序分析都是建立在同步电路的基础上的,异步电路不能做时序分析(或者说只能做伪路径约束)。

异步电路由于使用的时钟不同,导致上游寄存器的输出数据进入下游寄存器的时间是任意的,这非常可能导致不满足下游寄存器的建立时间要求和保持时间要求,从而导致亚稳态。同样的原因,由于两者时钟不同,所以也无法建立对应的模型来分析异步电路是否能满足时序要求。

所以,对 FPGA 的时序分析其实主要就是对同步时序逻辑电路进行分析,然后再做约束。那么到底要约束些什么?

3、建立时间与保持时间

时序逻辑电路的基础是触发器FF,对FF的使用要求就是必须满足建立时间与保持时间。

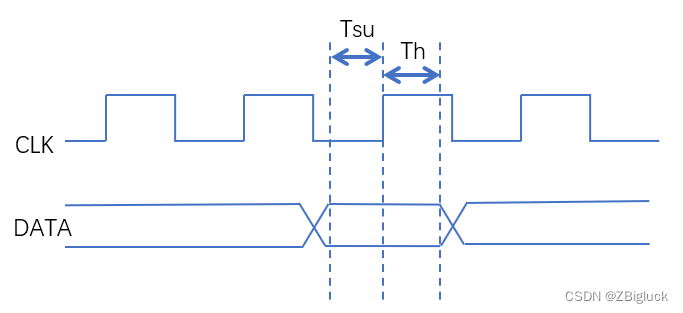

建立时间 Tsu(Setup Time):即在时钟上升沿之前数据必须稳定的最短时间

保持时间 Th(Hold Time):即在时钟上升沿之后数据必须稳定的最短时间

通俗来讲:建立时间和保持时间就是在寄存器采样窗口中输入数据必须保持不变,以免寄存器无法稳定采样。也就是说,在我寄存器的采样窗口之前你输入数据就必须要保持稳定,即输入数据不能来的太晚(建立时间);同样的,你寄存器的输入数据也必须在我寄存器的采样窗口结束后才变化,在此之前必须保持问题,即输入数据不能走的太早(保持时间)。

建立时间和保持时间的示意图如下:

建立时间和保持时间是触发器的固定属性,也就是说同一 FPGA 型号其所有的 FF 的建立时间和保持时间都是相同的,而不同的 FPGA 型号之间,其建立时间与保持时间则不同。关于 FPGA 对应的建立时间和保持时间可以通过手册来查询,也可以用 vivado 做时序分析时查询。高级的 FPGA 芯片其建立时间和保持时间会比低级的 FPGA 芯片较小,这也是其能运行频率更高的原因。

了解 FPGA 的建立时间和保持时间非常重要,它是我们进行时序分析的基础,甚至可以说,时序分析就是要分析所有的 FF 是不是都满足建立时间与保持时间的要求。如果建立时间或者保持时间的要求无法被满足,那么就会发生亚稳态现象。

亚稳态 (Metastability):如果数据传输中不满足触发器的Tsu和Th,就可能产生亚稳态。此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。这段时间称为 决断时间Tmet(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。

4、恢复时间与去除时间

恢复时间(Recovery Time)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,如果保证不了这个最小恢复时间,也就是说这个异步控制信号的解除与“下个时钟沿”离得太近(但在这个时钟沿之前),没有给寄存器留有足够时间来恢复至正常状态,那么就不能保证“下个时钟沿”能正常作用,也就是说这个“时钟沿”可能会失效。

去除时间(Removal)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近(但在这个时钟沿之后),那么就不能保证有效地屏蔽这个“时钟沿”,也就是说这个“时钟沿”可能会起作用。

换句话来说,如果你想让某个时钟沿起作用,那么你就应该在“恢复时间”之前是异步控制信号变无效,如果你想让某个时钟沿不起作用,那么你就应该在“去除时间”过后使控制信号变无效。如果你的控制信号在这两种情况之间,那么就没法确定时钟沿是否起作用或不起作用了,也就是说可能会造成寄存器处于不确定的状态。而这些情况是应该避免的。所以恢复时间和去除时间是应该遵守的。

比如下图中:复位信号 rst_n 作为一个异步控制型号,需要在下一个时钟有效沿之前就变无效(拉高),以保证 Recovery 恢复时间,这样寄存器才有足够的时间恢复到正常状态(这有点类似建立时间);同样的,复位信号 rst_n 的移除不能与上一个时钟有效沿间隔太近,以保证其无法影响上一个时钟有效沿(这有点类似保持时间)。

5、4种基本的时序路径

下图是一张典型的 FPGA 与上游、下游器件通信的示意图。

其可以划分为基本的四条数据路径,这四条路径也是需要进行时序约束的最基本的路径:

路径1,上游器件通过 FPGA 管脚到 FPGA 的寄存器的时序路径,即 pin2reg (管脚到寄存器),需要对其进行约束,以满足 FPGA 端寄存器的建立时间和保持时间要求;

路径2,FPGA 内部的寄存器到另一个寄存器, 即 reg2reg(寄存器到寄存器),需要对其进行约束,以满足 FPGA 端寄存器的建立时间和保持时间要求;

路径3,FPGA 管脚到下游器件的寄存器的时序路径,即 reg2pin(寄存器到管脚),需要对其进行约束,以满足下游器件的寄存器的建立时间和保持时间要求;

路径4,FPGA 管脚到 FPGA 管脚的时序路径(不通过任何寄存器),其本质上是纯组合逻辑电路,仅仅需要约束其值在一个指定范围,不需要满足建立时间和保持时间要求。

11万+

11万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?