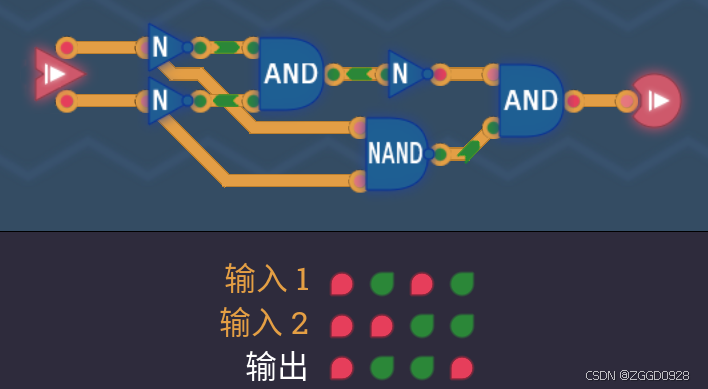

异或门

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个输出端,多输入异或门可由两输入异或门构成。若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。即如果两个输入不同,则异或门输出高电平1。

异或门电路

-------------------------------------

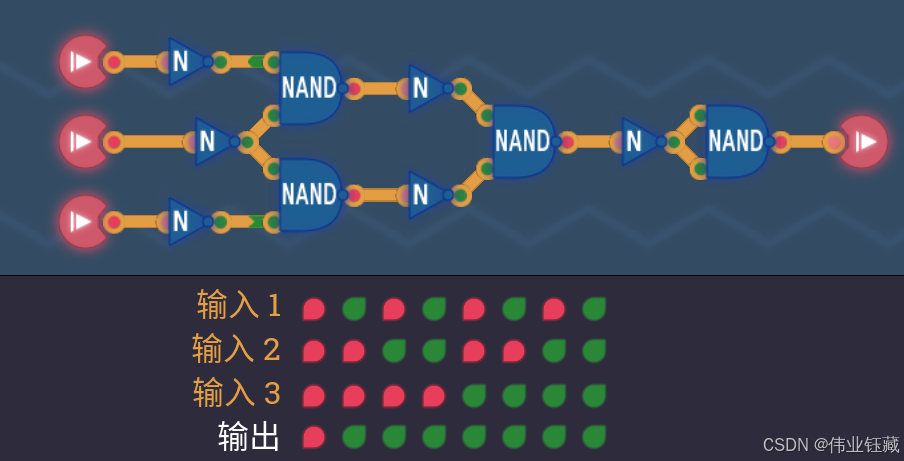

同或门

同或门(英语:XNOR gate或equivalence gate)也称为异或非门,在异或门的输出端再加上一个非门就构成了异或非门,是数字逻辑电路的基本单元,有2个输入端、1个输出端。当2个输入端中有且只有一个是低电平(逻辑0)时,输出为低电平。亦即当输入电平相同时,输出为高电平(逻辑1)。 [1]

同或门电路

-------------------------------------

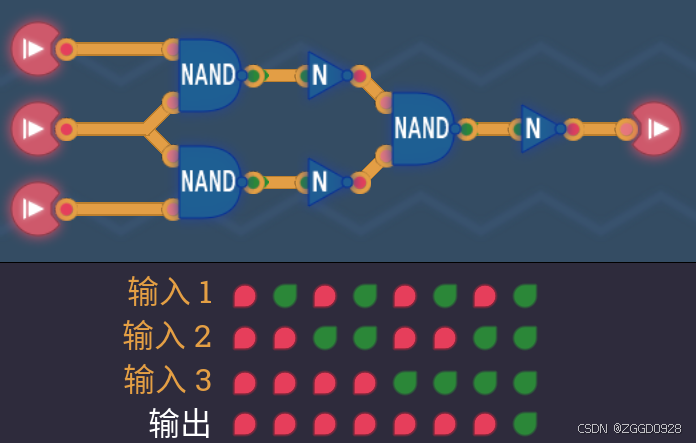

三路(多路)或门

三路(多路)或门是或门的延申版,或门逻辑详解在或与非文章写过这里就不过多赘述了。

三路(多路)或门电路

-------------------------------------

三路(多路)与门

三路(多路)与门是与门的延申版,与门逻辑详解在或与非文章写过这里就不过多赘述了。

三路(多路)与门电路

-------------------------------------

2575

2575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?