Xilinx Zynq UltraScale+ RFSoC 47DR系列板卡凭借其独特的单芯片集成架构和灵活的可扩展性,在无线通信、雷达、电子对抗等领域展现了显著优势。以下从硬件设计、性能参数、开发支持及应用场景四方面展开分析。

一、硬件集成与架构创新

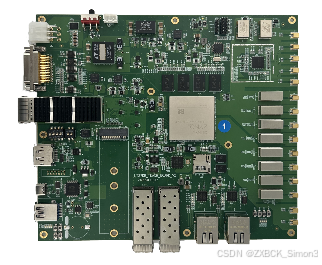

1. 射频-数字一体化设计

RFSoC 47DR板卡采用单芯片集成方案,将8通道14位ADC(最高5GSPS)与8通道14位DAC(最高9.85GSPS)直接嵌入FPGA,同时集成ARM Cortex-A53处理器和UltraScale+可编程逻辑单元。相比传统分立式架构(CPU+FPGA+ADC/DAC),其功耗降低约30%,尺寸缩减50%以上,尤其适合机载、便携式设备等空间受限场景^[1][5][9]^。

-对比竞品:Intel Stratix 10 MX系列需外接射频模块,而RFSoC 47DR的射频前端与逻辑单元深度融合,减少了信号链延迟,提升实时性^[1]^。

2. 多通道同步与扩展能力

板卡支持外部Sync同步信号和Refclk参考时钟输入,可实现多板卡同步采样或输出(如16通道A/D与D/A扩展),误差控制在皮秒级,适用于大规模MIMO系统与相控阵雷达^[7][12]^。例如,西安正弦波测控的多块47DR板卡同步实现多通道5GSPS数据采集,满足24~64多通道扩展需求。

二、射频性能与接口优势

1. 宽频段与高采样率

射频范围:接收频率覆盖1MHz~6GHz,支持C波段以下通信与雷达信号处理,发送频率最高达6GHz。

采样能力:单通道模式下ADC采样率5GSPS,正交模式(4通道)提升至9.85GSPS;DAC采样率可达9.8GSPS,支持超宽带信号生成(如5G毫米波频段)^[2][15]^。

2. **高速数据传输与存储**

接口带宽:通过PCIe 3.0接口(8通道)或100Gbps光纤接口,支持48Gbps数据传输速率,满足实时流数据处理需求^[7][9]^。

存储扩展:板载56Gb DDR4内存,可选配NVMe SSD或EMMC存储(最高128GB),适用于长时间高速数据记录与回放。

三、开发便利性与生态支持

1. 软硬件协同开发工具链

开发环境:提供完整的Vivado/Vitis工具链,支持Python、C++及MATLAB编程,并开源信号处理算法库(如DDC/DUC、波束成形)。

2. 灵活配置与调试支持

启动模式:支持Micro-SD卡、QSPI Flash或JTAG动态加载,适应不同开发阶段需求。

调试接口:集成RS232、USB 3.0及千兆以太网接口,便于实时监控与远程控制。

四、行业应用与场景适配

1. 通信与雷达系统

5G基站:利用8T8R架构实现Massive MIMO波束成形,支持Sub-6GHz频段基站部署^。

电子对抗:通过动态重配置能力,快速切换通信干扰与信号侦察模式,响应时间低于10μs。

2. 高精度测试与医疗设备

医学成像:14位高精度ADC支持超声雷达信号采集,分辨率达0.1mm级。

工业检测:多通道同步采样可用于高速生产线上的缺陷检测,采样误差率低于0.01。

3.推荐低成本型号介绍:

ZXB-47DR-4T4R数字阵列板卡,采用XCZU47DR作为主控制器,以适配不同教学资源需求;实现4收4发的信号发射、采集和控制,并根据需求搭建外围高速接口,实现平台的数据处理及运算能力。支持4收4发; 支持DC-6GHz射频直采; 支持高速数据流盘,1路100G光口,2路10G光口; 支持板间级联。成本低,xiao'lv作为入门级的不二选择。

总结

RFSoC 47DR板卡通过射频-数字一体化架构、多通道同步扩展及软硬件协同优化,解决了传统方案中功耗高、延迟大、开发周期长的痛点。其核心优势体现在:

性能突破:单芯片集成8路高速ADC/DAC,支持6GHz以下宽频段与超高采样率;

生态完备:从硬件设计到算法库的全栈支持,降低开发门槛;

场景普适:覆盖通信、雷达、医疗等高频宽、高实时性领域。

9590

9590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?