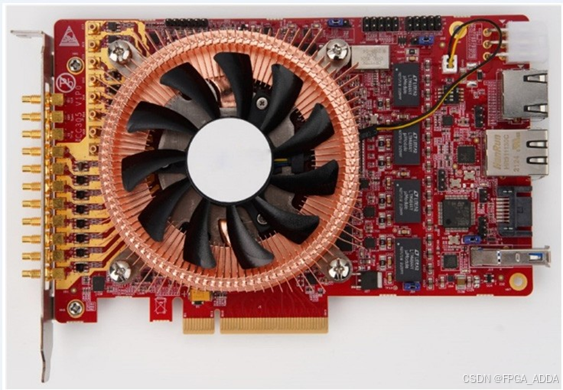

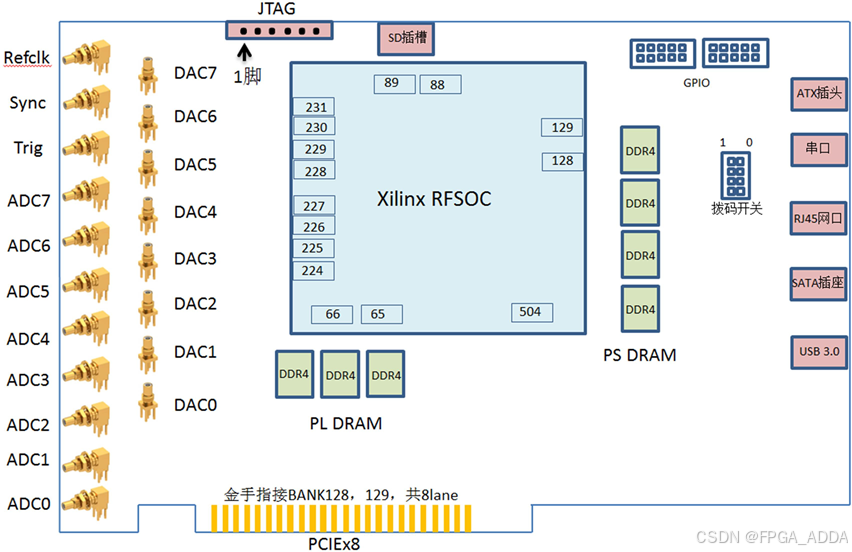

8通道ADC + 8通道DAC PCIe数据处理卡

- 基于 Xilinx RFSOC ZU27DR 或 ZU47DR

- 8 通道 ADC 采样

- 8 通道 DAC

- PCI Express x8 GEN3 Interface

- 4 核ARM Cortex-A53 处理器,主频最高 1.3G

- 板载 7GB DDR4 SDRAM 缓存,最高支持 2400MT

- 板载 x2 512Mb QSPI 配置 Flash

- X1 10/100/1000Mbps 以太网(RJ45)接口

- X1 Micro SD 卡

- X1 SATA 接口

- X1 USB2.0/USB3.0 接口

- X1 UART RS232 调试串口

- X15 GPIO 接口,支持 3.3V 和 5V 可选

- 支持外参考时钟输入

- 支持外部触发信号输入

该板卡基于 Xilinx 公司 RFSOC 系列芯片,最大提供 8 个 9.8GSPS 14 位 DAC 输出通道与 8 个5GSPS 14 位ADC 输入通道。板卡支持外部 Sync 同步信号输入

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

603

603

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?