一、计数器的特点和分类

1、计数器的功能及应用

(1)功能:对时钟脉冲CP计数。

(2)应用:分频、定时、产生节拍脉冲和脉冲序列、进行数字运算等。

2、计数器的特点

(1)一般地说,这种计数器除了输入计数脉冲CP信号之外,很少有另外的输入信号,其输出通常也是现态的函数,是一种Moore型的时序电路,而输入计数脉冲CP是当作触发器的时钟信号对待的。

(2)从电路组成看,其主要组成单元是时钟触发器。

3、计数器的分类

(1)按数的进制分:

①二进制计数器:当输入计数脉冲到来时,按二进制数规律进行计数的电路都叫做二进制计数器。

②十进制计数器:当输入计数脉冲到来时,按十进制数规律进行计数的电路都叫做十进制计数器。

③N进制计数器:除了二进制和十进制计数器之外的其它进制的计数器都叫做N进制计数器。

(2)按计数时是递增还是递减分:

①加法计数器:当输入计数脉冲到来时,按递增规律进行计数的电路叫做加法计数器。

②减法计数器:当输入计数脉冲到来时,进行递减计数的电路称为减法计数器。

③可逆计数器:在加减信号的控制下,既可进行递增计数,也可进行递减计数的电路叫可逆计数器。

(3)按计数器中触发器翻转是否同步分:

①同步计数器:当输入计数脉冲到来时,要更新状态的触发器都是同时翻转的计数器叫做同步计数器,计数器中各个时钟触发器的时钟信号都是输入计数脉冲。

②异步计数器:当输入计数脉冲到来时,要更新状态的触发器,有的先翻转,有的后翻转,是异步进行的,这种计数器叫做异步计数器,计数器中各个触发器的时钟不完全相同。

(4)按计数器中使用的开关元件分:

①TTL计数器。

②CMOS计数器。

4、计数器级数长度、进制或模的概念

(1)人们常把一个具体的计数器能够记忆输入脉冲的数目叫做计数器的计数长度、进制或模。

(2)所谓计数器的长度、进制或模,就是电路的有效状态数(也就是说,电路的当前有效状态代表了计数器的当前计数值)。

(3)当计数器的计数值超过计数器的长度时,计数器将产生进位或者借位信号,然后重新开始新一轮的计数。

二、二进制同步计数器

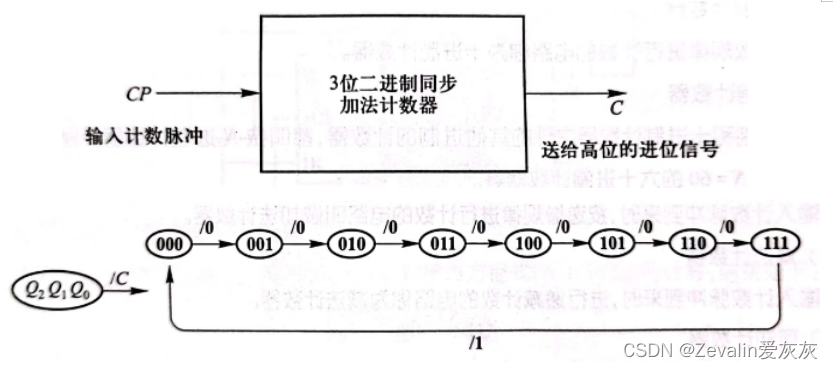

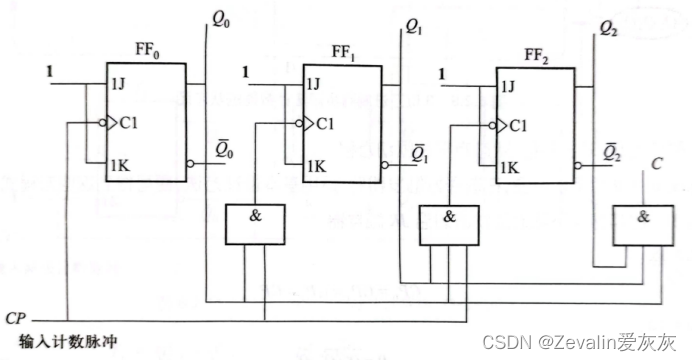

1、3位二进制同步加法计数器

(1)结构示意框图与状态转换图:

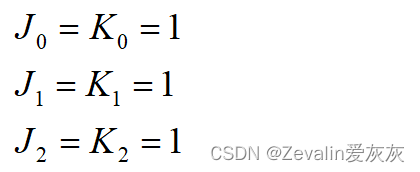

(2)选择触发器,求时钟方程、输出方程和状态方程:

①由于JK触发器功能齐全、使用灵活,故选用3个时钟下降沿触发的边沿JK触发器。

②由于要求构成的是同步计数器,显然各个触发器的时钟信号都应使用输入计数脉冲CP,即。

③由上图所示的状态转换图可直接得到输出方程。

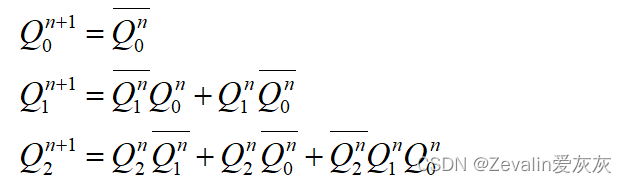

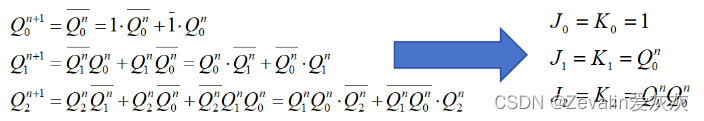

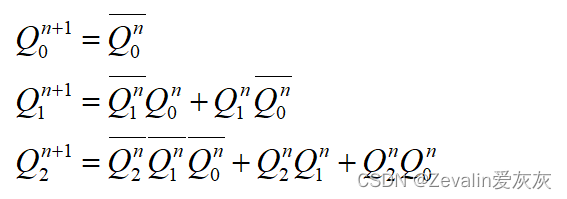

④根据状态转换图可画出各个触发器次态的卡诺图(前面已经有示例,这里不再赘述),根据卡诺图可求得状态方程:

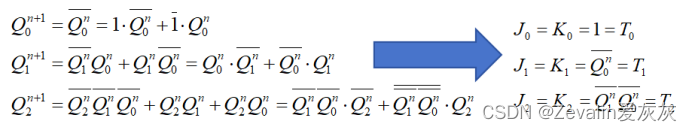

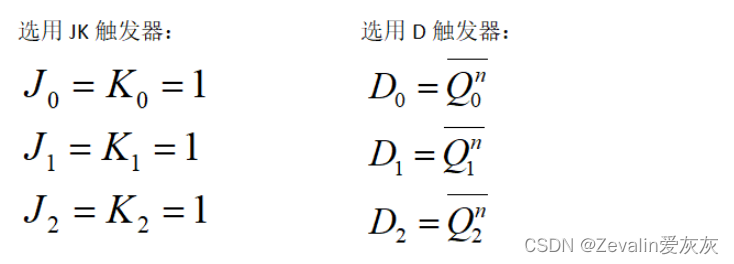

(3)根据JK触发器特性方程的格式变换状态方程式,求出驱动方程。

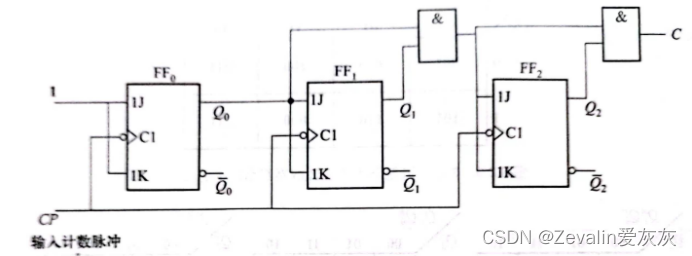

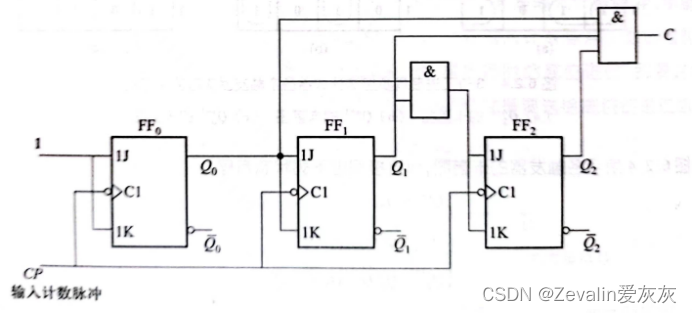

(4)画逻辑电路图:

①串行进位方式:产生进位信号的时间较长,需要从低位到高位逐级传送,但是只要用2输入端与门即可,且各个触发器Q端所带的负载是均匀的。

②并行进位方式:产生进位信号的时间较短,不需要逐级传送,但是随着计数器级数的增加,所用与门的输入端数也随之增加,而且各个触发器所带的负载是不均匀的,越是低位带的负载越重。

(5)二进制同步加法计数器级间连接规律:

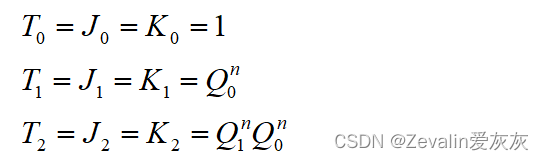

逻辑图中的JK触发器都已经替换成T触发器,那么上述的驱动方程可改为

由此可得

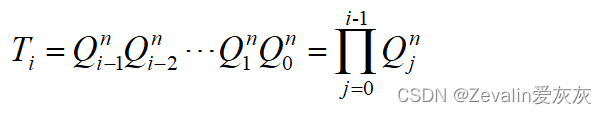

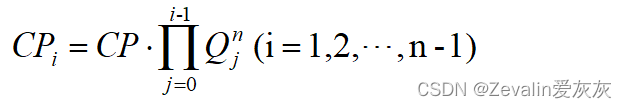

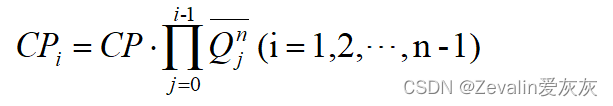

(6)如果把上图中的触发器换成T’触发器,把上式归入

的时钟条件,即将

的时钟方程改变成为

那么就可方便地用T’触发器构成n位二进制加法计数器,不过在这种情况下,严格地讲系统已不是真正的同步时序电路了。

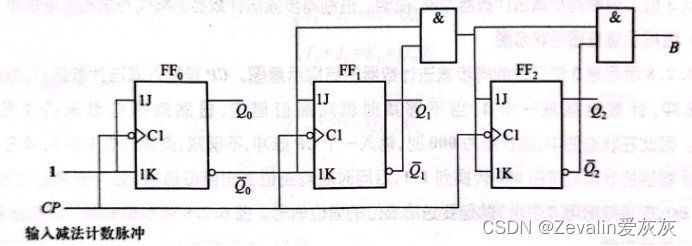

2、3位二进制同步减法计数器

(1)结构示意框图与状态转换图:

(2)选择触发器,求时钟方程、输出方程和状态方程:

①由于JK触发器功能齐全、使用灵活,故选用3个时钟下降沿触发的边沿JK触发器。

②由于要求构成的是同步计数器,显然各个触发器的时钟信号都应使用输入计数脉冲CP,即。

③由上图所示的状态转换图可直接得到输出方程。

④根据状态转换图可画出各个触发器次态的卡诺图(前面已经有示例,这里不再赘述),根据卡诺图可求得状态方程:

(3)根据JK触发器特性方程的格式变换状态方程式,求出驱动方程。

(4)画逻辑电路图(用T型触发器):

①串行借位方式:产生借位信号的时间较长,需要从低位到高位逐级传送,但是只要用2输入端与门即可,且各个触发器Q端所带的负载是均匀的。

②并行借位方式:产生借位信号的时间较短,不需要逐级传送,但是随着计数器级数的增加,所用与门的输入端数也随之增加,而且各个触发器所带的负载是不均匀的,越是低位带的负载越重。

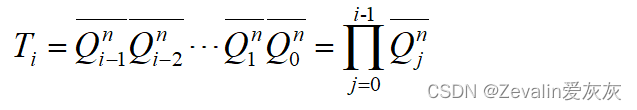

(5)二进制同步减法计数器级间连接规律:

逻辑图中的JK触发器都已经替换成T触发器,驱动方程为

由此可得

(6)如果把上图中的触发器换成T’触发器,把上式归入

的时钟条件,即将

的时钟方程改变成为

那么就可方便地用T’触发器构成n位二进制减法计数器,不过在这种情况下,严格地讲系统已不是真正的同步时序电路了。(图略)

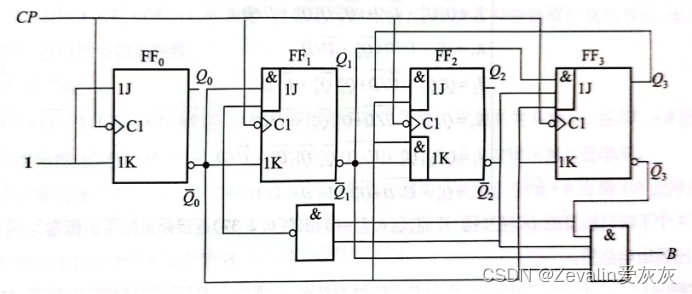

3、二进制同步可逆计数器

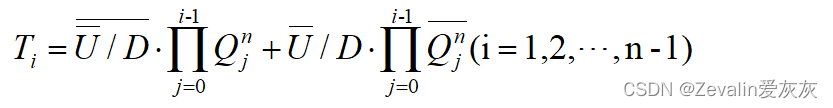

(1)在加减控制信号的管理下,把二进制同步加法计数器和减法计数器组合起来便可获得二进制同步可逆计数器。

(2)单时钟输入二进制同步可逆计数器:

①若用表示加减控制信号,且为0时进行加计数,为1时做减计数,则只需按下式把T触发器级联起来,所得到的便是单时钟输入的二进制同步可逆计数器。

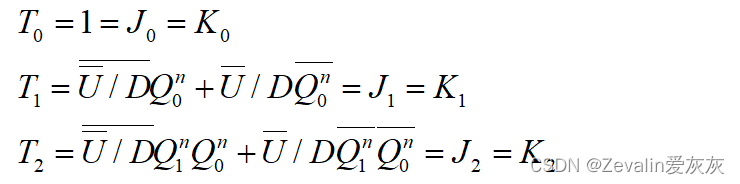

②对于3位二进制同步可逆计数器,有驱动方程

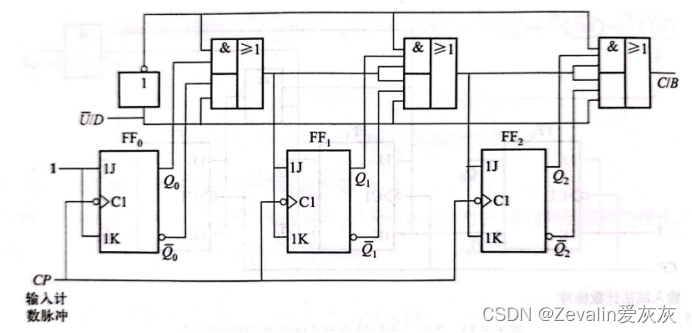

③单时钟输入的3位二进制同步可逆计数器的逻辑电路图:

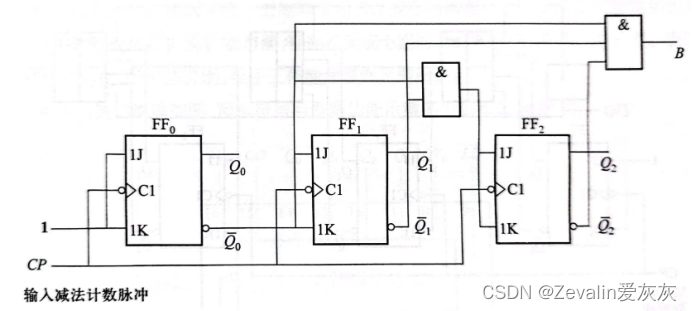

(3)双时钟输入二进制同步可逆计数器:

①如果用表示加计数脉冲、

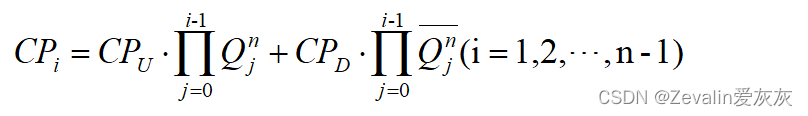

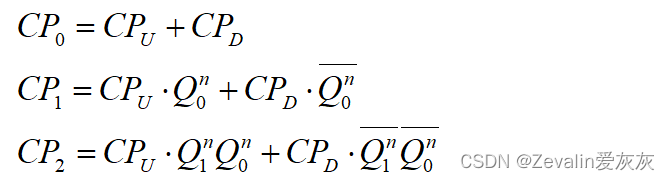

表示减计数脉冲,则只需按下式把T’触发器级联起来,所得到的便是双时钟输入的二进制同步可逆计数器。

②对于3位二进制同步可逆计数器,有时钟方程

③双时钟输入的3位二进制同步可逆计数器的逻辑电路图:

4、集成二进制同步计数器

(1)常用的集成二进制同步计数器有加法计数和可逆计数两种类型,它们采用的都是自然加权二进制码。

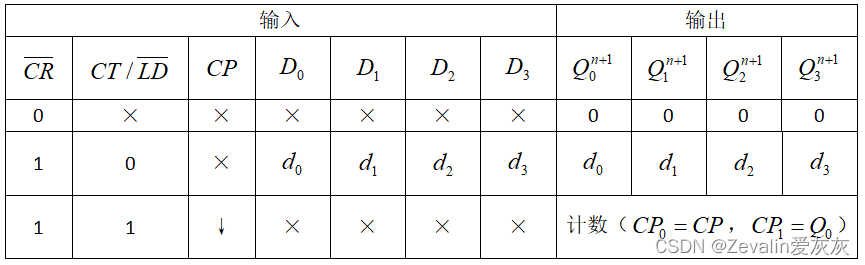

(2)集成4位二进制同步加法计数器:

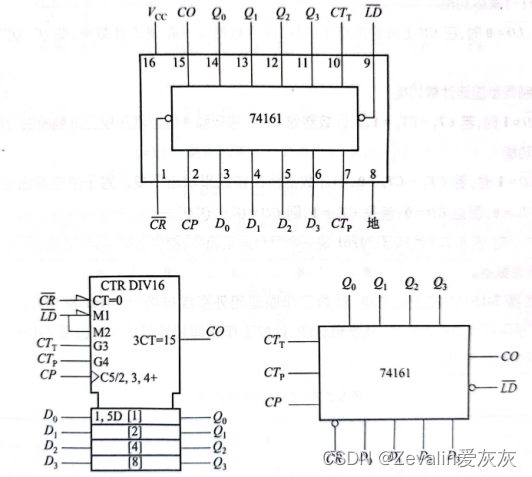

①74161的引出端功能排列图、逻辑符号与逻辑功能示意图:

②在74161中,是输入计数脉冲,也就是加到各个触发器的时钟信号端的时钟脉冲,

是清零端,

是置数控制端,

、

是两个计数器工作状态控制端(只要有一个输入为0,计数器将停止计数,保持现有状态),

是并行输入数据端,

是进位信号输出端,

是计数器状态(也就是当前计数值)输出端。

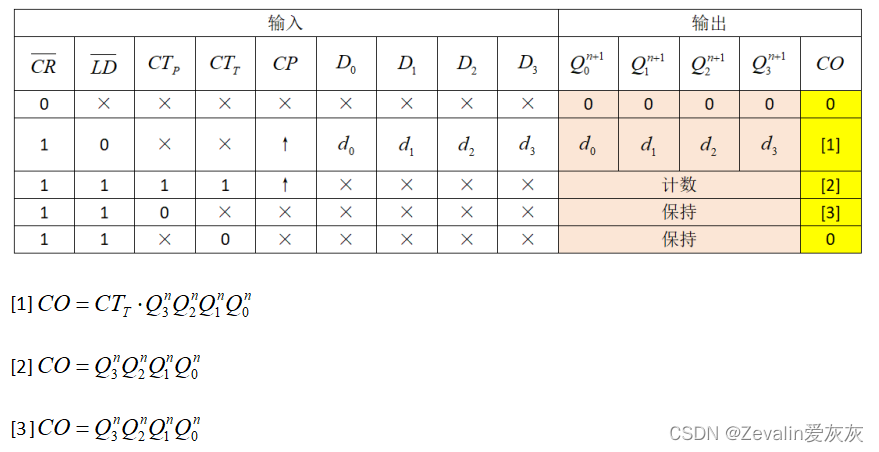

③74161的状态表:

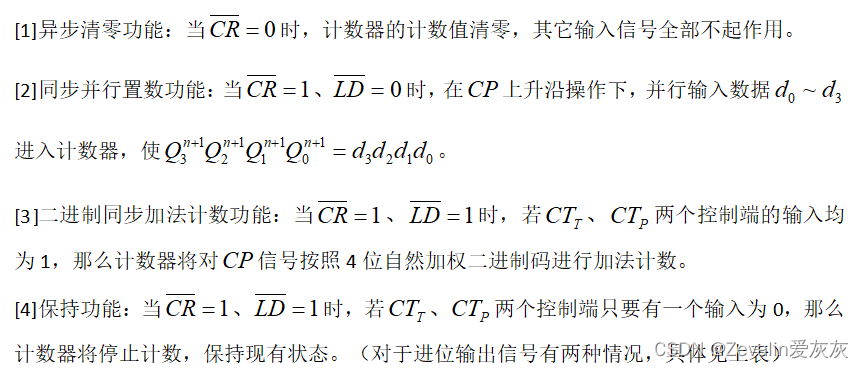

④74161功能详解:

⑤集成计数器74LS161的逻辑功能、计数工作原理和外引线排列都与74161相同,而74163和74LS163除了采用同步清零方式外,其逻辑功能、计数工作原理和外引线排列也与74161没有区别。74163的状态表如下:

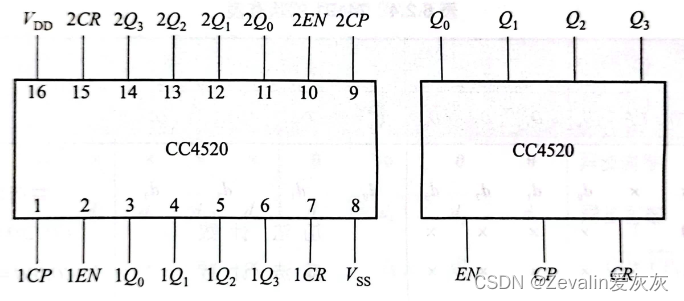

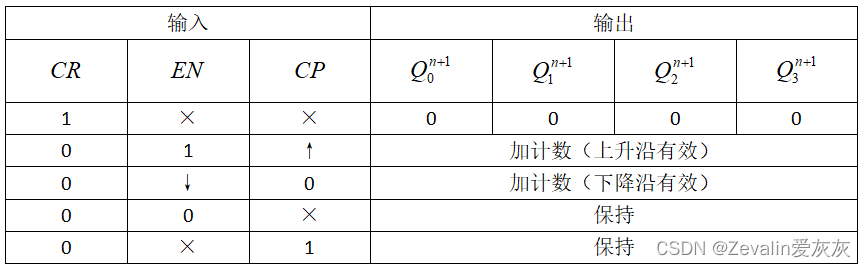

⑥CC4520是双4位二进制同步加法计数器,属于CMOS集成电路,它的引出端排列图、逻辑功能示意图和状态表如下所示。是清零端;

既是使能端,也可以作为计数脉冲输入端;

既是计数脉冲输入端,也可作为使能端;CC4520是具有异步清零,既可上升沿触发,也能下降沿有效的双4位二进制同步加法计数器。(CMOS电路中有4位二进制同步减法计数器,其型号是CC4526)

(3)集成4位二进制同步可逆计数器:

①集成4位二进制同步可逆计数器有单时钟和双时钟两种类型,前者用的是T型触发器,后者用的是T’型触发器。

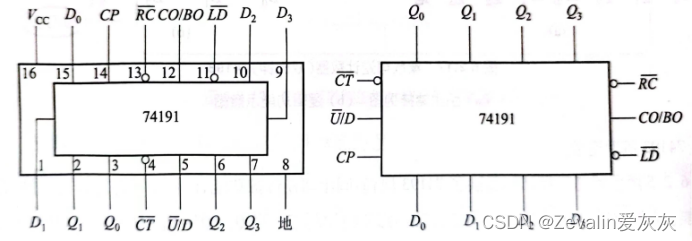

②74191(单时钟):

[1]引出端排列图与逻辑功能示意图:

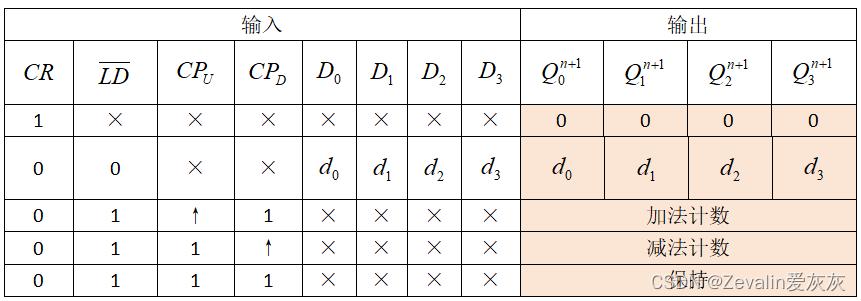

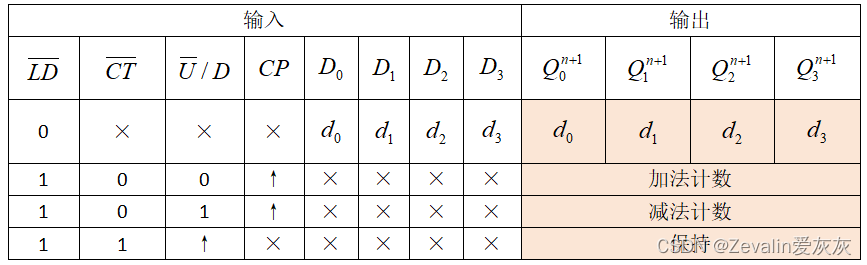

[2]状态表:

[3]74191采取的是异步并行置数,不受时钟脉冲的控制;74191在加法计数模式下,,在减法计数模式下,

。

[4]多个可逆计数器可级联使用,这时有。

[5]与74191功能和引出端排列完全相同的还有74LS191。此外,集成单时钟4位二进制同步可逆计数器还有74S169、74LS169、CC4516等。

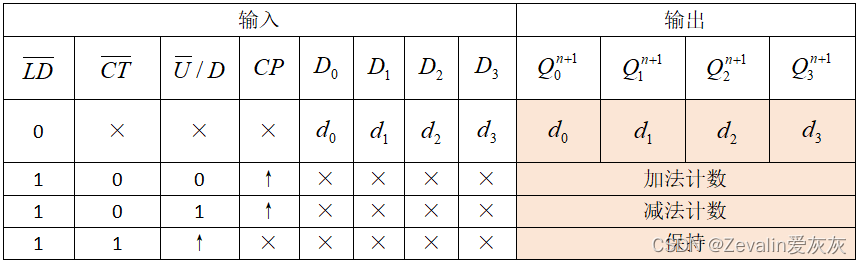

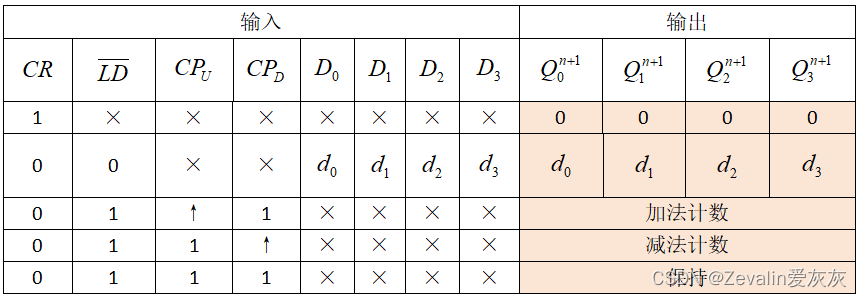

③74193(双时钟):

[1]引出端排列图与逻辑功能示意图:

[2]状态表:

[3]74193采取的是异步并行置数和异步清零,不受时钟脉冲的控制;74193在加法计数模式下,,在减法计数模式下,

。

[4]、

是供多个双时钟可逆计数器级联时使用的,多个74193级联时,只要把低位的]

端、

端分别与高位的

端、

端连接起来,各个芯片的

端连接在一起、

端连接在一起即可。

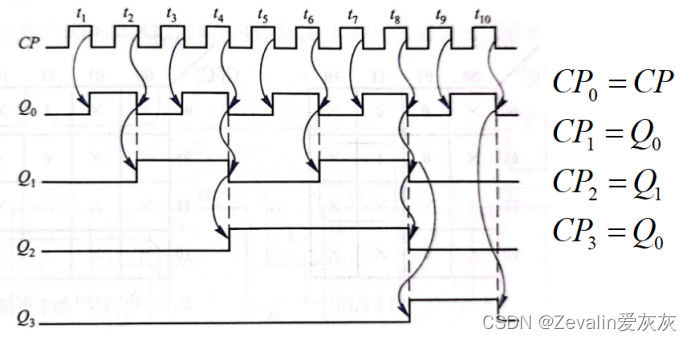

三、二进制异步计数器

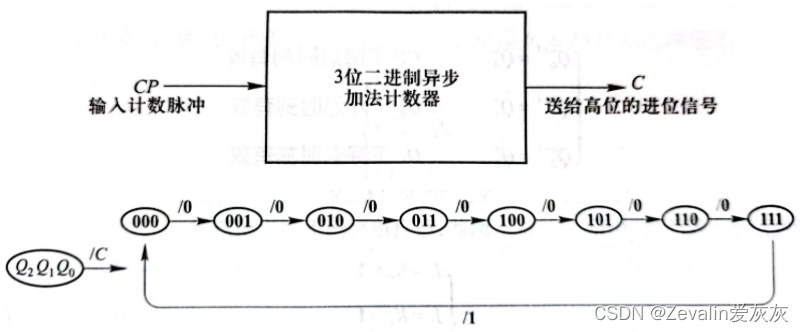

1、3位二进制异步加法计数器

(1)结构示意框图与状态转换图:

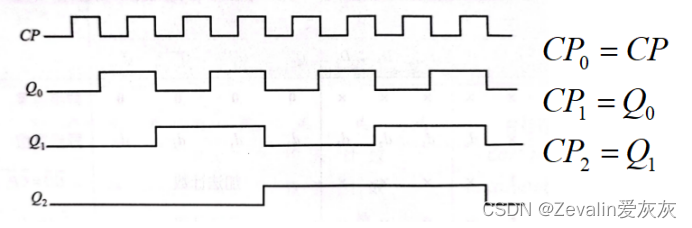

(2)选择触发器,求时钟方程、输出方程和状态方程:

①由于JK触发器功能齐全、使用灵活,故选用3个时钟下降沿触发的边沿JK触发器。

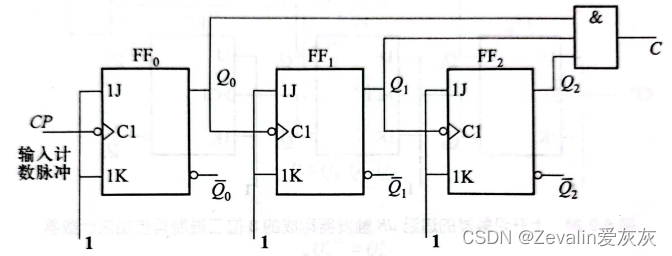

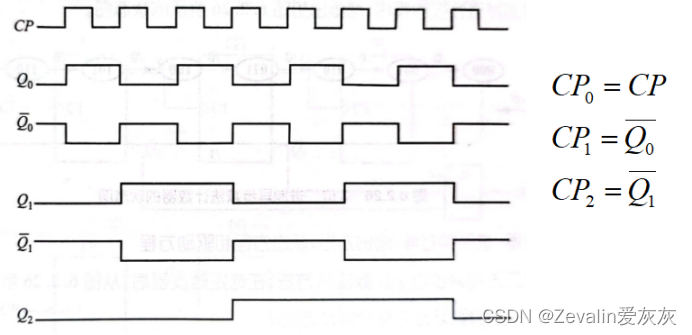

②由于要求构成的是异步计数器,首先画出时序图,然后选择时钟信号,写出时钟方程,如下图所示。

③由上图所示的状态转换图可直接得到输出方程。

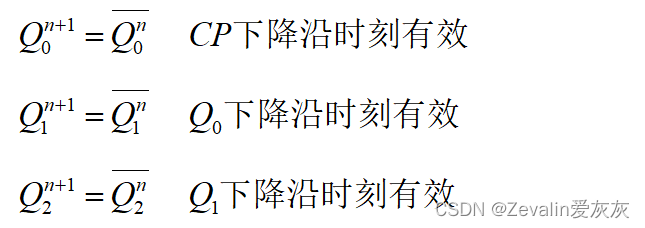

④根据时序图和时钟方程,可知三个时钟触发器均应为T’型(需要翻转的时候有下降沿,不需要翻转时没有下降沿),求得状态方程:

(3)根据JK触发器特性方程的格式变换状态方程式,求出驱动方程。(前面已经做过演示,这里直接写出驱动方程)

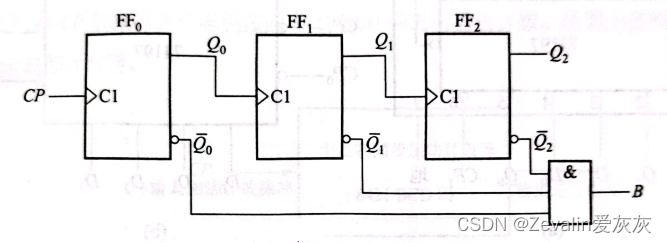

(4)画逻辑电路图:

①根据上面分析过程所得的电路图(用下降沿触发的边沿JK触发器):

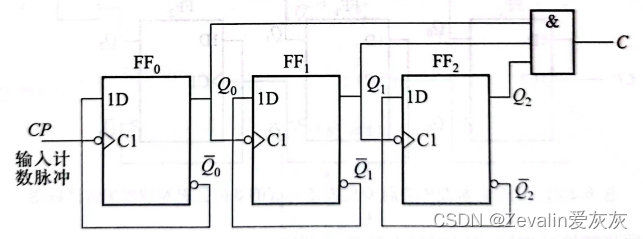

②用下降沿触发的边沿D触发器:

(5)如果选用触发器时选的是时钟脉冲上升沿触发的边沿触发器,则时序图和时钟方程如下图所示,对三个触发器来说,需要翻转时一定有上升沿,不需要翻转时肯定没有上升沿,这样的话用3个T’触发器就可以了。

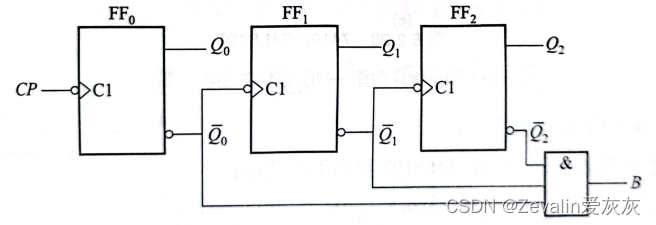

①上升沿触发的边沿JK触发器构成的3位二进制异步加法计数器的逻辑图:

②上升沿触发的边沿D触发器构成的3位二进制异步加法计数器的逻辑图:

(6)二进制异步加法计数器级间连接规律:高位触发器的时钟信号是低位的输出,若选择的是下降沿触发的T’触发器,则应取,如果选用的是上升沿触发的T’触发器,则应取

。(从电路结构看,二进制异步加法计数器使用的单元电路是T’触发器)

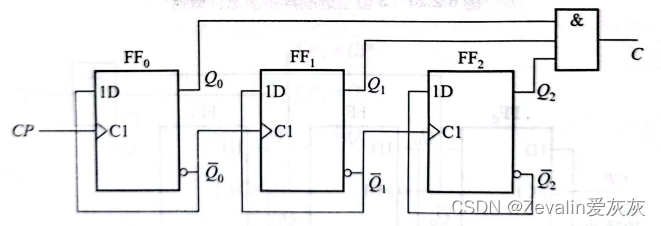

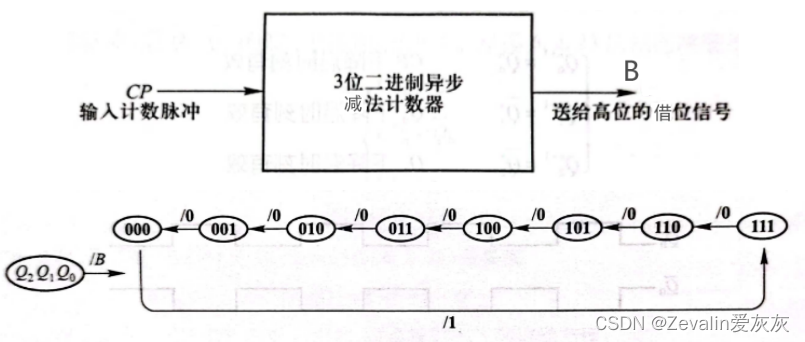

2、3位二进制异步减法计数器

(1)结构示意框图与状态转换图:

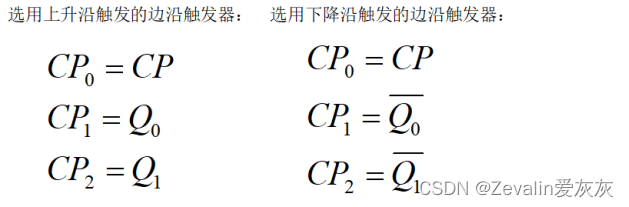

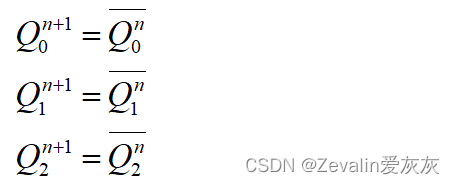

(2)按照构成3位二进制异步加法计数器的方法选用触发器,求时钟方程、输出方程和状态方程:

①时钟方程:

②由上图所示的状态转换图可直接得到输出方程。

③三个时钟触发器均应为T’型,求得状态方程:

(3)根据选用的触发器的特性方程写出驱动方程:

(4)画逻辑电路图:

①用上升沿触发的T’触发器:

②用下降沿触发的T’触发器:

(5)二进制异步减法计数器级间连接规律:高位触发器的时钟信号是低位的输出,若选择的是下降沿触发的T’触发器,则应取,如果选用的是上升沿触发的T’触发器,则应取

。(从电路结构看,二进制异步减法计数器使用的单元电路是T’触发器)

3、集成二进制异步计数器

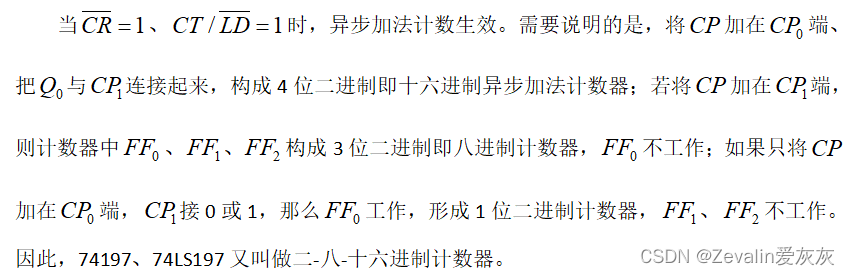

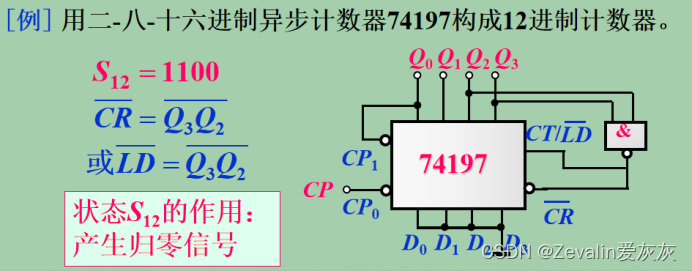

(1)集成二进制异步计数器是指按照自然加权二进制码进行加法计数的电路,规格品种不少,这里以74197、74LS197为例做简单说明。

(2)74197、74LS197的引出端排列图和逻辑功能示意图:

(3)74197、74LS197的状态表:

(4)74197、74LS197的4位二进制异步加法计数功能:

(5)属于二-八-十六进制异步加法计数器的芯片还有74177、74S197、74LS293等,属于双4位二进制异步加法计数器的芯片有74393、74LS393,CMOS集成异步计数器有7位的CC4024、12位的CC4040、14位的CC4060等。

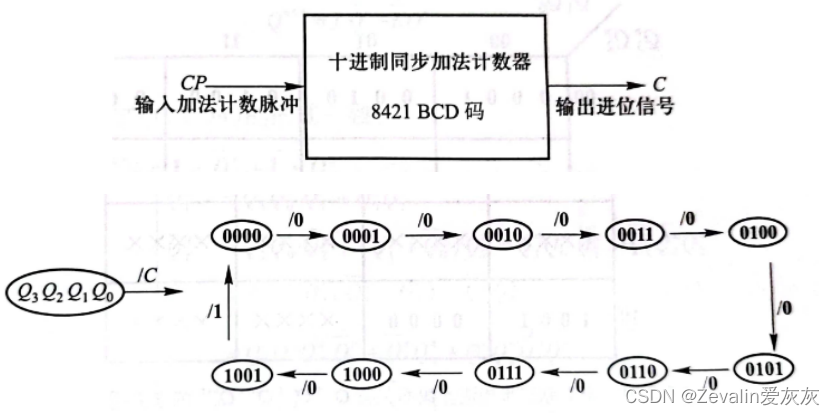

四、十进制同步计数器

1、十进制同步加法计数器

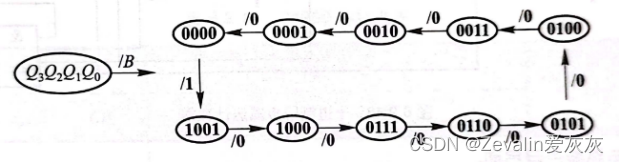

(1)结构示意框图与状态转换图:

(2)选择触发器,求时钟方程、输出方程和状态方程:

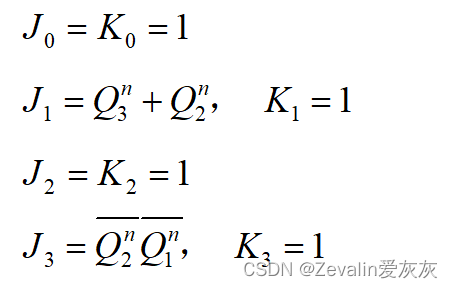

①由于JK触发器功能齐全、使用灵活,故选用4个时钟下降沿触发的边沿JK触发器。

②由于要求构成的是同步计数器,显然各个触发器的时钟信号都应使用输入计数脉冲CP,即。

③由上图所示的状态转换图可直接得到输出方程。

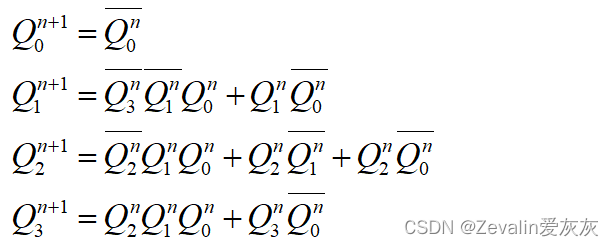

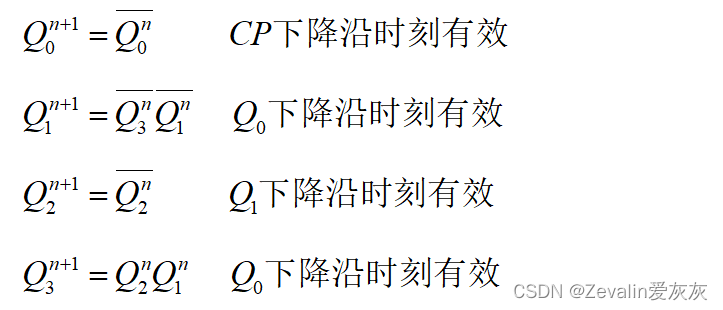

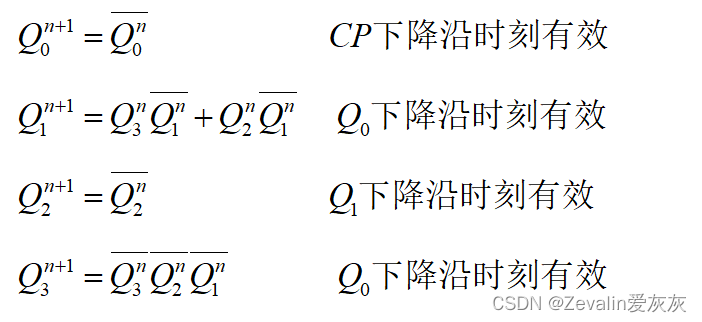

④根据状态转换图可画出各个触发器次态的卡诺图(前面已经有示例,这里不再赘述),根据卡诺图可求得状态方程:

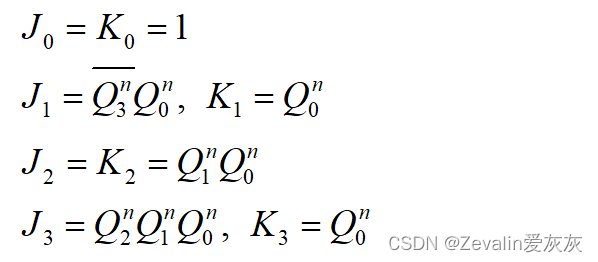

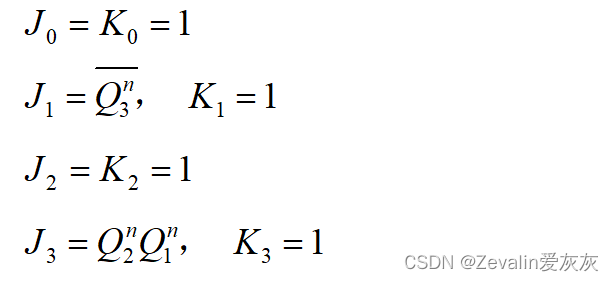

(3)根据JK触发器特性方程的格式变换状态方程式,求出驱动方程。(前面已经做过演示,这里直接写出驱动方程)

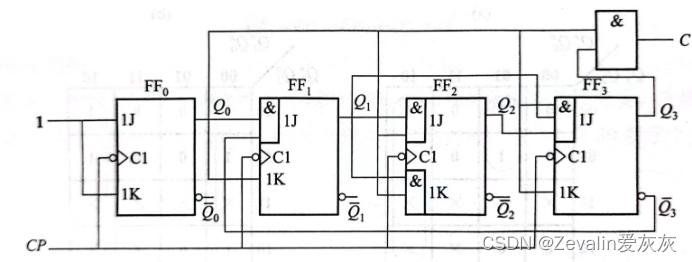

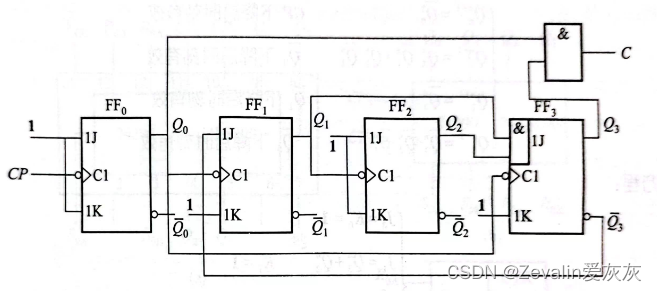

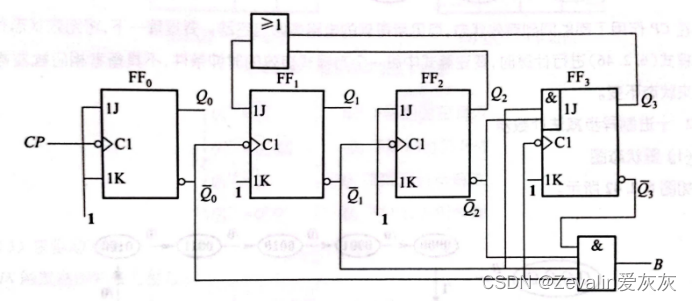

(4)画逻辑电路图:

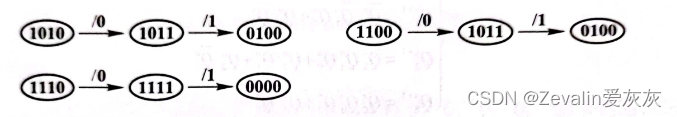

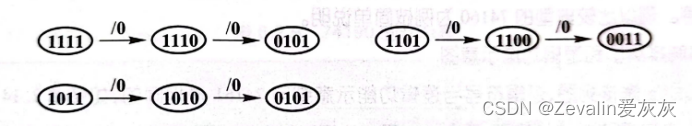

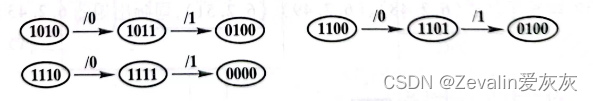

(5)将无效状态代入状态方程中进行计算,检查电路能否自启动,都能回到有效状态说明能够自启动。

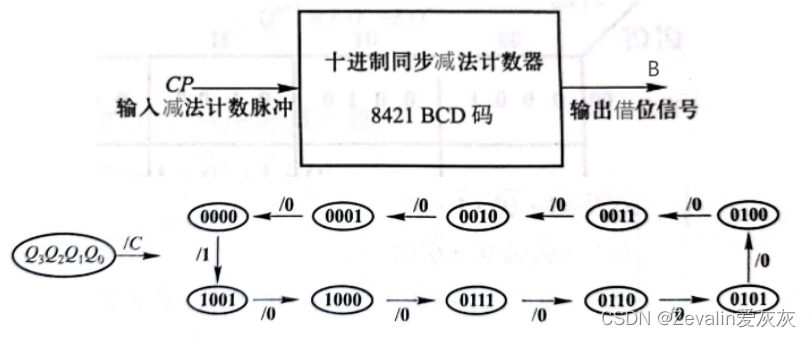

2、十进制同步减法计数器

(1)结构示意框图与状态转换图:

(2)选择触发器,求时钟方程、输出方程和状态方程:

①由于JK触发器功能齐全、使用灵活,故选用4个时钟下降沿触发的边沿JK触发器。

②由于要求构成的是同步计数器,显然各个触发器的时钟信号都应使用输入计数脉冲CP,即。

③由上图所示的状态转换图可直接得到输出方程。

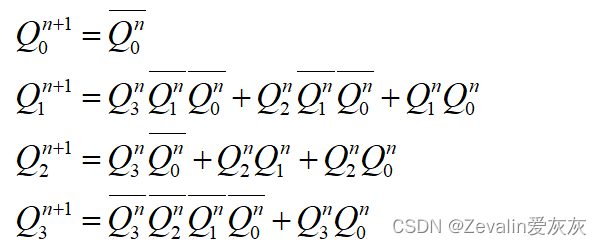

④根据状态转换图可画出各个触发器次态的卡诺图(前面已经有示例,这里不再赘述),根据卡诺图可求得状态方程:

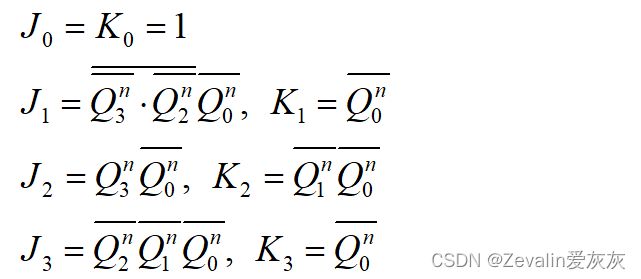

(3)根据JK触发器特性方程的格式变换状态方程式,求出驱动方程。(前面已经做过演示,这里直接写出驱动方程)

(4)画逻辑电路图:

(5)将无效状态代入状态方程中进行计算,检查电路能否自启动,都能回到有效状态说明能够自启动。

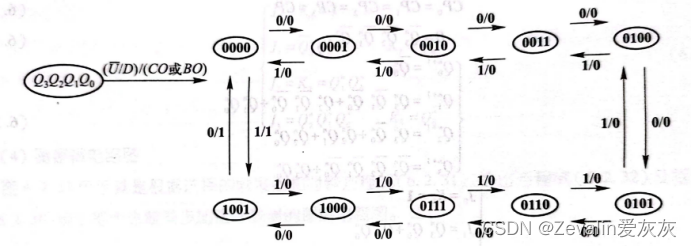

3、十进制同步可逆计数器

(1)在加减控制信号的管理下,把十进制同步加法计数器和减法计数器组合起来便可获得二进制同步可逆计数器。

(2)十进制同步可逆计数器也分单时钟输入十进制同步可逆计数器和双时钟输入十进制同步可逆计数器,下面给出它们的状态转换图,其余部分由于篇幅有限,这里不再赘述。

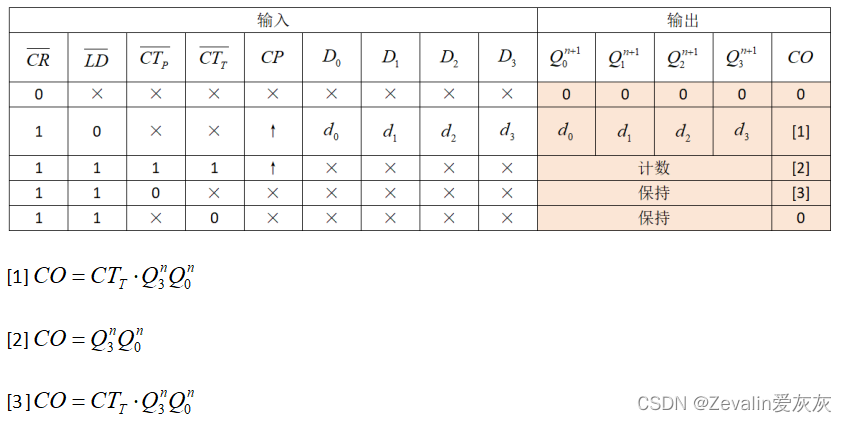

4、集成十进制同步计数器

(1)常用的十进制同步计数器有加法计数和可逆计数两大类,采用的都是8421 BCD码。

(2)集成十进制同步加法器:

①集成十进制同步加法器,TTL产品有74160、74LS160、74162、74S162、74LS162等,CMOS产品有CC4518等,下面以74160为例做介绍。

②74160的引出端排列图、逻辑符号和逻辑功能示意图与74161是相同的,只不过74160是十进制同步加法器。

③74160的状态表:

④74160有异步清零功能、同步置数功能、同步计数功能和保持功能,这些前面都有提及,这里不再赘述。(需要说明的是,74162、74S162、74LS162采用的是同步清零方式,时需要时钟上升沿到来后才能将计数器清零)

(3)集成十进制异步加法器:

①集成十进制异步加法器常见的产品有74192、74LS192、74168、74LS168、74190、74LS190、CC4510、CC40192等,下面以74190和74190为例做介绍。

②74190(单时钟):

[1]引出端排列图与逻辑功能示意图与74191相同,只不过74190是十进制异步加法器。

[2]状态表:

[3]74190采取的是异步并行置数,不受时钟脉冲的控制;74190在加法计数模式下,,在减法计数模式下,

。

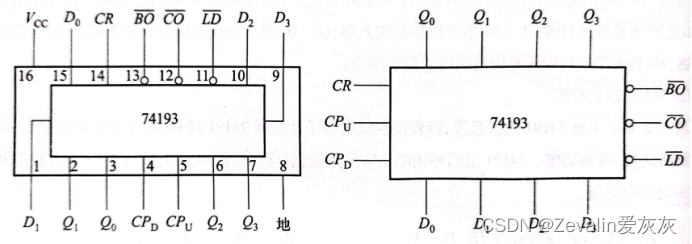

③74192(双时钟):

[1]引出端排列图与逻辑功能示意图与74193相同,只不过74192是十进制异步加法器。

[2]状态表:

[3]74193采取的是异步并行置数和异步清零,不受时钟脉冲的控制;74193在加法计数模式下,在减法计数模式下,

;在保持模式下,

。

五、十进制异步计数器

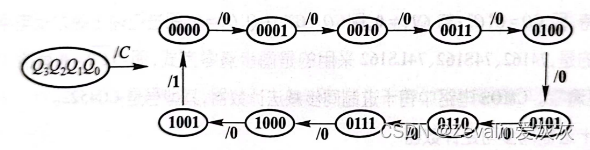

1、十进制异步加法计数器

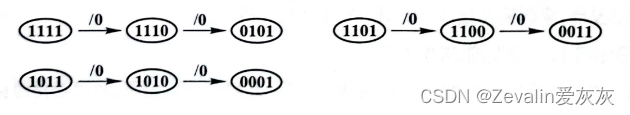

(1)状态转换图:

(2)选择触发器,求时钟方程、输出方程和状态方程:

①由于JK触发器功能齐全、使用灵活,故选用4个时钟下降沿触发的边沿JK触发器。

②由于要求构成的是异步计数器,首先画出时序图,然后选择时钟信号,写出时钟方程,如下图所示。

③由上图所示的状态转换图可得到输出方程。

④根据时序图和时钟方程,可知四个时钟触发器均应为T’型(需要翻转的时候有下降沿,不需要翻转时没有下降沿),求得状态方程:

(3)根据JK触发器特性方程的格式变换状态方程式,求出驱动方程。(前面已经做过演示,这里直接写出驱动方程)

(4)画逻辑电路图:

(5)将无效状态代入状态方程中进行计算,检查电路能否自启动,都能回到有效状态说明能够自启动。

2、十进制异步减法计数器

(1)状态转换图:

(2)按照构十进制异步加法计数器的方法,选用4个时钟下降沿触发的边沿JK触发器,求时钟方程、输出方程和状态方程:

①时钟方程:

②由上图所示的状态转换图可直接得到输出方程。

③四个时钟触发器均应为T’型,求得状态方程:

(3)根据JK触发器特性方程的格式变换状态方程式,求出驱动方程。(前面已经做过演示,这里直接写出驱动方程)

(4)画逻辑电路图:

(5)将无效状态代入状态方程中进行计算,检查电路能否自启动,都能回到有效状态说明能够自启动。

3、集成十进制异步计数器

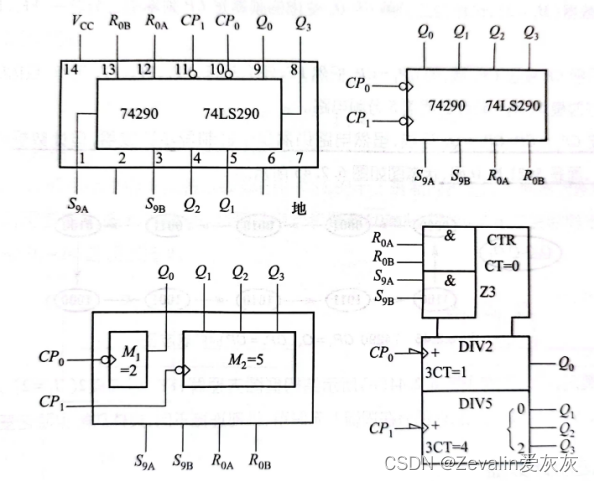

(1)集成十进制异步计数器常用的型号有74196、74S196、74LS196、74290、74LS290等,它们都是按照8421 BCD码进行加法计数的电路,下面以74290为例进行介绍。

(2)74290的引出端排列图、逻辑功能示意图、结构框图和国标逻辑符号:

(3)74290的状态表:

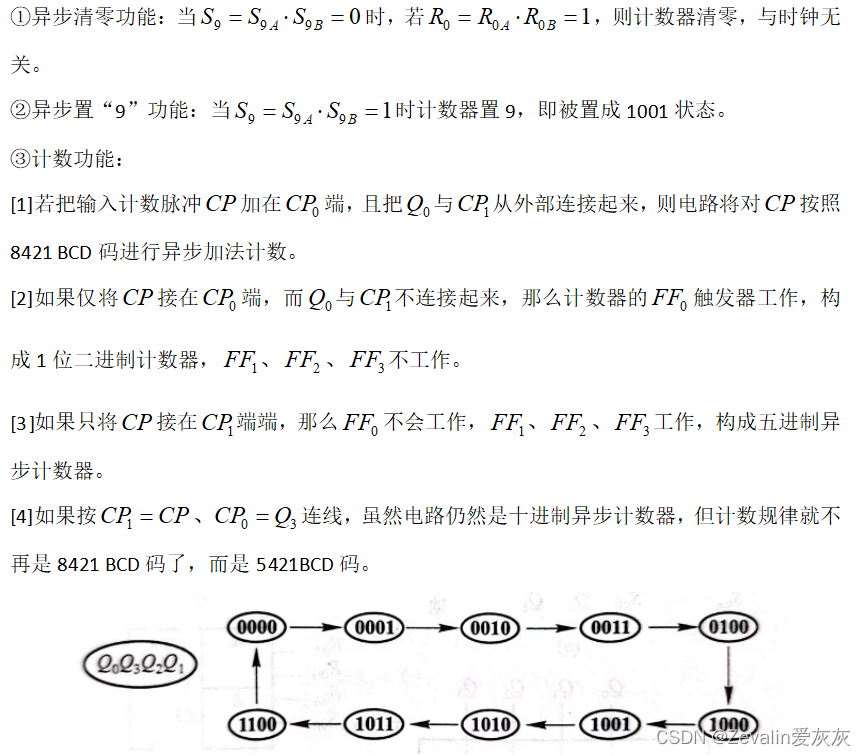

(4)74290的功能详解:

六、N进制计数器

1、利用同步清零或置数端获得N进制计数

(1)主要步骤:

①写出状态的二进制代码。

②求归零逻辑——同步清零端或置数控制端信号的逻辑表达式。(同步清零或置数端的计数终值为)

③画连线图。(主要体现在右侧的与门上,当计数器的值到达需要实现的进制N-1后,与门将会输出低电平给计数器的清零端,从而使后面的计数清零)

(2)应用举例:

2、利用异步清零或置数端获得N进制计数

(1)主要步骤:

①写出状态的二进制代码。

②求归零逻辑——异步清零端或置数控制端信号的逻辑表达式。(异步清零或置数端的计数终值为)

③画连线图。(主要体现在右侧的与门上,当计数器的值到达需要实现的进制N后,与门将会输出低电平给计数器的清零端,从而使后面的计数清零)

(2)应用举例:

3、计数容量的扩展

(1)把集成计数器级联起来扩展容量:

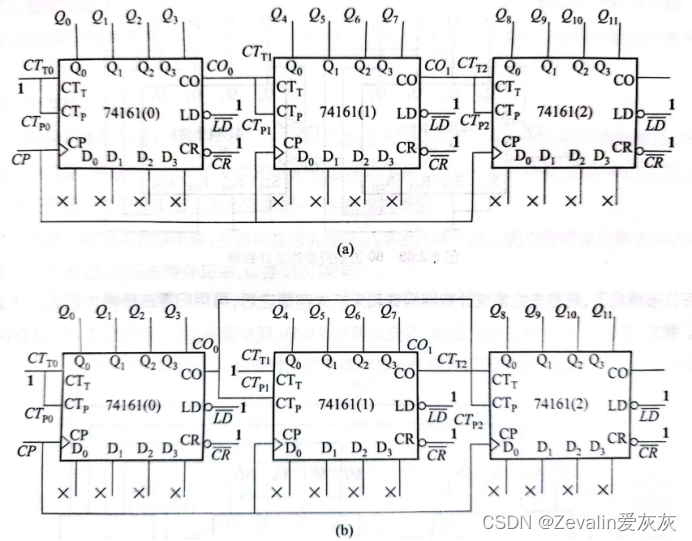

①三片76161级联起来构成的4096进制(12位二进制)同步加法计数器((b)是(a)的改进接法):

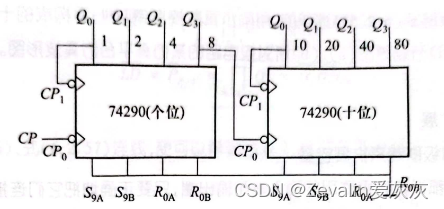

②两片74290级联起来构成的100进制(2位十进制)计数器:

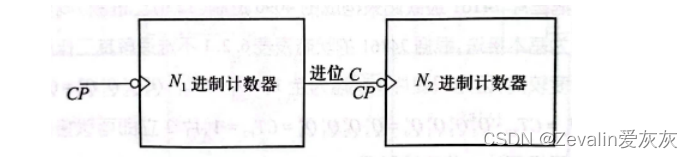

(2)利用级联获得大容量N进制计数器:

①所谓级联方法,就是把多个计数器串接起来,从而获得所需要的大容量N进制计数器,例如把一个进制计数器和一个

进制计数器串接起来,便可构成

进制计数器。

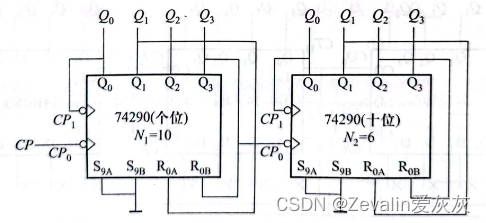

②由六进制和十进制计数器级联起来构成的60进制计数器:

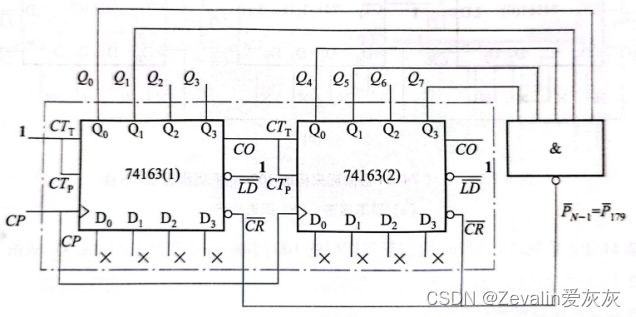

③在许多情况下,则是先把集成计数器级联起来扩大容量之后,再用归零法获得大容量的N进制计数器,下图所示是用两片74163(同步清零)级联起来构成的256进制计数器,借助同步归零法(主要体现在右侧的与门上,当计数器的值到达179后,与门将会输出低电平给计数器的清零端,从而使后面的计数清零)改造逻辑图后便得到180进制同步加法计数器。

4365

4365

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?