1. 问题描述:

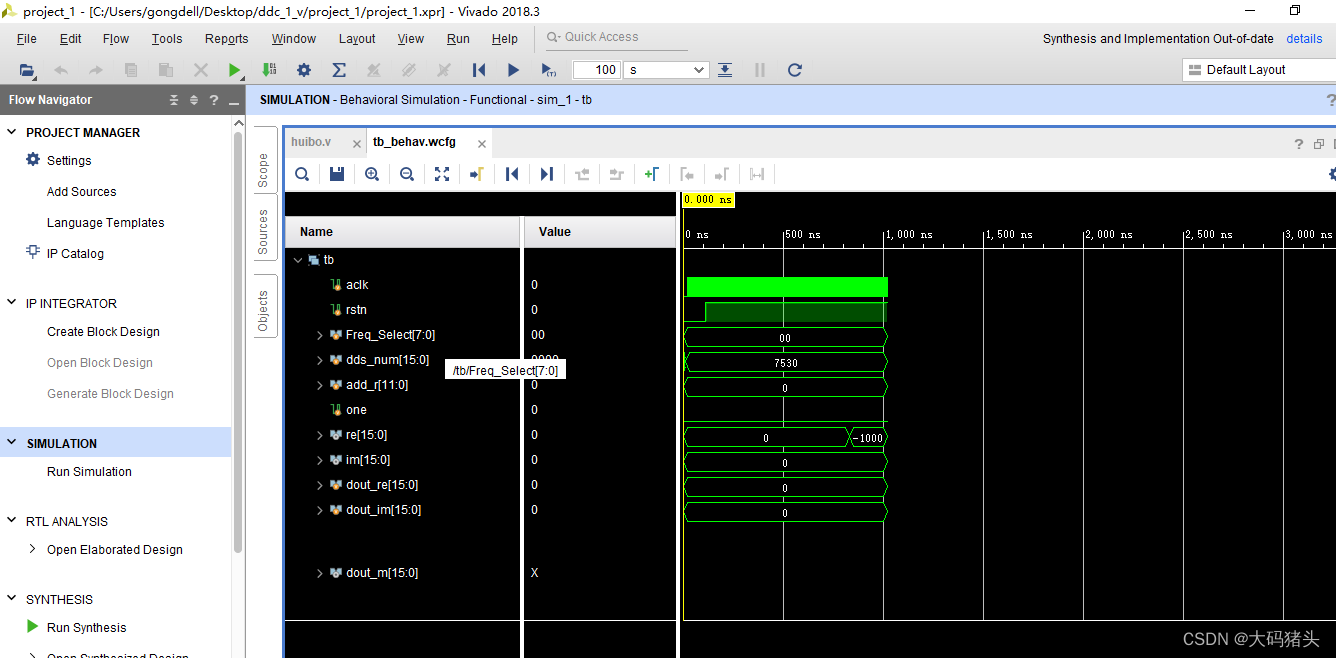

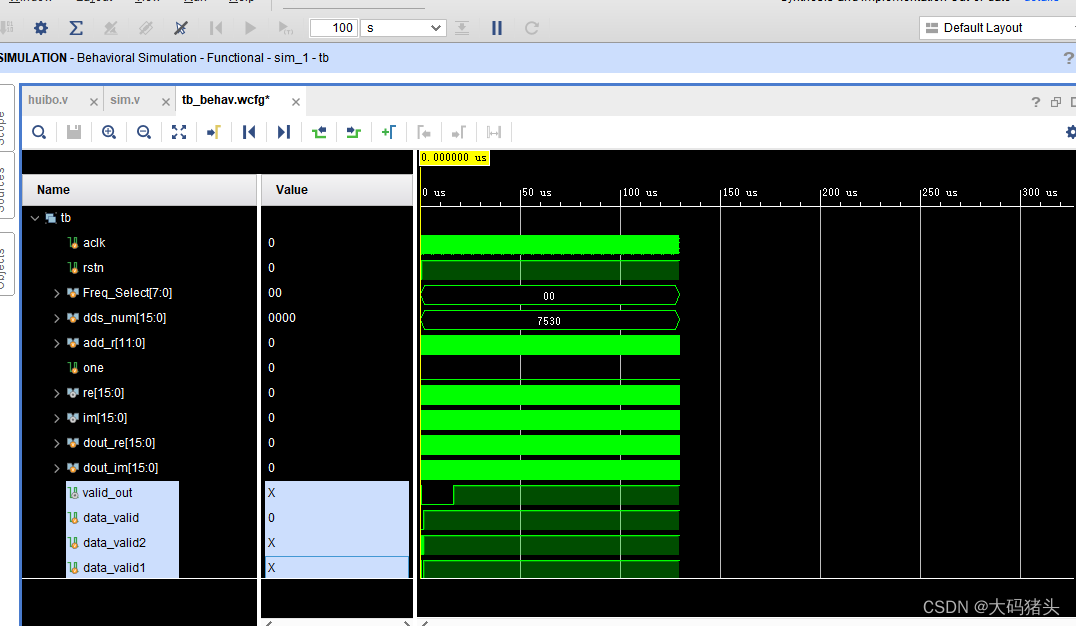

我们在编写完程序后,没有看到.v的模块有ERROR,或者是严重警告(CRITICAL WARRING),然后开始对这个模块进行功能仿真,然后仿真simulation也可以成功运行,成功进入到了波形的界面,如下图所示:

此时我们点击上面的哪个三角形按钮,进行仿真的开始。如果是正常情况的话,那么后续的波形会一直跑下去,直到设定好的时间值。

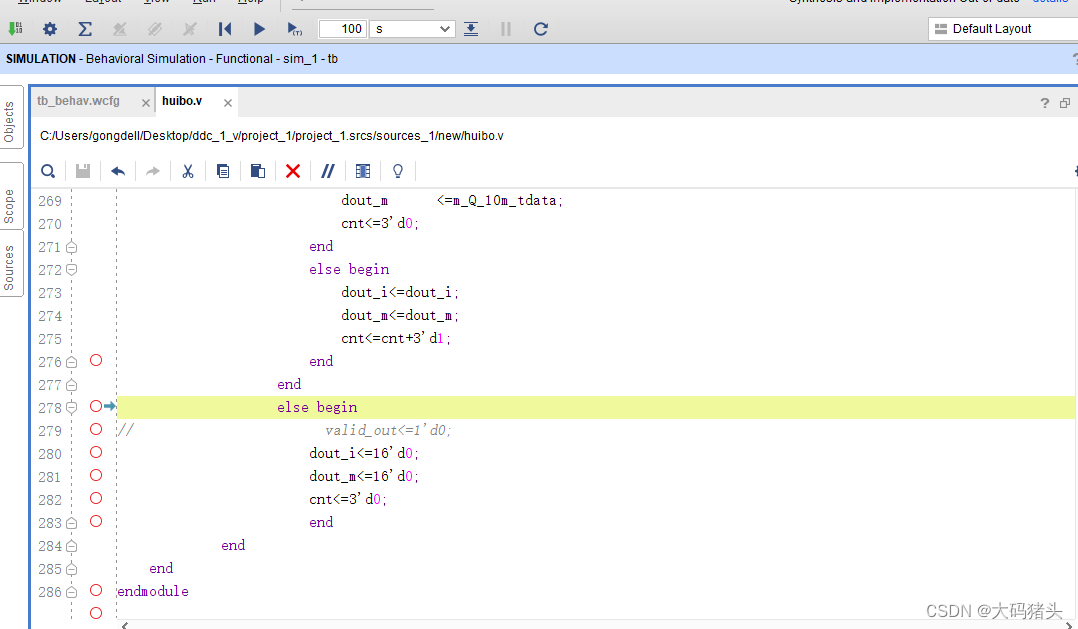

但是现在问题出现了,我点击了按钮以后就是下图这个情况,这个箭头指到这个地方,再点几次也是一样,说明我们的仿真停滞了,就停在这里没办法继续下去了。

2. 问题分析:

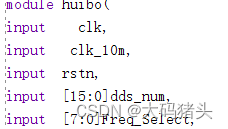

我的程序是没有报错的,逻辑上也是没有问题的,但是时序上出现了错误。时序上是不对的,主要是复位信号混乱导致的。如下:我先在输入模块里输入了rstn信号,然后rstn给到了时钟IP核,IP核又输出个locked信号。

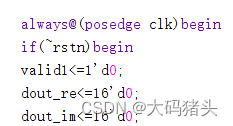

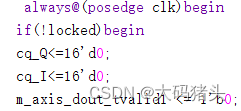

然后我在后续的逻辑里,一会用rstn信号作判断,一会用locked信号作判断,如下图。

这个在数字逻辑上是没有问题,但是在时序逻辑上是有错误的,因为不同的复位信号导致代码段不是同时运行,在时序上是对不准的,所以就可能会出现断点(看你的.v的逻辑怎么写),就是仿真器也不知道该怎么走了,然后就直接开摆下线罢工,把程序指到哪个断点的位置。

3. 解决办法:修改复位信号。最好保证一个.v文件共用同一个复位信号。

其实在具体的设计当中,不共用同一个复位信号是没有问题的,但是这样设计的时候,时序一定要非常清晰才对。不同时复位是有不同时复位的设计原因,是你的代码需要这么设计,而不是键盘敲错了。

我这里心里想的设计,是用同一个复位信号,对整个.v文件进行复位的,结果只是粗心大意,敲错了代码,导致时序逻辑对不上,所以才会运行不下去。

在修改完成以后,就可以跑通了,后续继续进行仿真验证就没问题了。如下图所示:

4. 其他情况:

大概就是类似于上述问题,代码中的逻辑没有很连贯,比如你有个信号连错了,或者是某个无用的信号,有一段逻辑注释掉了,导致这个信号的值不是连续的,等等,就是这种错误。

ojbk!(可以给个大拇指吗????哈哈哈哈哈)

至此,问题解决,所以即使有时候程序运行不下去,还是代码写的不对。需要多找找。楼主在这里只是提供一种解决问题的思路,如果解决不了。可能是其他问题:如软件装错了,代码还是有其他问题,配置错误等。祝小伙伴们早点解决这个问题。

本文描述了一次编程中遇到的问题,程序无误但仿真停滞,经分析发现是由于复位信号使用不当导致时序逻辑错误。作者分享了解决方法——确保所有.v模块共用同一复位信号,并强调了时序清晰的重要性。最后,通过修改代码解决了问题并给出了类似错误排查的建议。

本文描述了一次编程中遇到的问题,程序无误但仿真停滞,经分析发现是由于复位信号使用不当导致时序逻辑错误。作者分享了解决方法——确保所有.v模块共用同一复位信号,并强调了时序清晰的重要性。最后,通过修改代码解决了问题并给出了类似错误排查的建议。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?