PLL的英文全称(Phase Locked Loop),即锁相环,是一个反馈控制电路。对于PLL的概念不做过于详细的介绍,只需要知道它有如下几个作用:

1.具有时钟倍频、分频、相位偏移和可编程占空比的功能;

2.FPGA内部产生的信号不能驱动PLL;

3.不同的FPGA的PLL是不一样的,以Cyclone IV为例,它有两个PLL,每个PLL可以提供5路输出。

下面结合Quartus进行具体介绍:

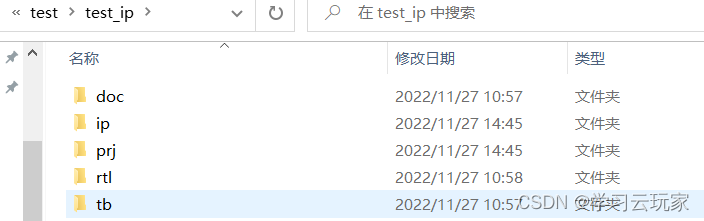

一、设置ip

1.首先创建一个工程文件夹,新建一个pll.v文件放于工程ip文件目录:

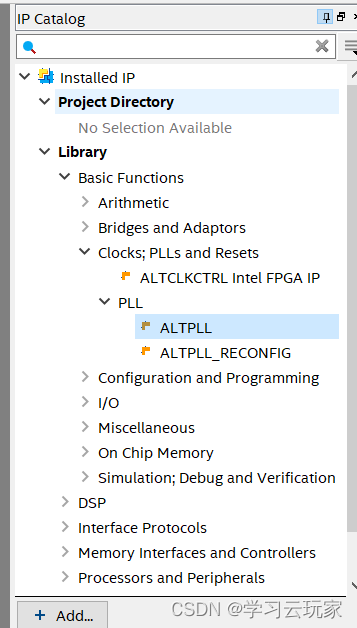

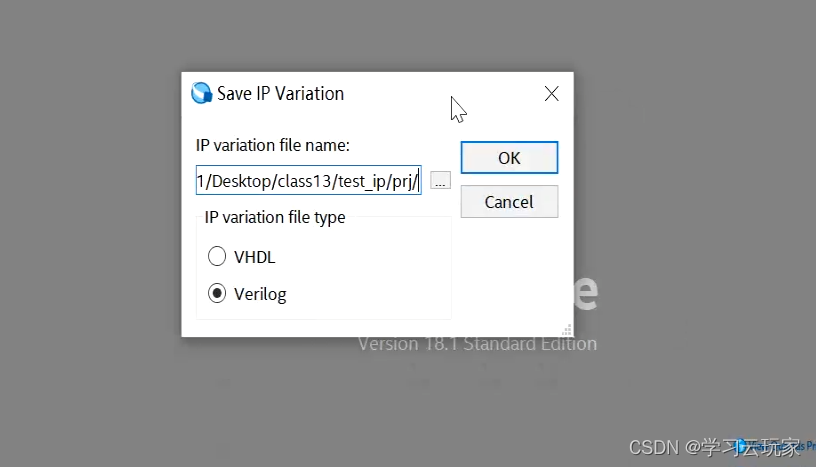

2.用 Quartus新建一个工程,在其右边界面IP Catalog依次选择Library--Basic Functions--Clocks--PLL--ALTPLL,双击ALTPLL,导入刚建立的pll.v文件点击ok:

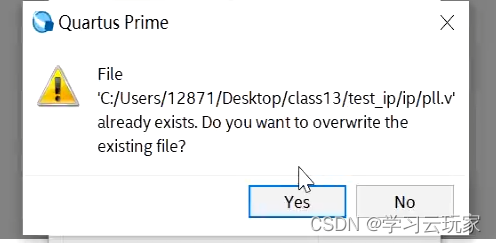

点击ok后会出现以下信息,选择yes覆盖:

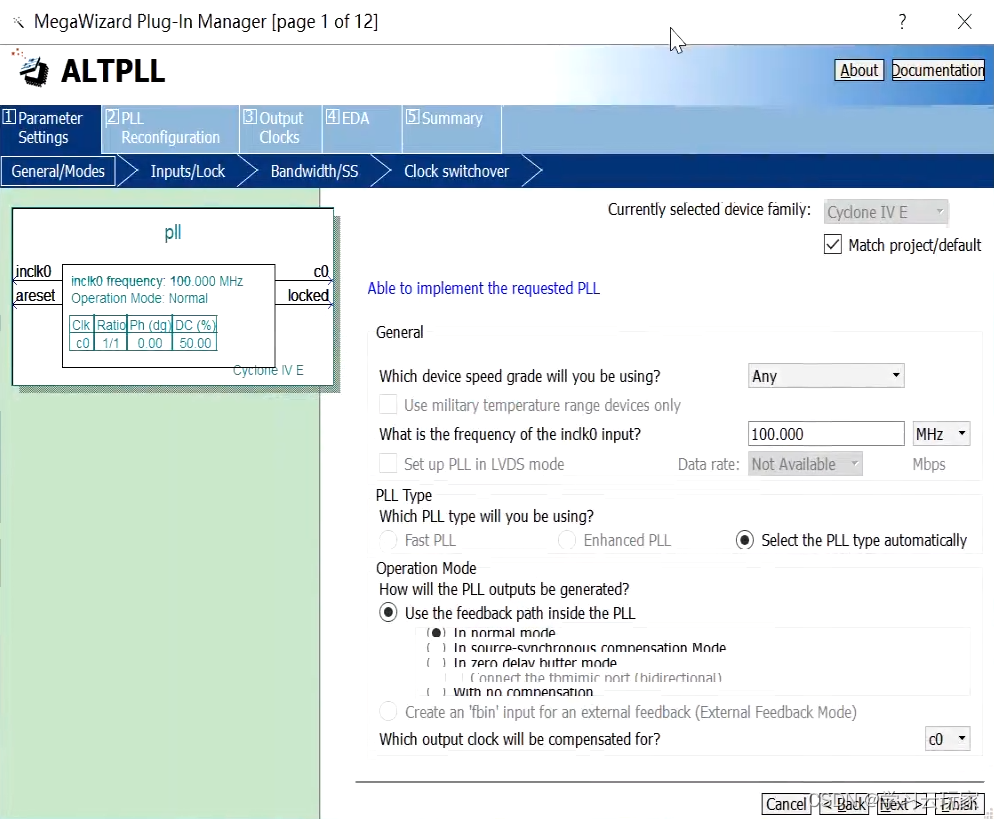

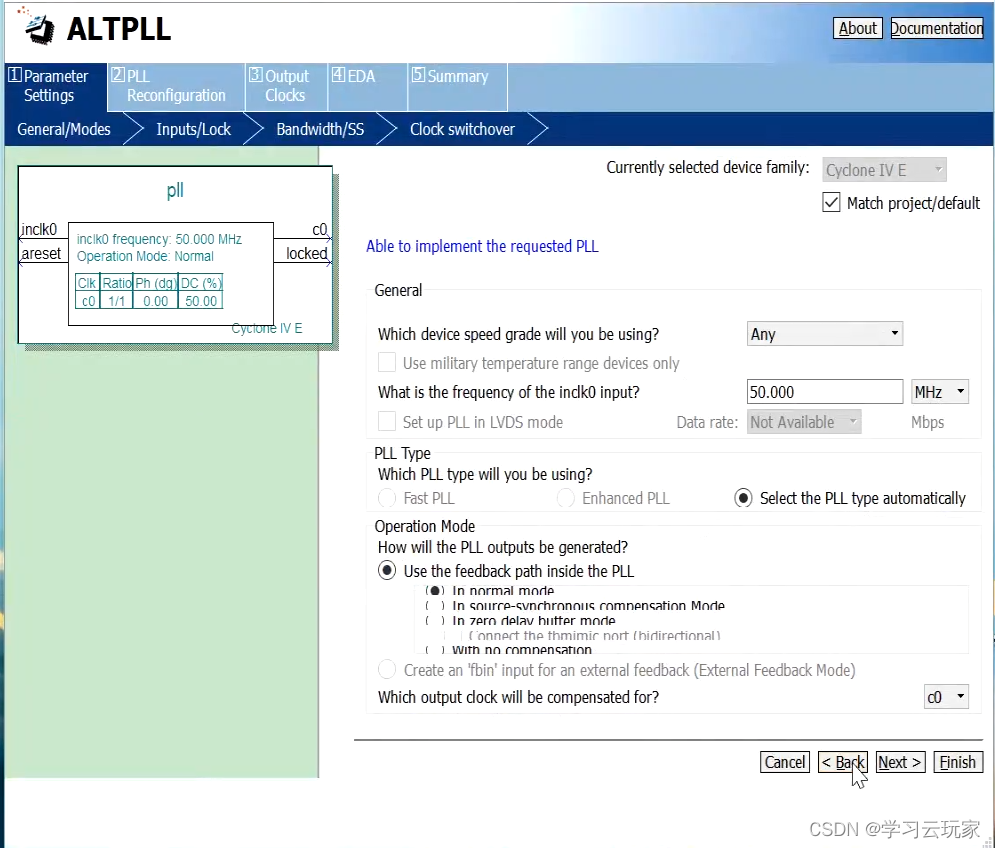

然后就会出现如下界面进行相应参数调整,首先是Parameter Settings部分:

调整时钟频率(跟随晶振时钟50MHz) :

然后一路next(如需要用到带宽自行调节,本次不涉及带宽便不选择)。

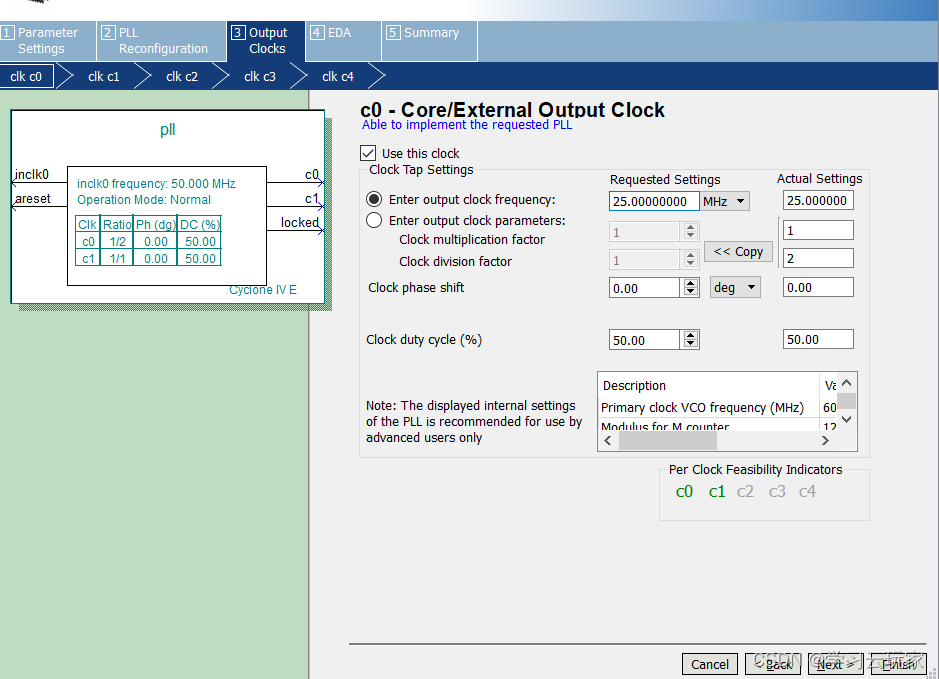

再进入Output Clocks调整参数,可以看到PLL有5路时钟输出:

假设时钟clk0使用25MHz频率,可以看到倍频clock multiplication factor的参数为1,分频clock division factor的参数为2,即是对晶振50MHz进行了2分频,相位偏移clock phase shift设置为0,占空比clock duty cycle为50%。

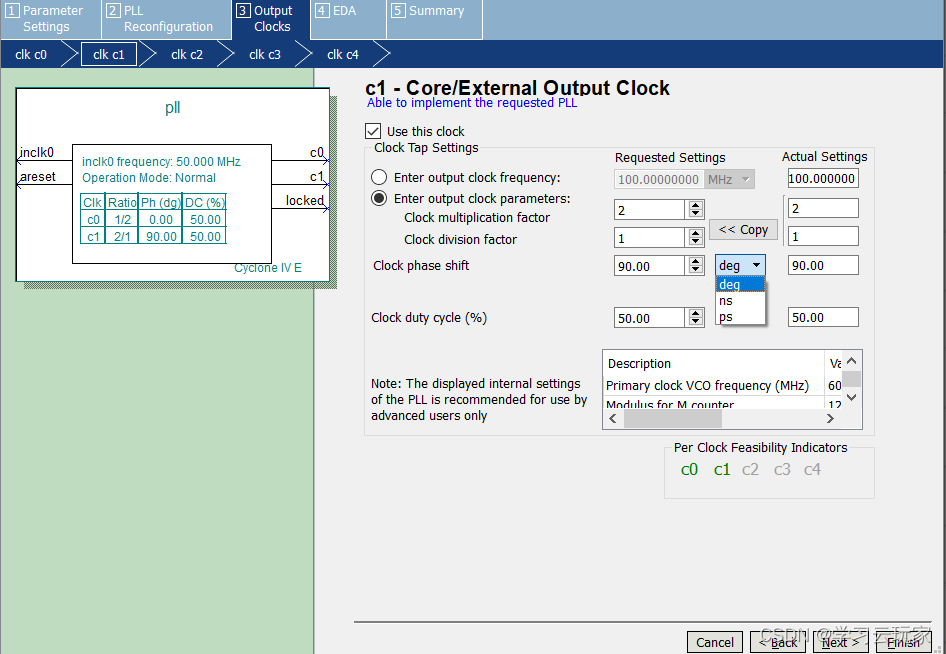

再对clk1进行参数配置:选择直接利用分频和倍频确定频率,此处是选择了2倍频,所以clk1输出为100MHz,相位偏移设置为90°,当然也可以选择对时间进行偏移(ns/ps):

再用clk2产生一个对于clk1而言的一个相位偏移参考时钟:

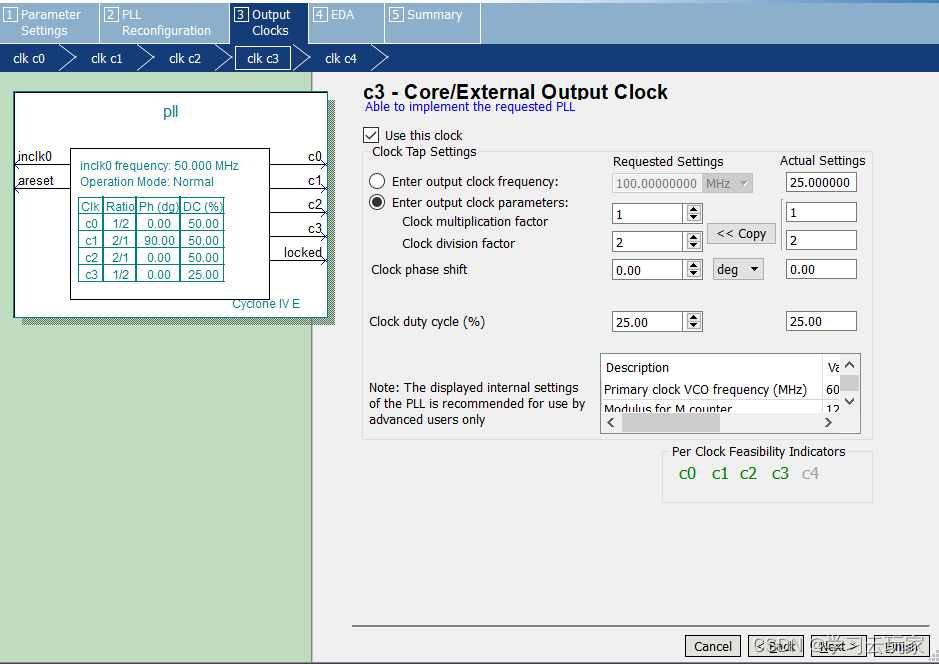

时钟clk3选择2分频,占空比为25%:

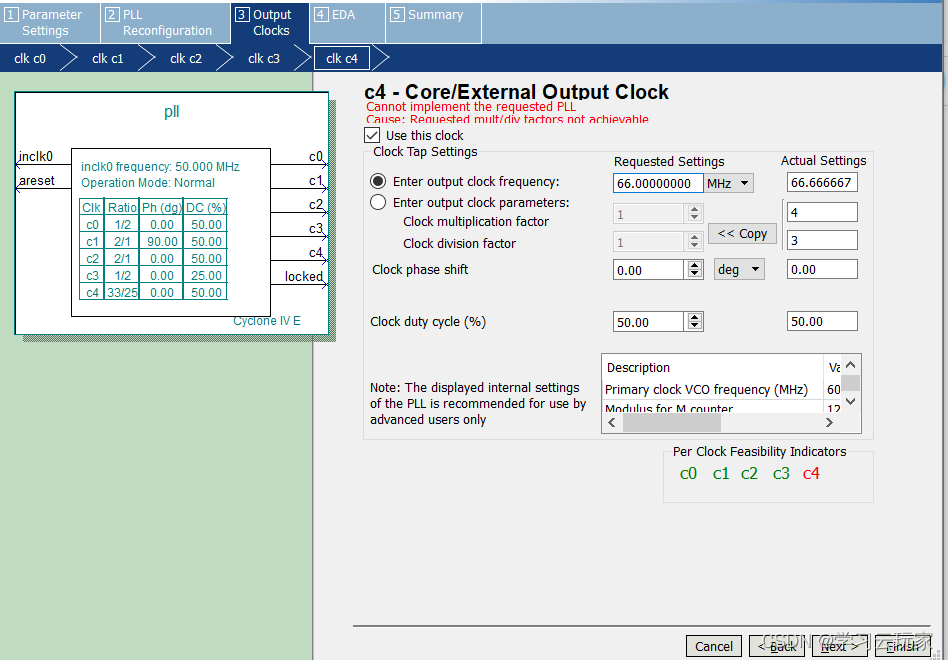

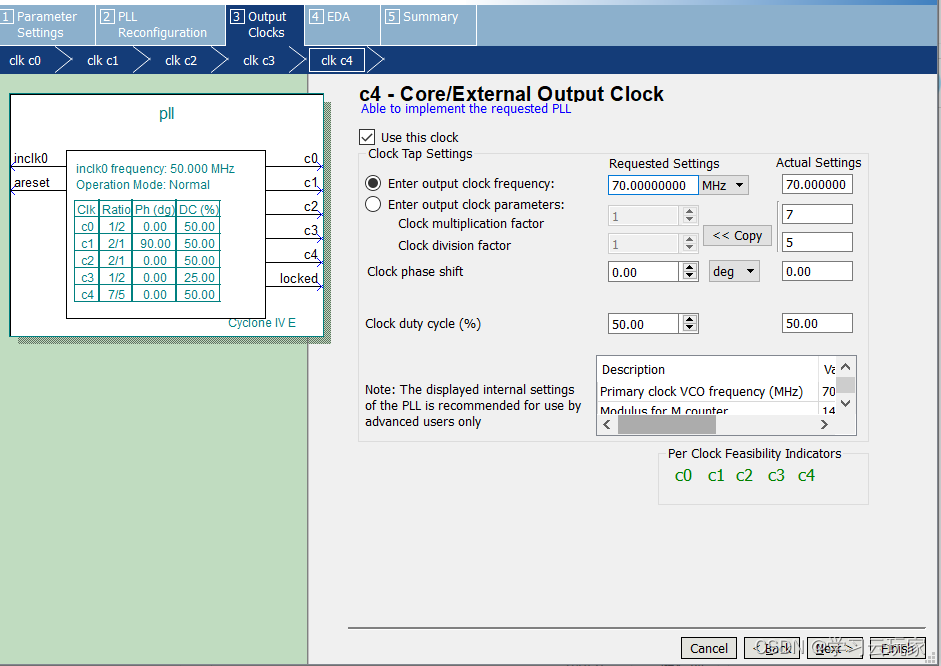

最后一个时钟直接选择频率,注意的是,如果配置的频率出现了红字部分是有问题的,需要配置为显示蓝字许可才行,这里设置为70MHz合理:

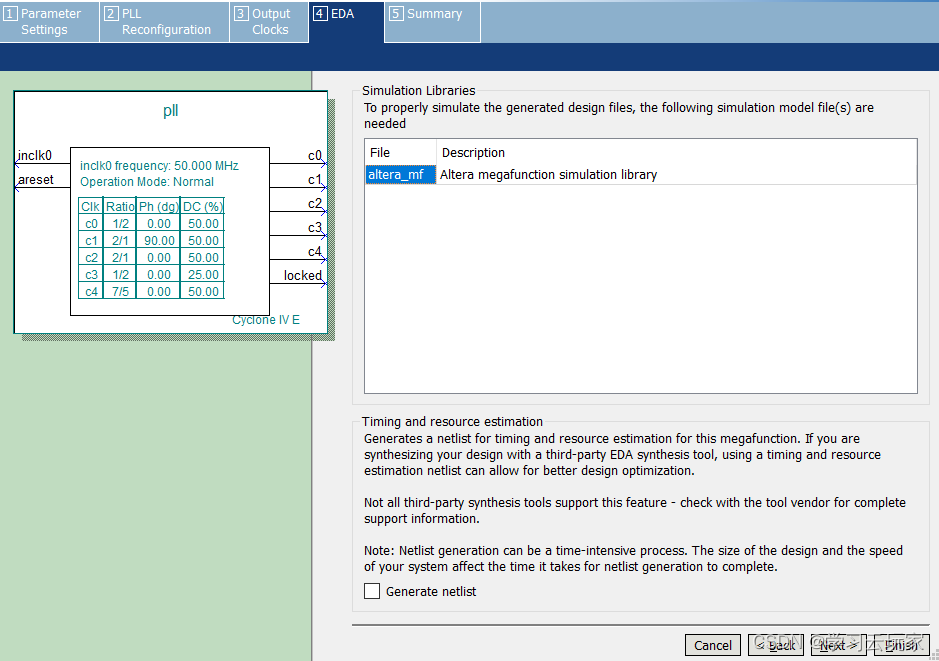

点击下一步,会检测到一个功能仿真文件库altera_mf(此文件是提前放进工程文件夹下):

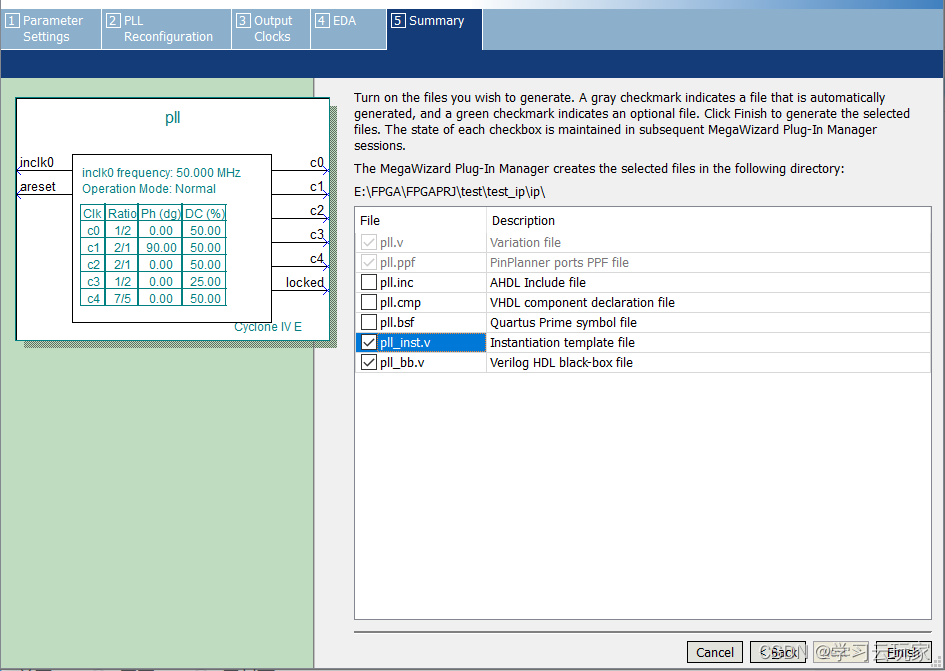

点击next,可以看到如下界面,勾选产生激励文件,整个PLL的模块的时钟参数配置如图,其分频倍频相位偏移以及占空比情况一目了然:

最后点击完成,会让你添加到ip文件夹里面,点击yes:

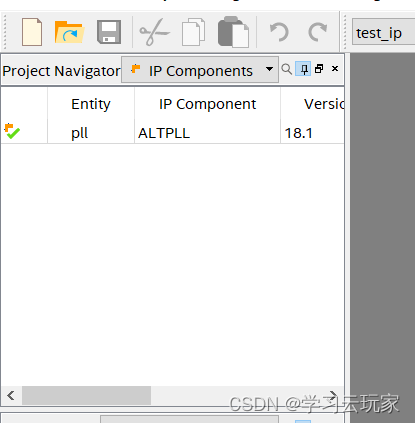

执行后便可以在Quartus里面看到ip组件:

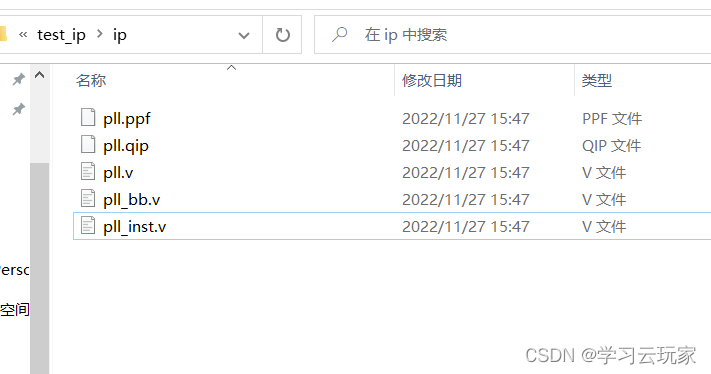

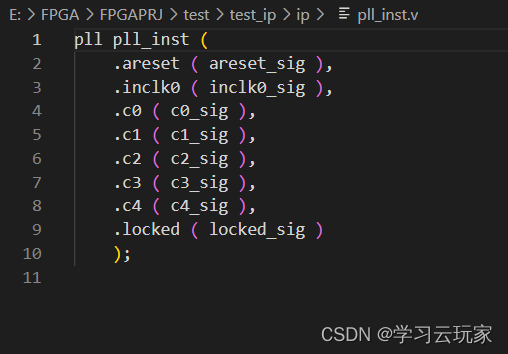

以及ip文件夹下会多出几个文件,其中点击inst文件就可以看到激励文件的端口信息:

二、硬件语言描述

根据pll.v以及pll_inst.v,编写顶层文件以及测试文件

顶层test_ip代码:

module test_ip (

input rst_n,

input clk,

output c0 ,

output c1 ,

output c2 ,

output c3 ,

output c4 ,

output locked

);

pll pll_inst (

.areset ( ~rst_n ),//根据cyclone iv手册,pll复位高电平有效,而设计的rst_n为低电平有效

.inclk0 ( clk ),

.c0 ( c0 ),

.c1 ( c1 ),

.c2 ( c2 ),

.c3 ( c3 ),

.c4 ( c4 ),

.locked ( locked )

);

endmodule

测试文件:

`timescale 1ns/1ps

module test_tb();

reg rst_n ;

reg clk ;

wire c0 ;

wire c1 ;

wire c2 ;

wire c3 ;

wire c4 ;

wire locked ;

parameter CYCLE = 20;

test_ip u_test_ip (

.rst_n ( rst_n ),

.clk ( clk ),

.c0 ( c0 ),

.c1 ( c1 ),

.c2 ( c2 ),

.c3 ( c3 ),

.c4 ( c4 ),

.locked ( locked)

);

initial begin

clk = 1'b1;

rst_n = 1'b1;

#(2*CYCLE)

rst_n = 1'b0;

#(5*CYCLE)

rst_n = 1'b1;

#(200*CYCLE)

$stop;

end

always #(CYCLE/2) clk = ~clk ;//50M

endmodule

另外,这里是用do文件直接在modelsim仿真,编写test.do文件并置于相应目录下:

vlib work

vmap work work#编译testbench文件

vlog test_tb.v

#编译 设计文件

vlog ../ip/pll.v

vlog ../rtl/test_ip.v

vlog altera_mf.v

#指定仿真顶层

vsim -novopt work.test_tb

#添加信号到波形窗

add wave -position insertpoint sim:/test_tb//*run -all

三、仿真结果

打开modelsim,修改到文件路径,命令窗口执行do test.do,得到仿真波形:

图中间部分有一段红色是因为锁住了时钟导致没有波形,截取相应的时钟片段可以验证符合设计要求。

3240

3240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?