PS:给出关键结论,以便复习。具体思路还得看书。

若un=350*10^(-4),,

| (介电常数*8.854*10e-12) / tox,SIO2介电常数=3.9 用这个公式,工艺不同tox不同,一般sansen认为 tox=Lmin/50 但是也不尽然 |

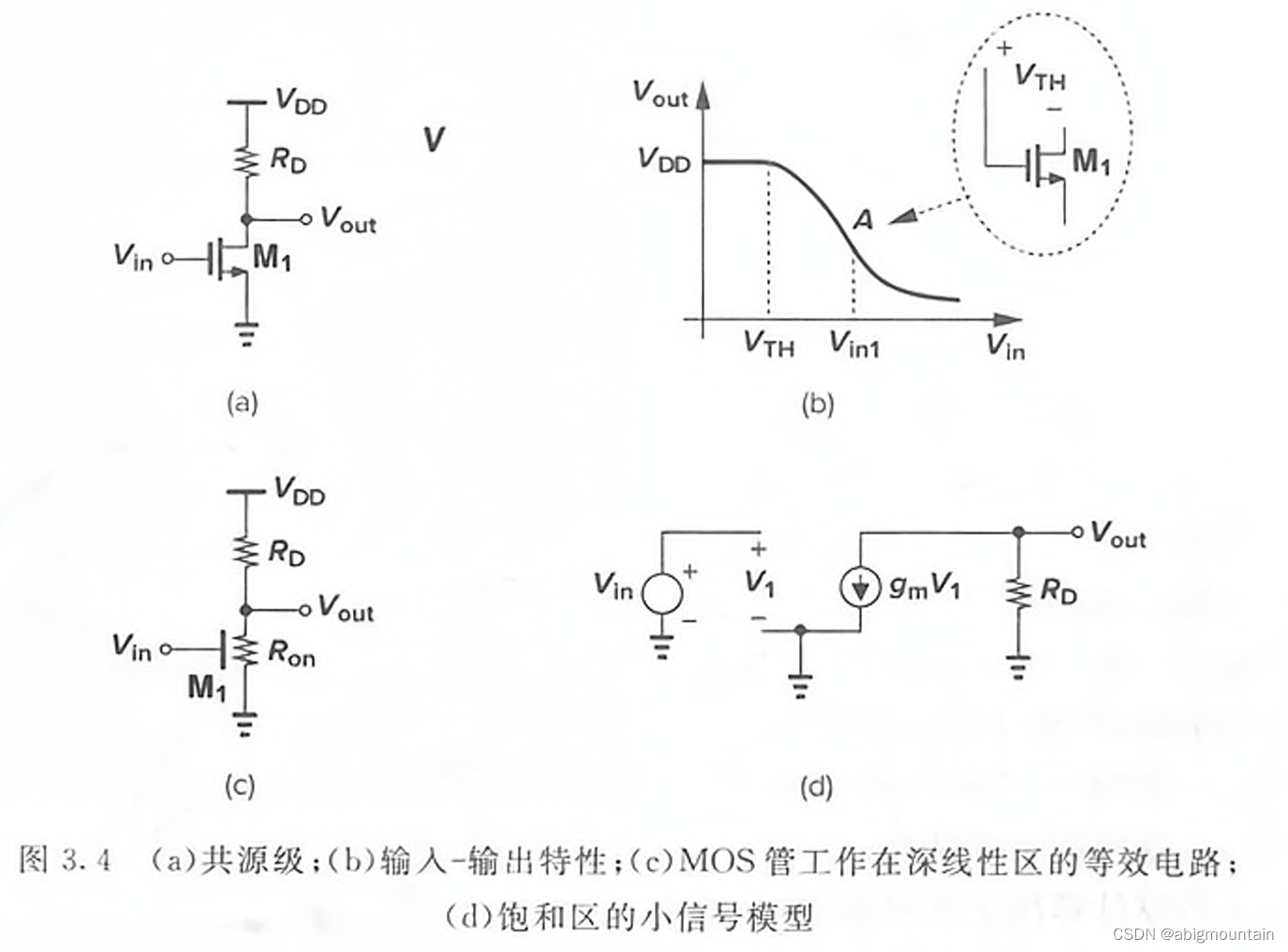

一、共源级(G输入,D输出)

共源级作用:借助于自身的跨导,MOS 管可以将栅-源电压的变化转换成小信号漏极电流,小信号漏电流流过电阻就会产生输出电压。

Vgs→Id→Vout

1.1 采用电阻做负载的共源级

特点:电路的输入阻抗在低频时非常高。

Av=-gm*RD

(考虑了沟道长度调制效应)

1.1.1讨论如何使共源级的增益达到最大值

①提高W/L,较大的器件尺寸会导致较大的器件电容;

②增大,较高的

会限制最大电压摆幅;

③减少,由于

导致RD增大。输出结点的时间常数

增大。

综上,需要在增益、带宽和电压摆幅之间进行折中。

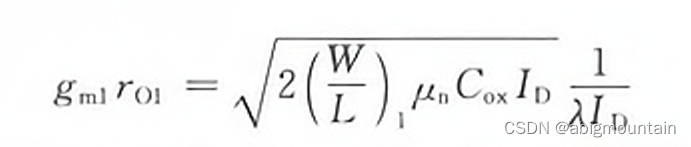

1.1.2本征增益

这个量代表用单个器件能够得到的最大电压增益。短沟道器件的Av大约在5-10。

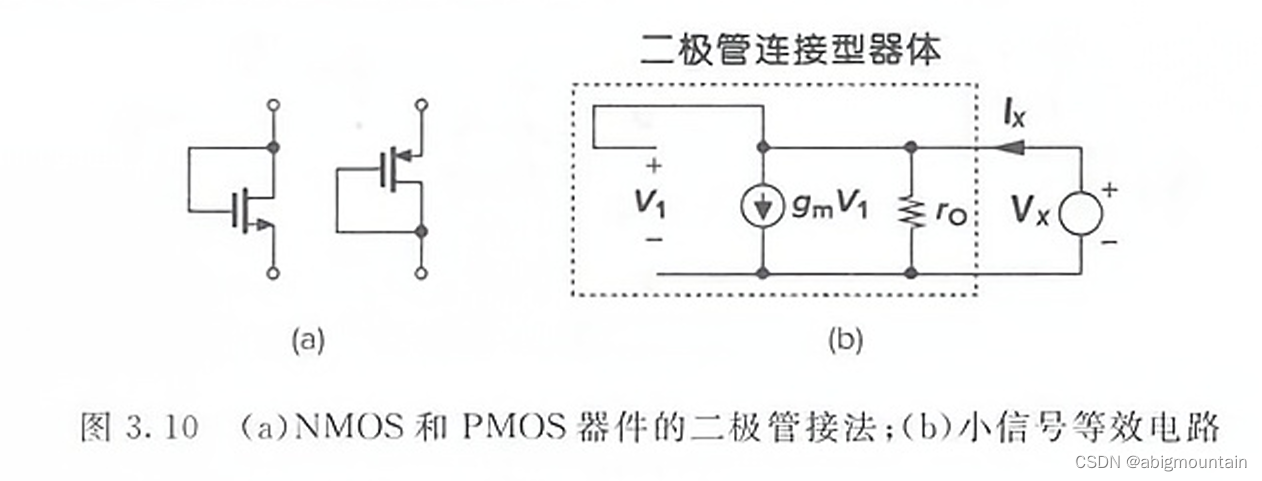

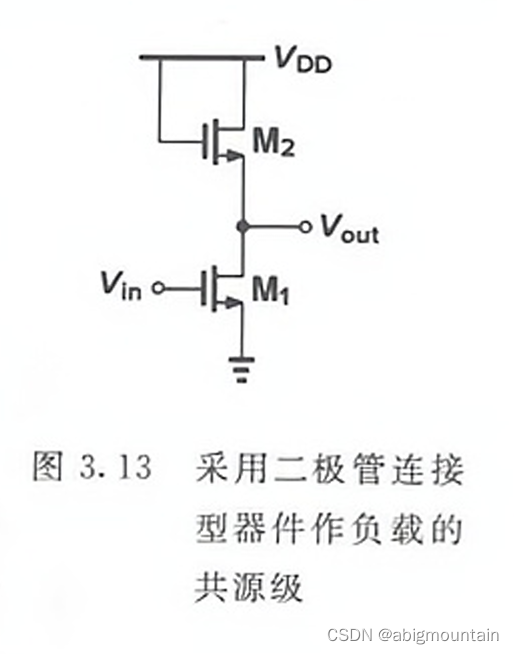

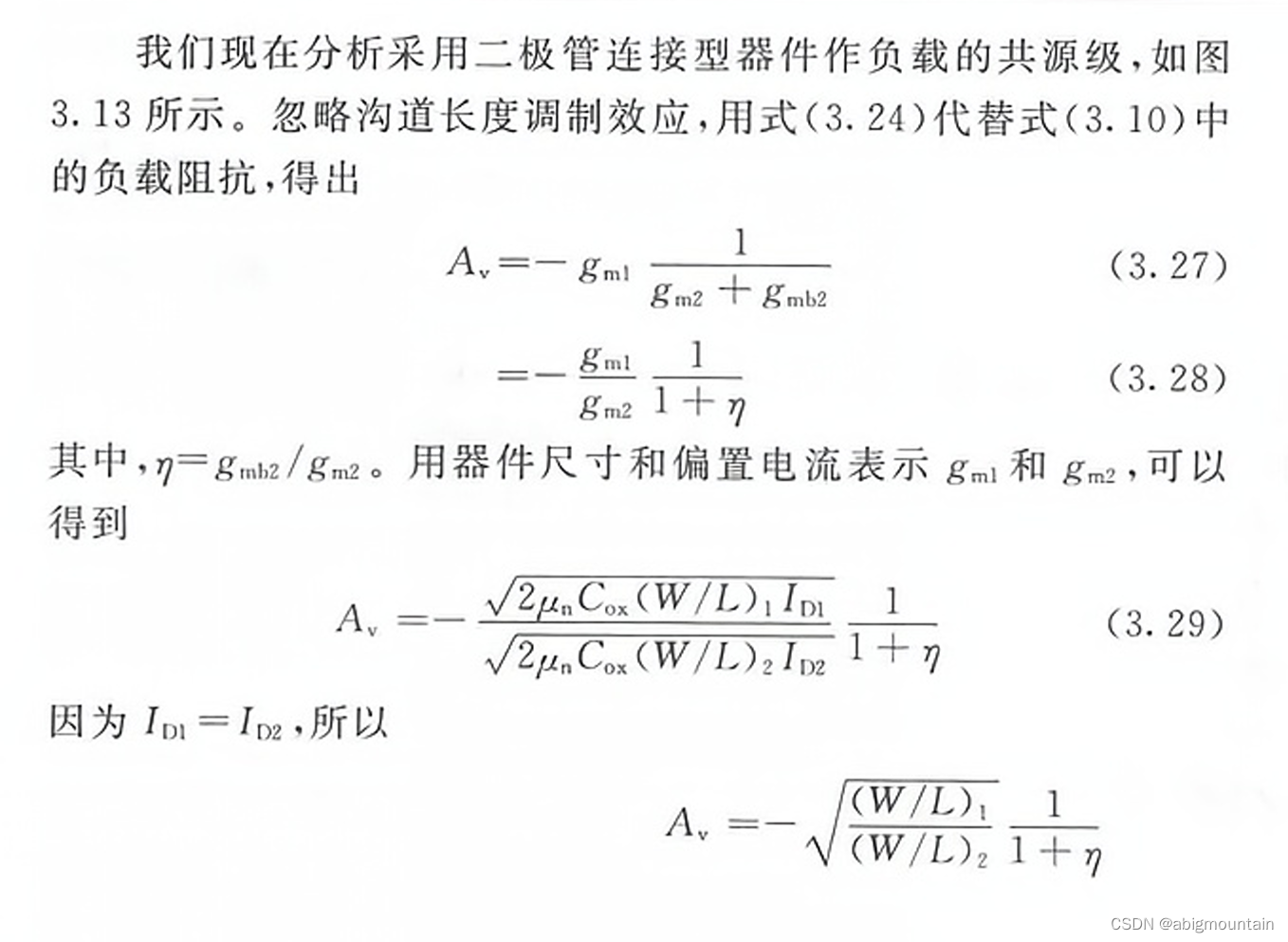

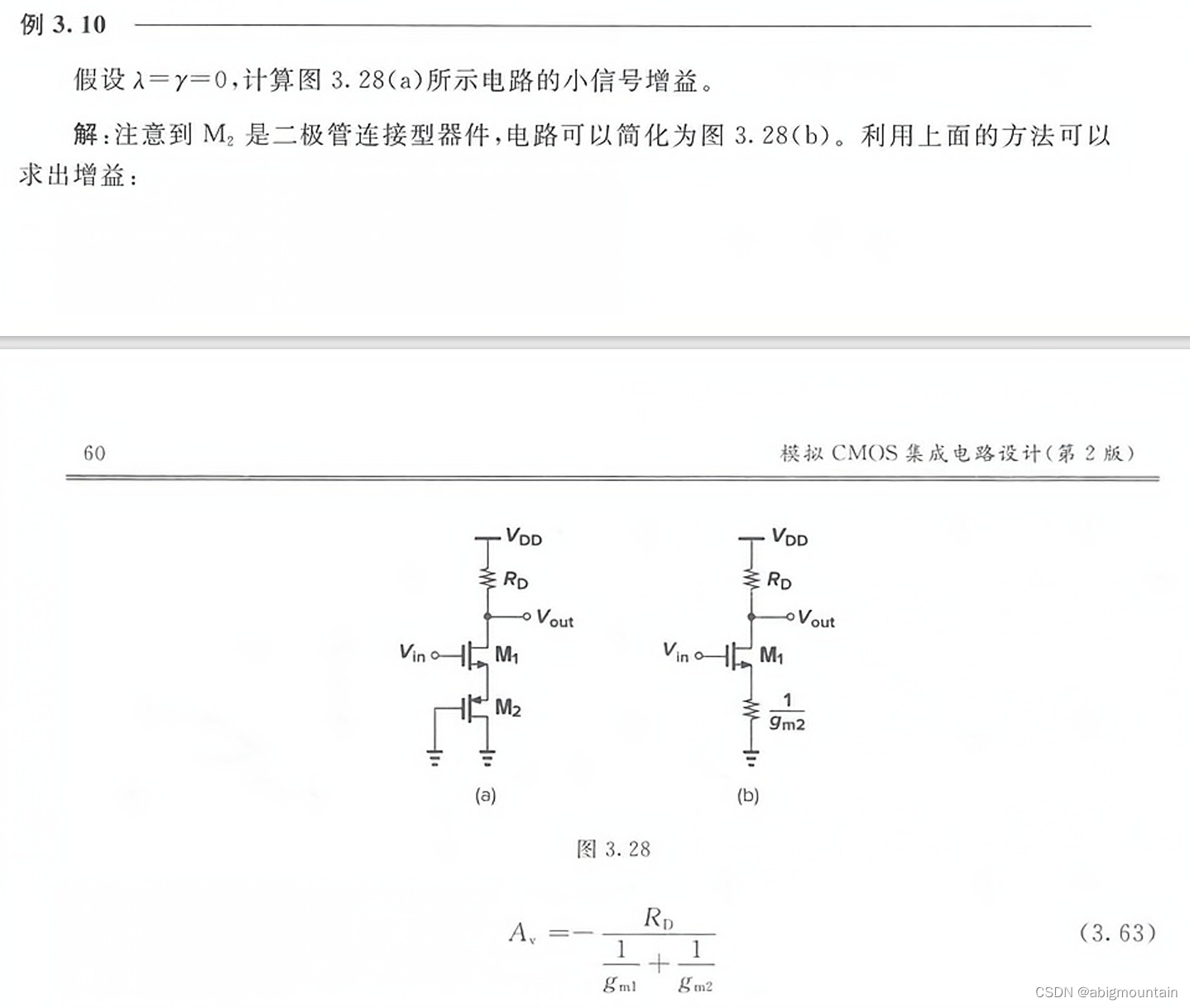

1.2采用二极管连接型器件作负载的共源级

特点:把晶体管的栅极和漏极短接,这个 MOS 器件可以起一个小信号电阻的作用。

(

)

(

)

1.2.1采用PMOS二极管连接型器件做负载的共源级

优点:如果忽略

优点:如果忽略随输出电压的变化,增益和偏置电压或电流没有关系(只要 MOS 管工作在饱和区)。也就是说,当输入和输出电平发生变化时,增益相对保持不变,这表明输入-输出特性呈线性。

缺点:①高增益除了会造成晶体管的图形不均衡(太宽或太长,从而导致大的输入或者负载电容)

②允许的输出电压摆幅的减小(Vgs2会相应增大,导致Vout=VDD-Vgs2 减小)。

摆幅同时受所需的过驱动电压和闽值电压两方面的约束。也就是说,即使过驱动电压很小,输出电平也不会超过 VDD-|VTH|

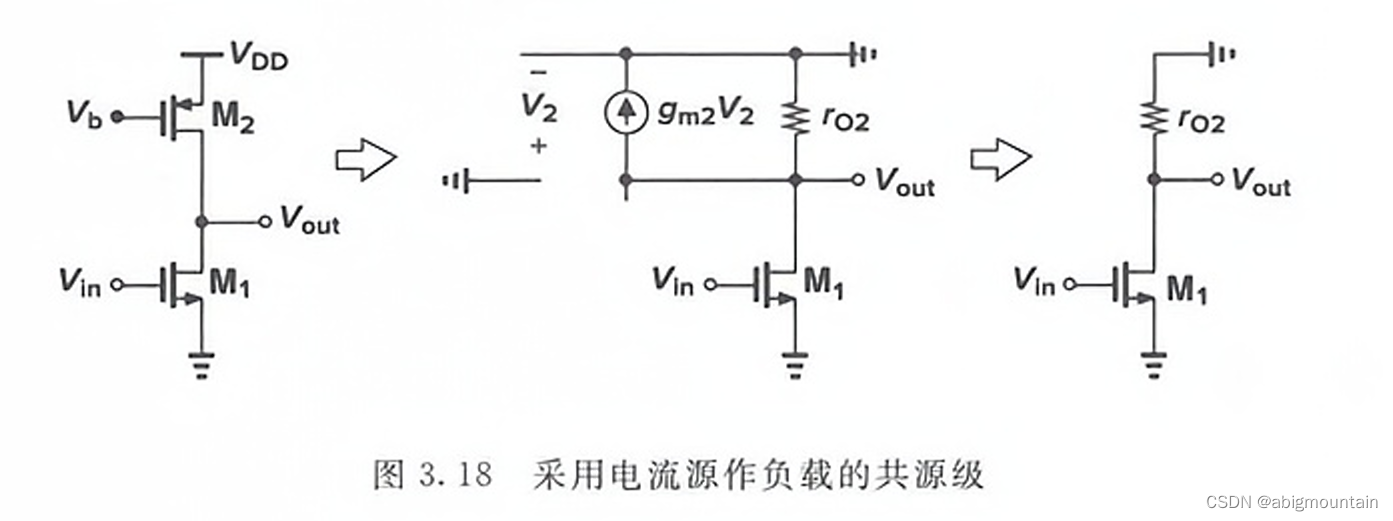

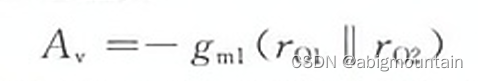

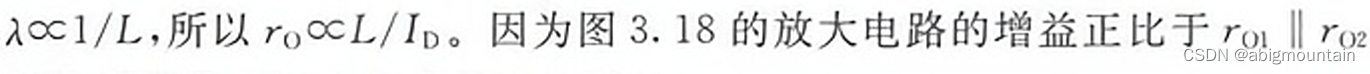

1.3采用电流源作负载的共源级

有时要求单级有很大的电压增益,根据Av=-gm*RD,我们可以增大共源级的负载电阻。但是对于电阻或者二极管连接的负载而言,增大阻值会消耗直流压降,从而限制输出电压的摆幅。

一个更切实可行的方法是用不服从欧姆定律的器件,如电流源代替负载。

特点:增加M2的沟道宽度,就可以使电压|VDS2,min=VGS2-VTH2|减小到几百毫伏。如果 ro不够大,在保持相同的过驱动电压的同时增大 M2的长和宽可以获得比较小的。代价是 M2在输出结点引人了大的电容。

长沟道器件可以产生高的电压增益。

缺点:电流源负载共源级的输出摆幅较小:

缺点:电流源负载共源级的输出摆幅较小:

优点:但若增加L,它总能得到较高的增益 。

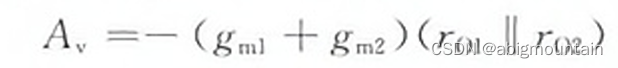

1.4有源负载的共源级(互补共源级)

特点:将M2的栅极也作为输入端,产生了更高的增益。

缺点:①两个晶体管的偏置电流是PVT的强函数,VDD或者阈值电压的变化会直接转换为它们的漏电流的变化;

②电路会放大电源电压的变化电源噪声。

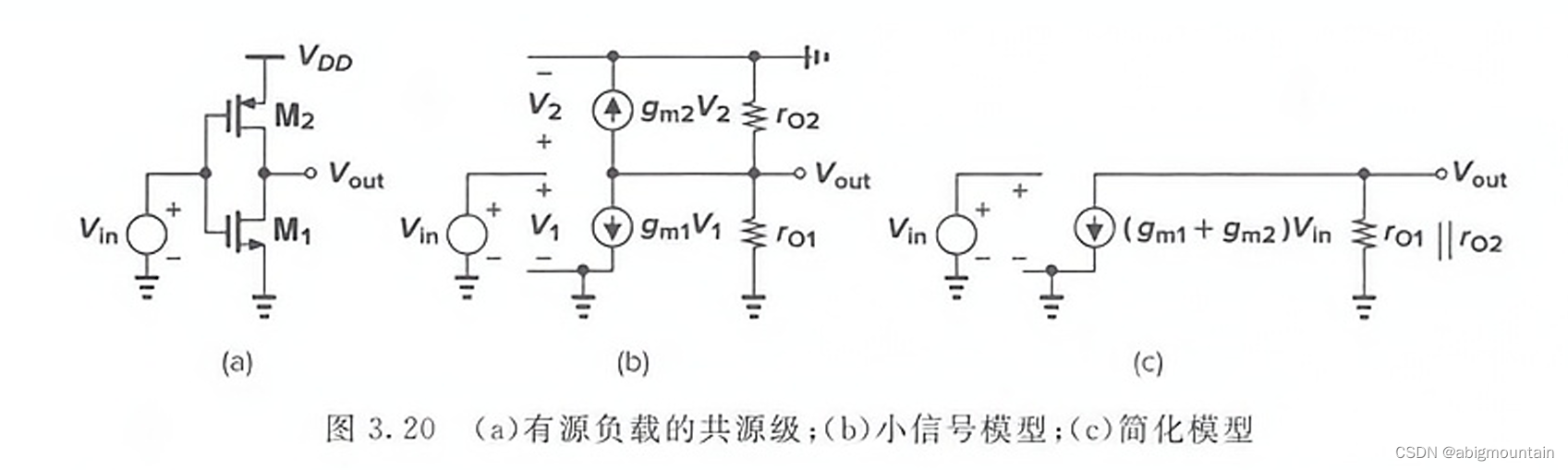

1.5工作在线性区的MOS为负载的共源级

特点:可作为电阻

缺点:

优点:

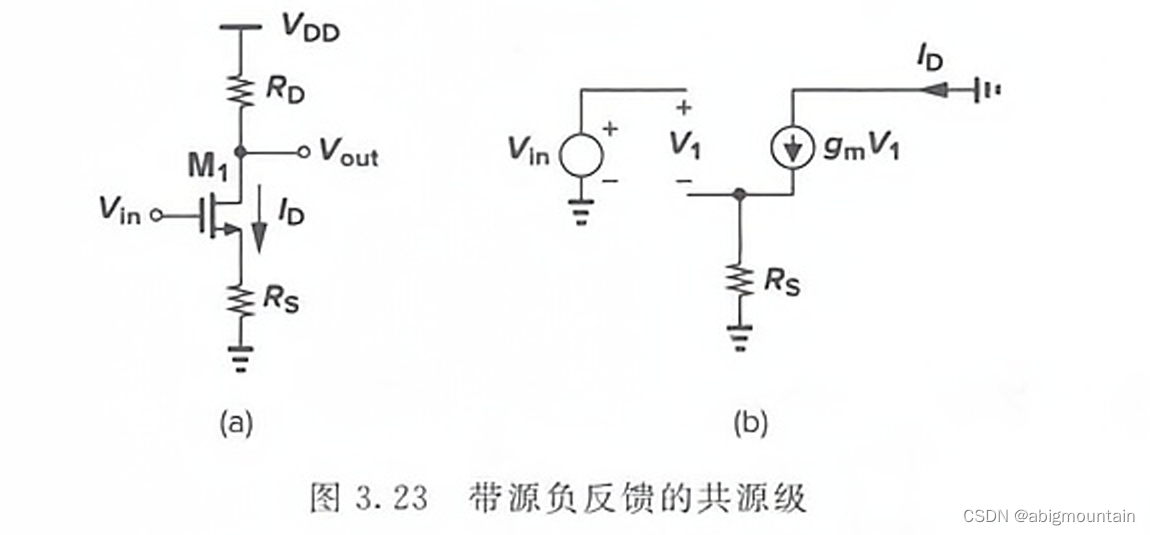

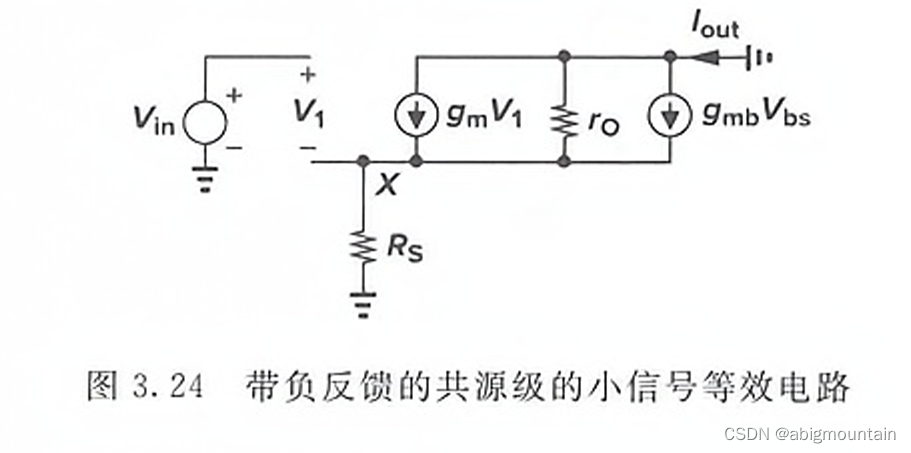

1.6带源级负反馈的共源级

特点:在一些应用中,由于漏电流与过驱动电压之间的非线性关系引入大量的非线性,因此,人

们希望“软化”器件的这种非线性关系。

优点:①在晶体管的源端串联一个“负反馈”电阻,以使输入器件更加线性。

②增大共源级的输出阻抗。

缺点:牺牲增益和高的噪声。

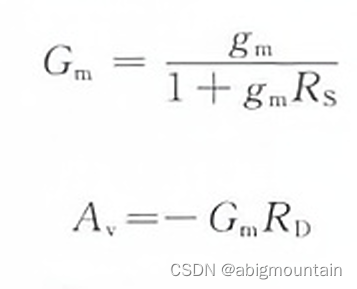

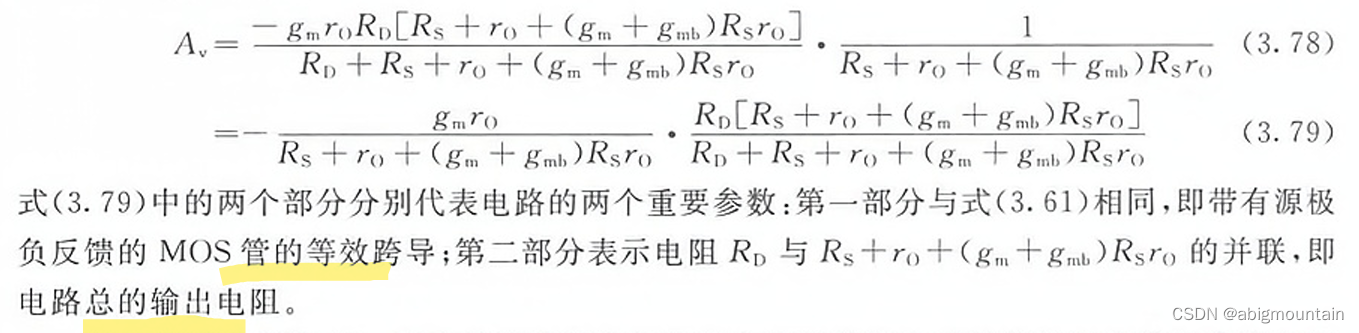

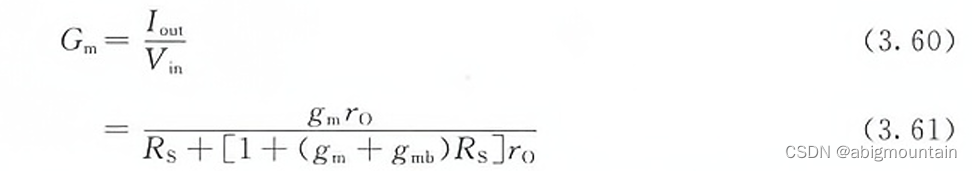

1.6.1GM和Av

考虑体效应和沟道长度调制效应后,

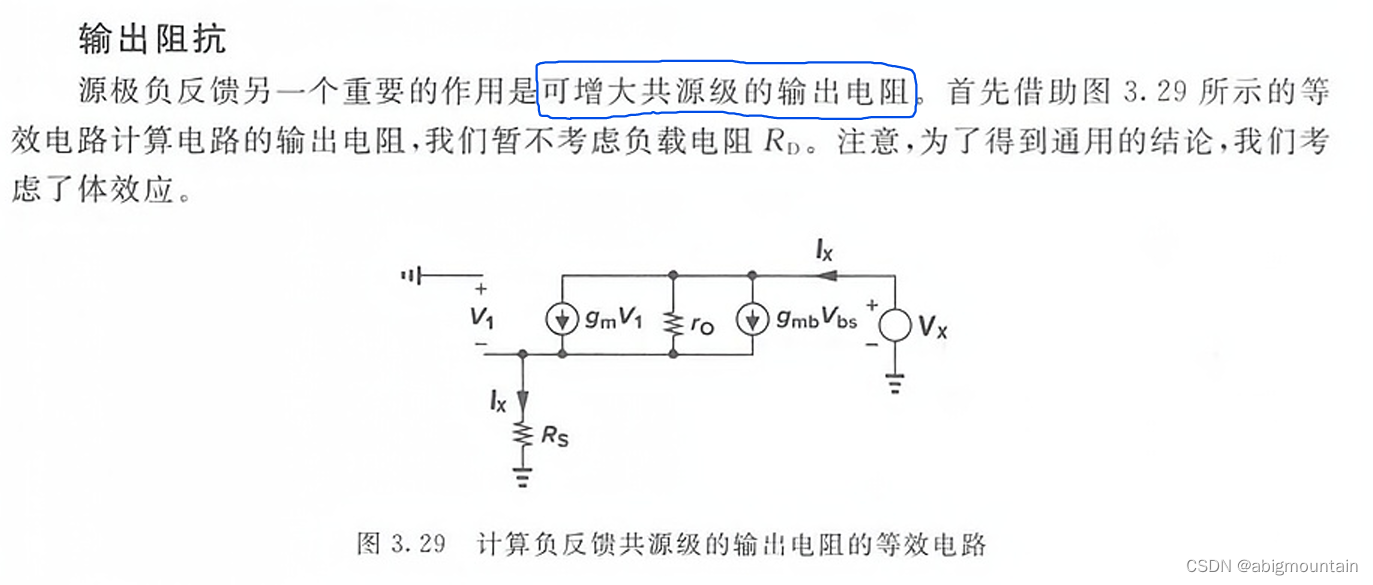

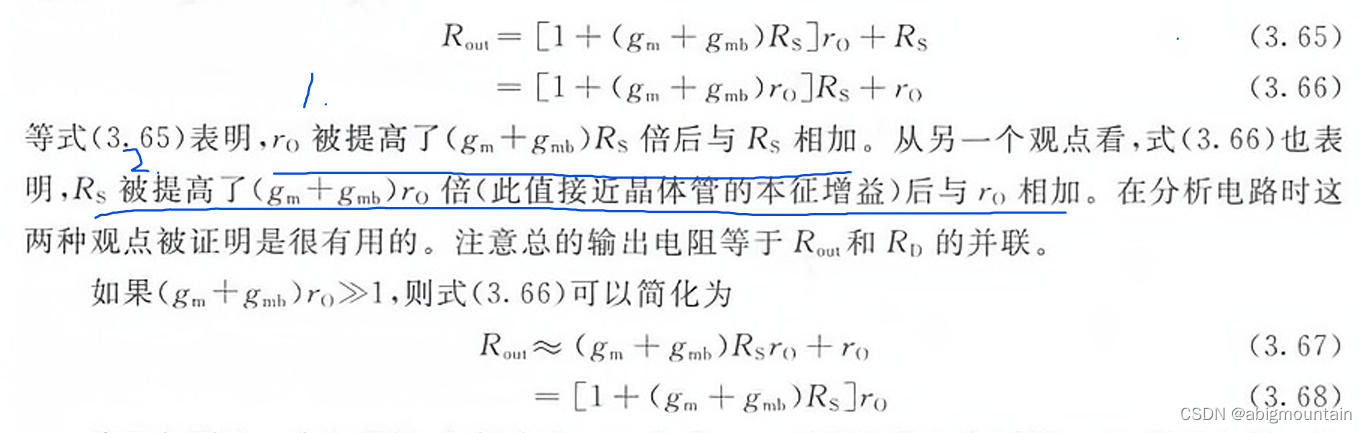

1.6.2输出阻抗

如果加了负载RD后,

以上式子得到原因

1.7共源级总结

| 采用电阻作负载 | 将Vgs转换为ID,然后在利用电阻转化为Vout输出 |

| 采用二极管连接型器件作负载 | 负载用MOS管(饱和区)作为电阻 |

| 采用电流源作负载 | 提供较大增益 |

| 有源负载 | 提供比“采用电流源作负载”更大的增益,缺点也更明显 |

| 工作在深线性区的MOS为负载 | 作为电阻,缺点很多 |

| 带源级负反馈 | 使得Vgs-ID关系更线性化,增大输出阻抗。增益不太高,噪声大 |

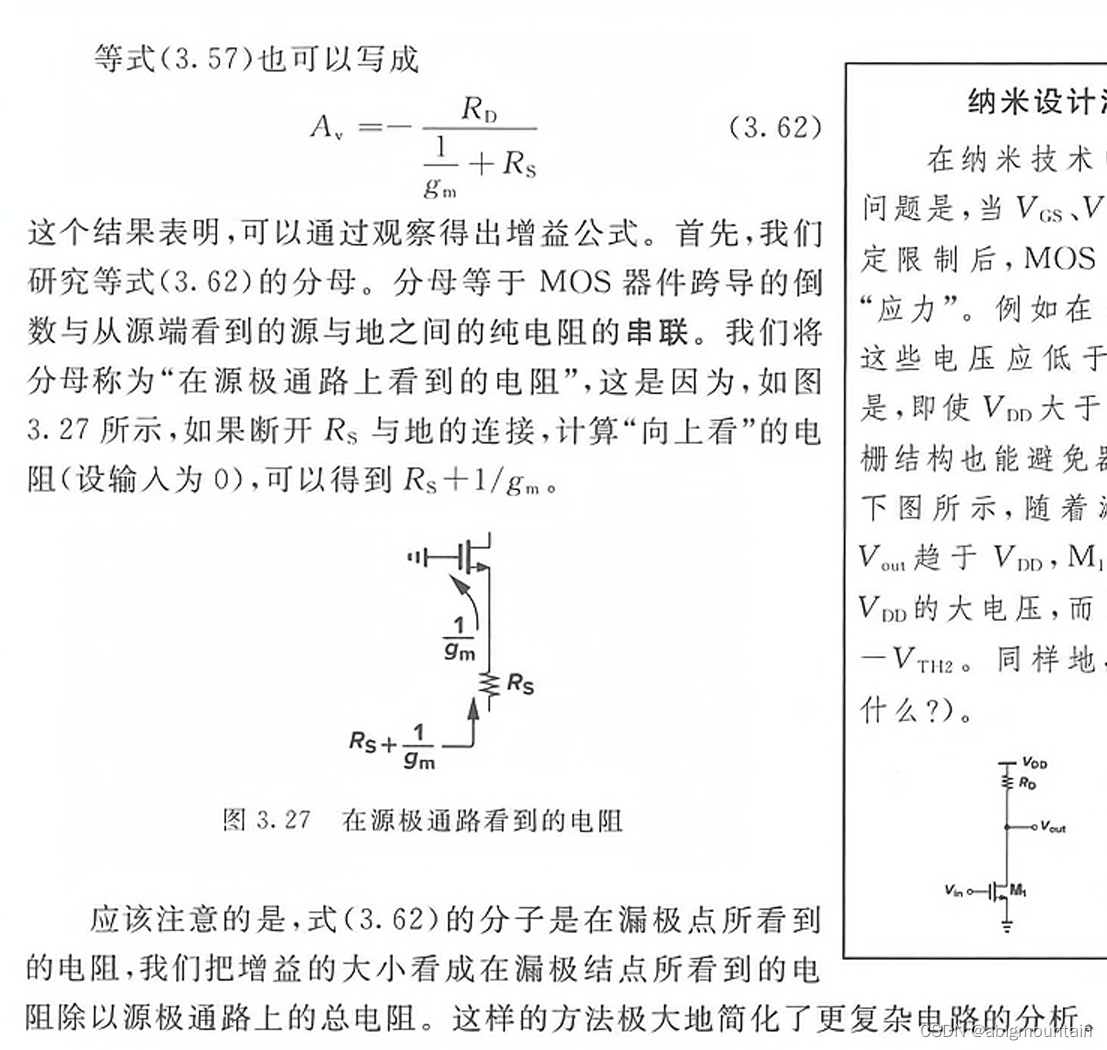

1.8观察法看出增益公式

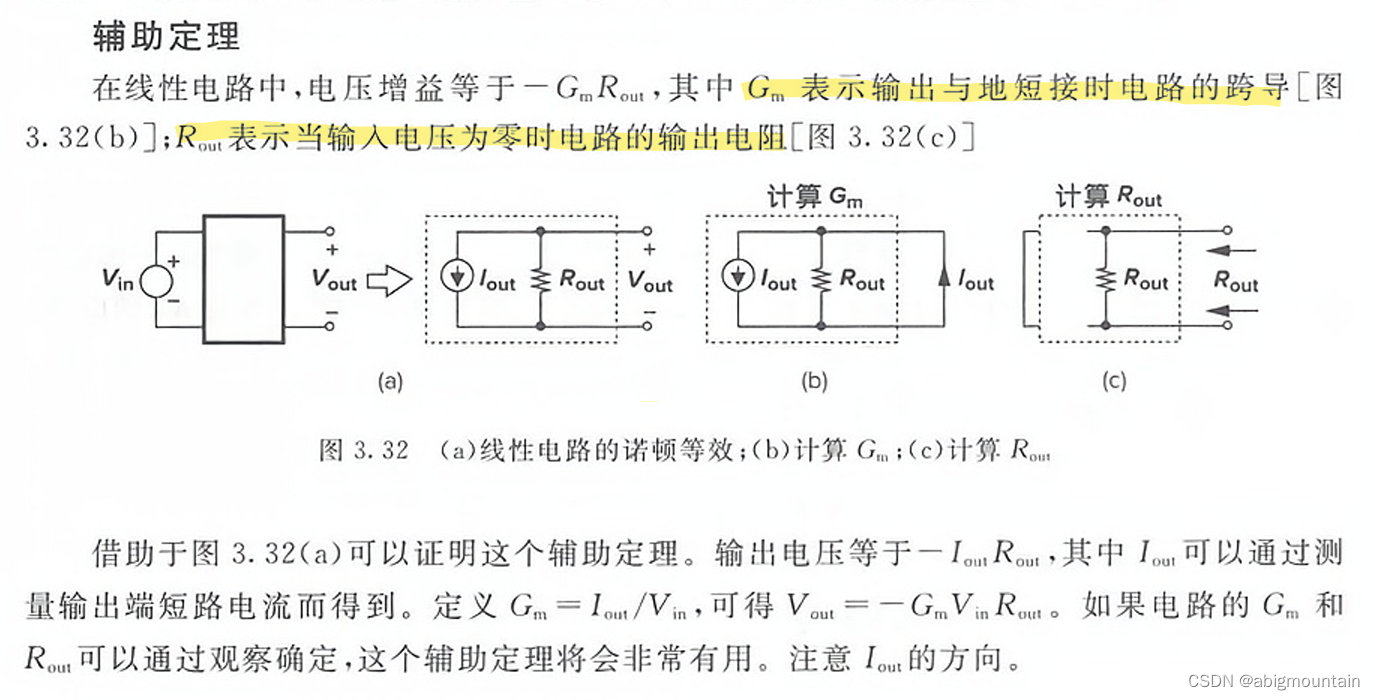

1.9辅助定理

Av=-Gm*Rout

可根据(3.61)确定Gm,(3.66)确定Rout

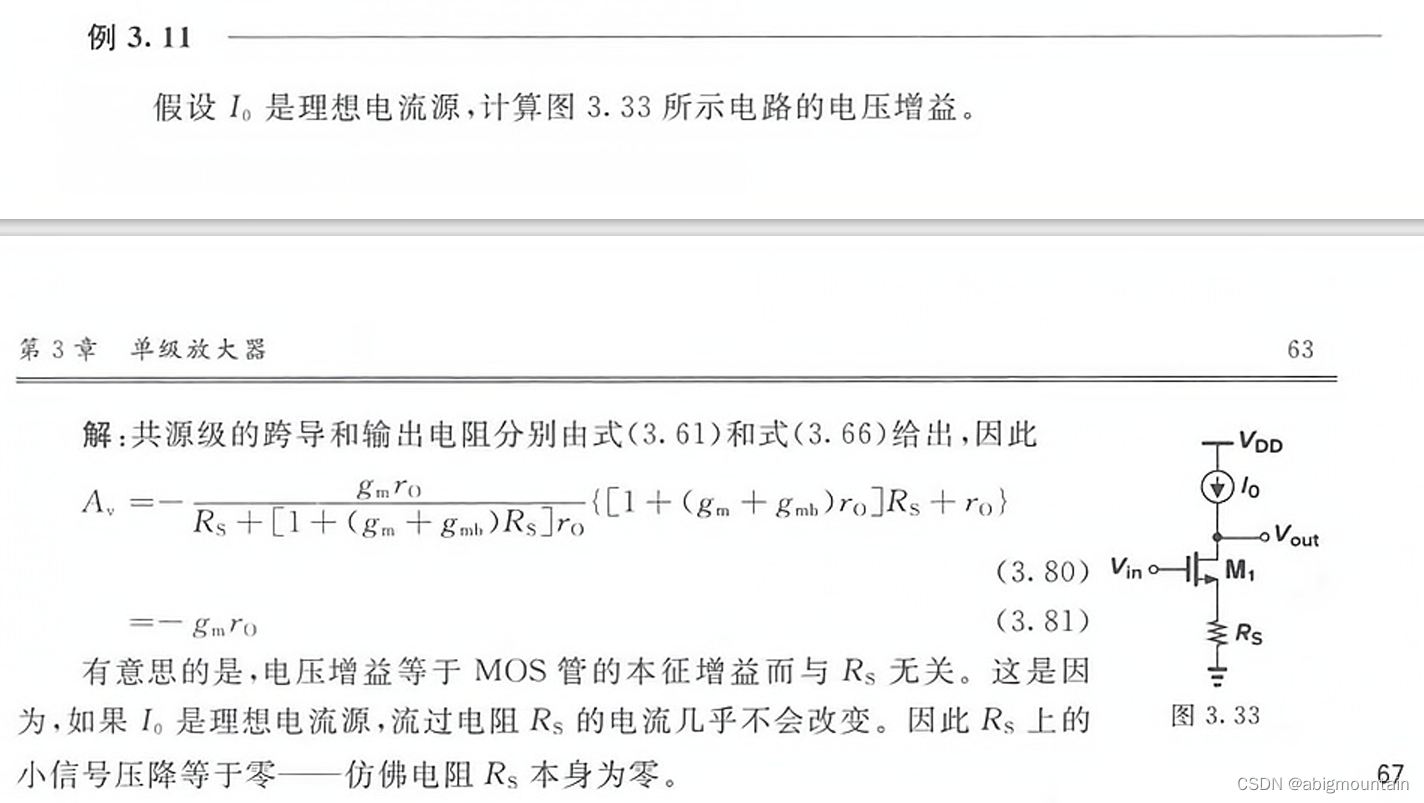

例题

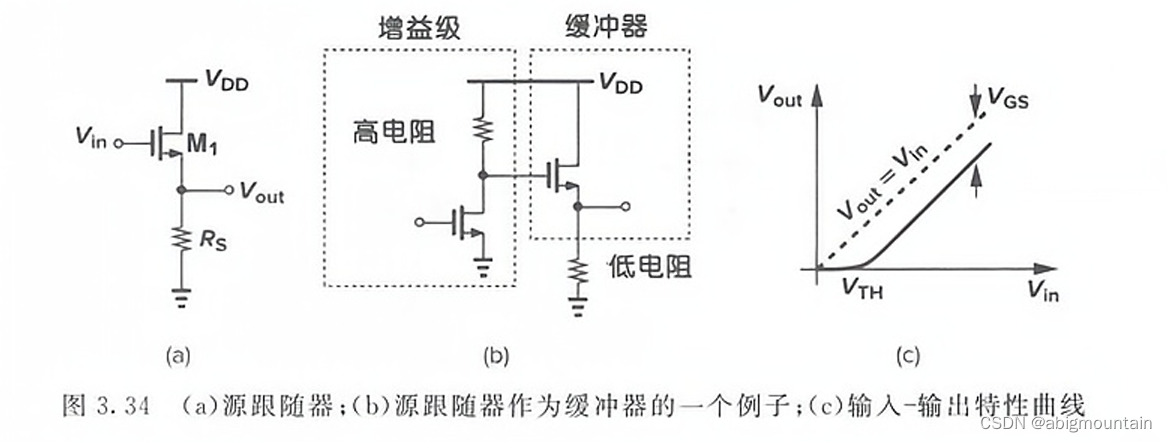

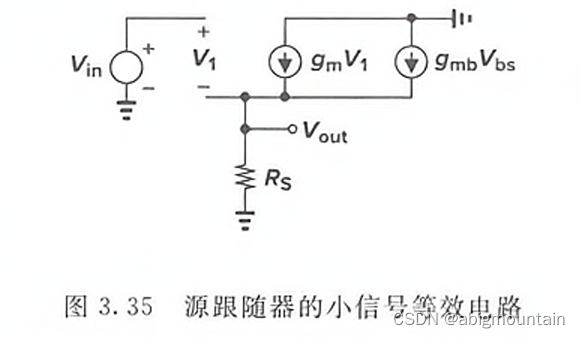

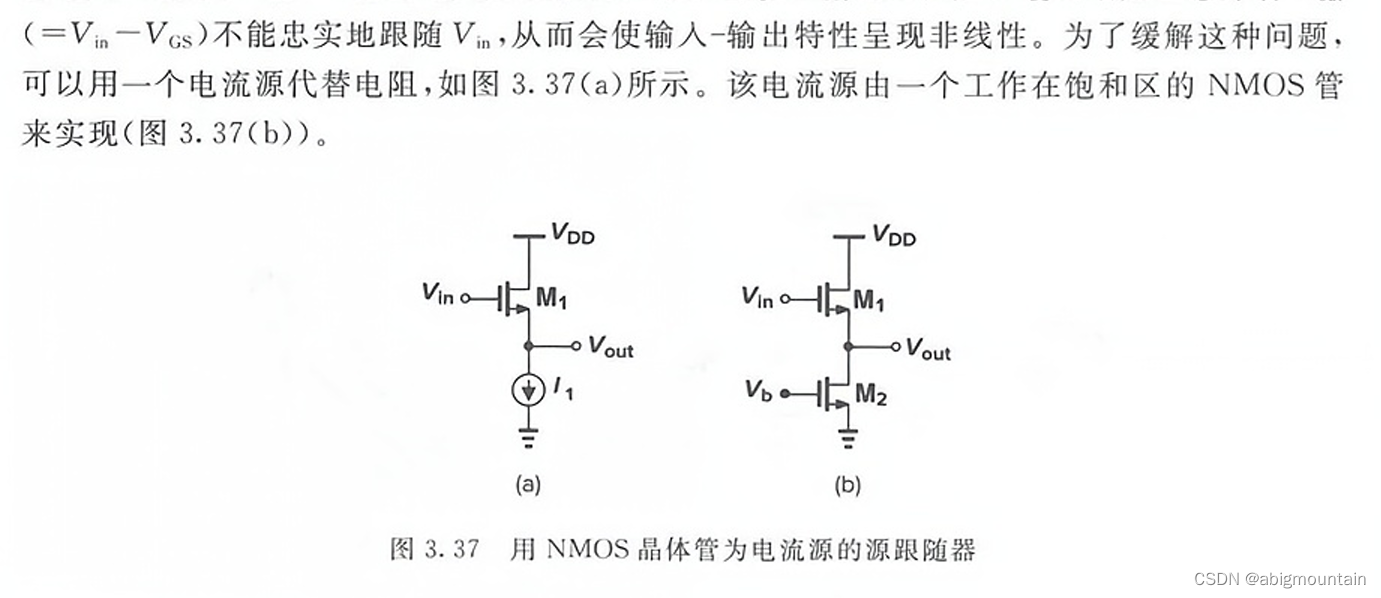

二、源跟随器(G输入,S输出)

预期目标,Vout随着Vin线性变化。

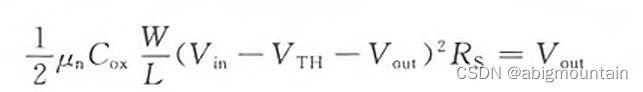

2.1负载为电阻Rs

Vgs=Vin-Vout

但是Vgs随Id影响大,Vgs会变化导致Vout随着Vin非线性变化。以下为原因:

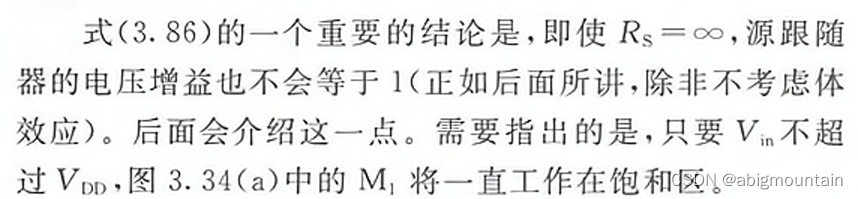

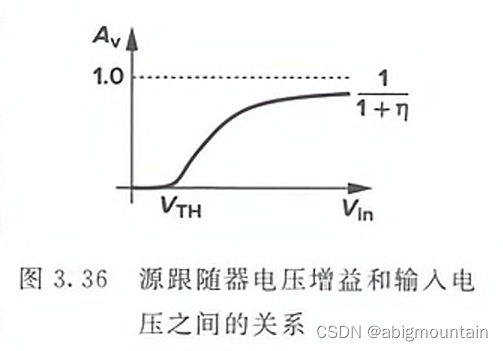

2.1.1Av原理分析:

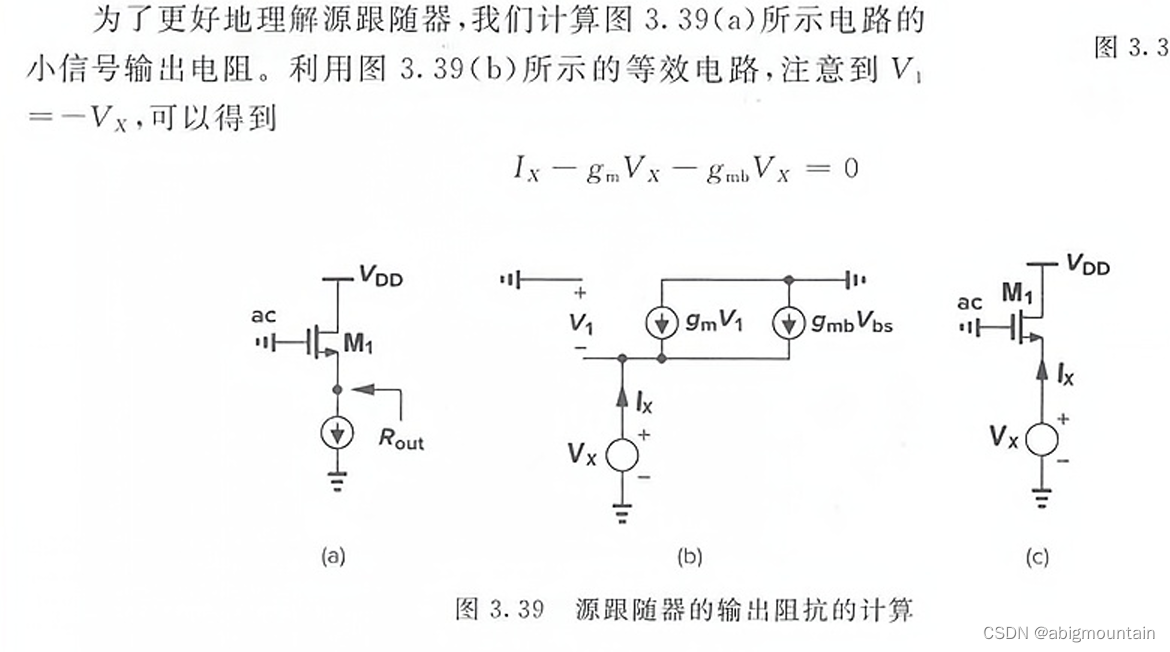

2.1.2计算Rout

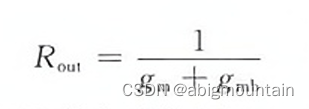

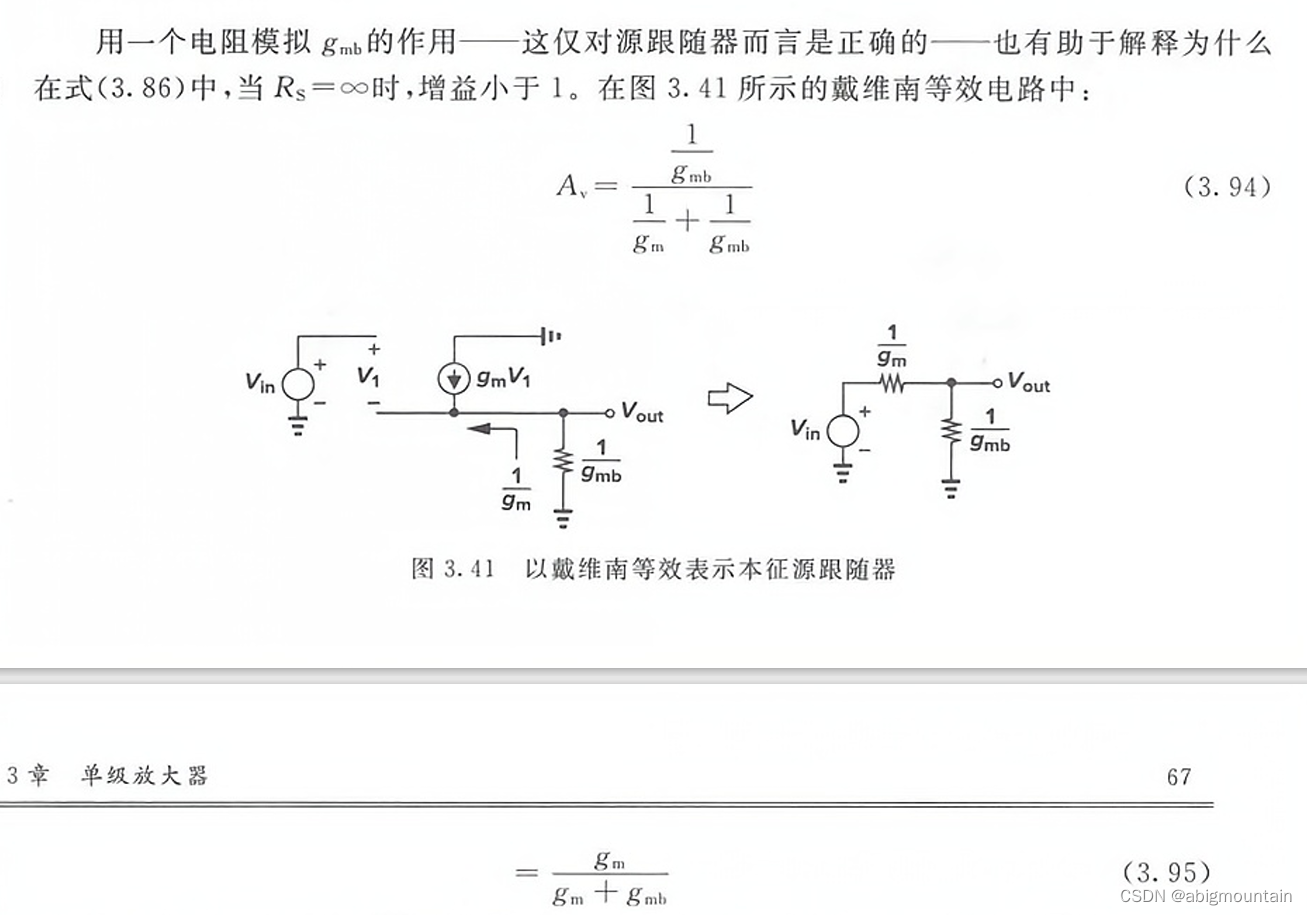

2.1.3戴维南等效电路后算Av(仅对源跟随器的算法)

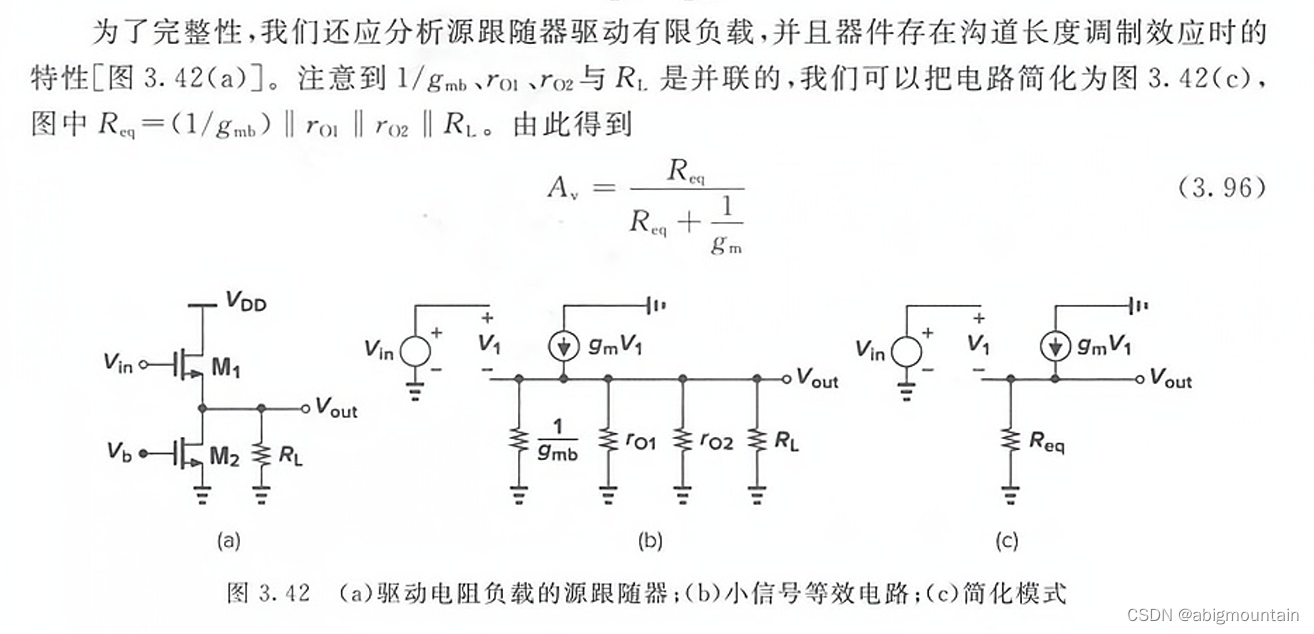

加了负载RL后,并且考虑沟道长度调节效应

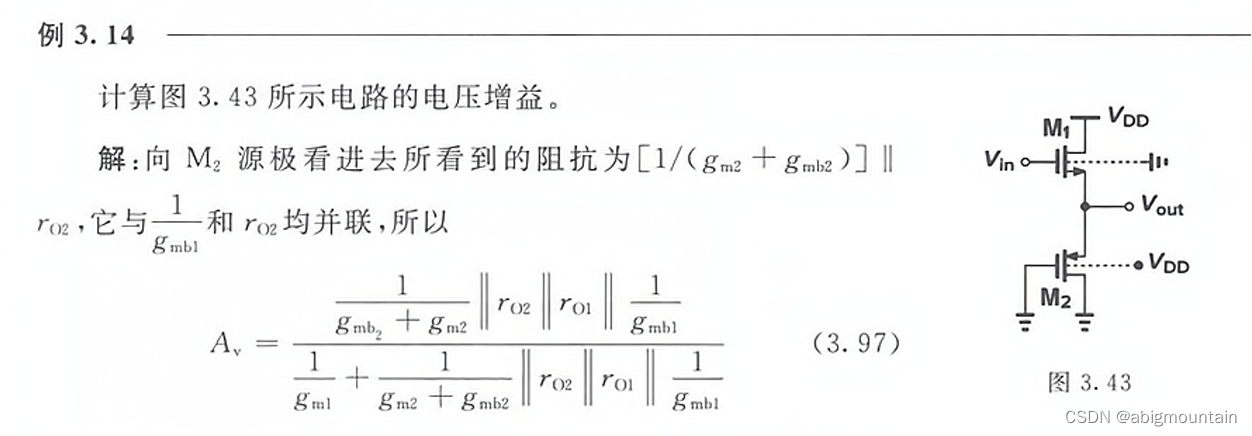

例题

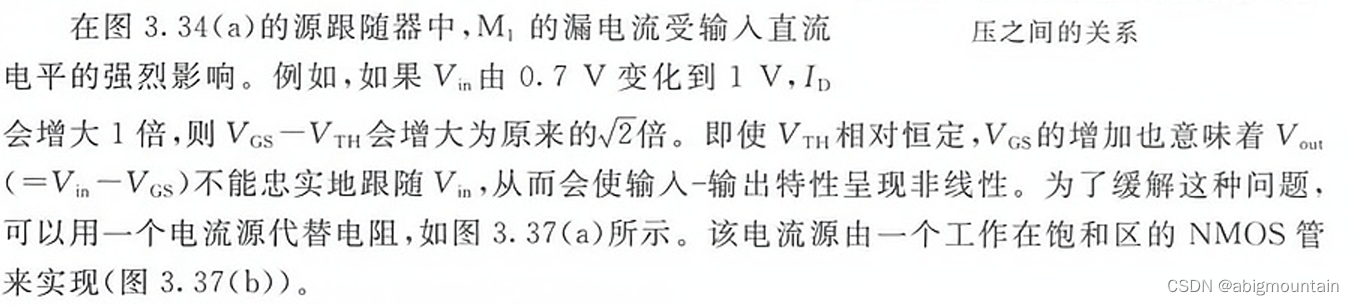

2.2负载为工作在饱和区的电流源代替电阻

目的:让Id保持相对稳定,使得Vgs=Vin-Vout,中的Vgs保持相对不变。

2.3 源跟随器的优缺点

优点:①高的输入阻抗;(查资料说是阻抗接近无穷大?但目前还不知道为什么)

②中等的输出阻抗。

缺点:①体效应和沟道长度调制效应导致的非线性;

A.这源于阈值电压 VTH与源极电压之间的非线性关系(如果把衬底和源接在一起,可以消除由体效应引起的非线性,由于所有的 NMOS管共用一个衬底,仅对PMOS管有效)(PMOS的低迁移率导致它的输出阻抗比NMOS的输出阻抗高。)

B.在亚微米工艺中,晶体管的ro同样随 VDS而显著改变,因此也会给电路的小信号增益带来额外的变化.

②电平移动导致电压余度的减小;

③差的驱动能力;

④引入显著噪声。

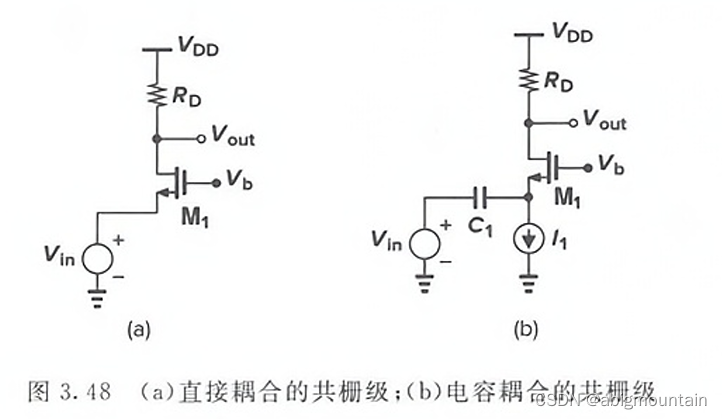

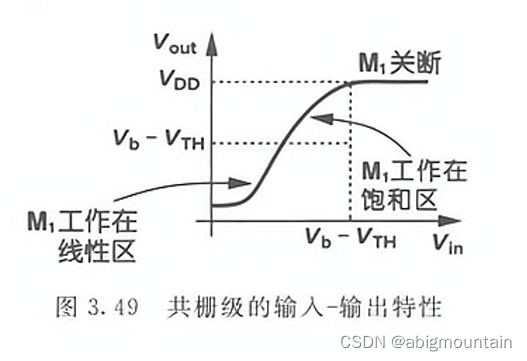

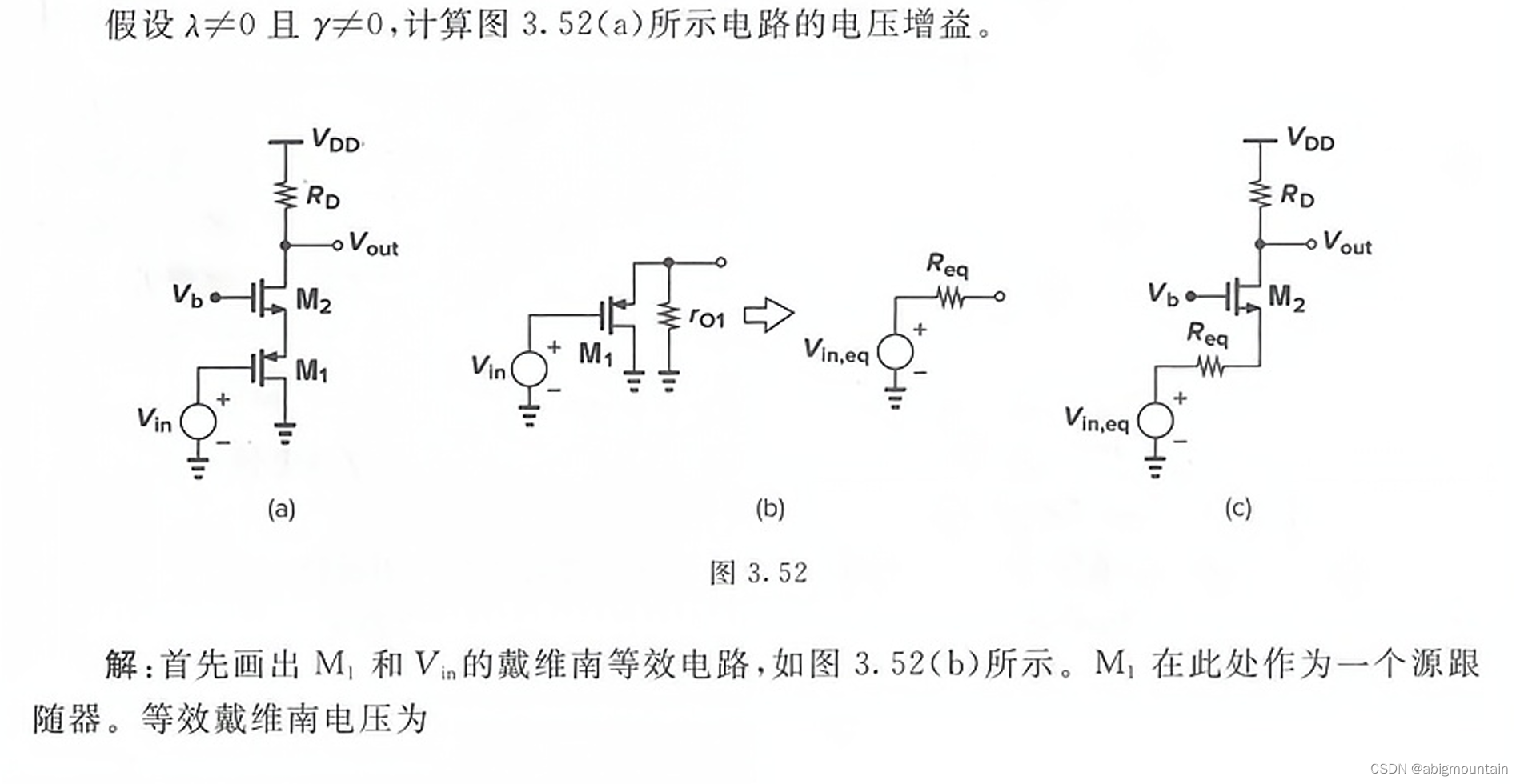

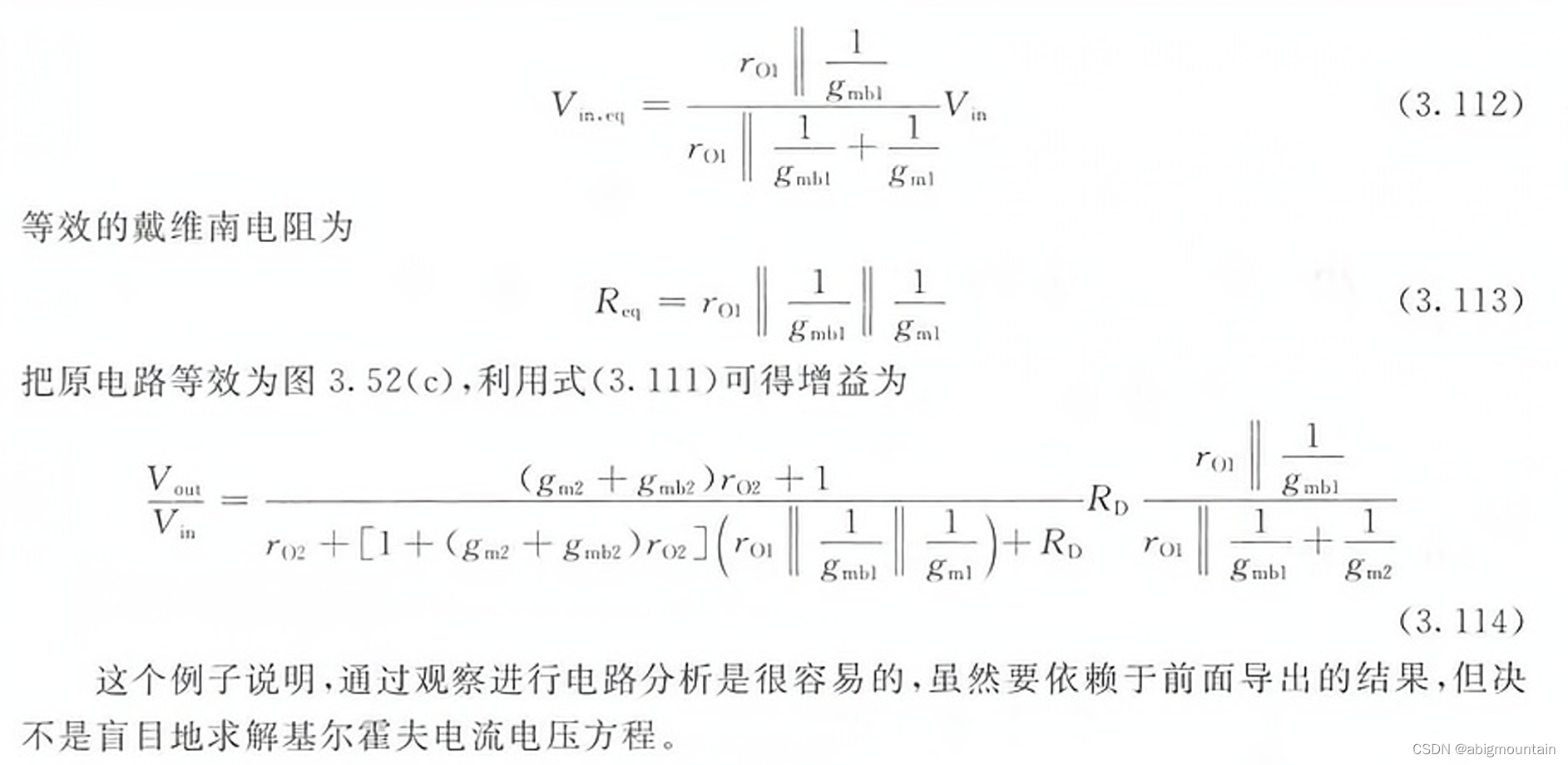

三、共栅极(S输入,D输出)

(a)M1管的偏置电流流过输入信号源;(b)M1管用一个恒流源来偏置,信号通过电容耦合到电路

对3.48(a):

共栅极的增益:

3.1观察法算增益(以共源共栅极为例)

类似于(3.96)的公式 ,2.1.3里面的

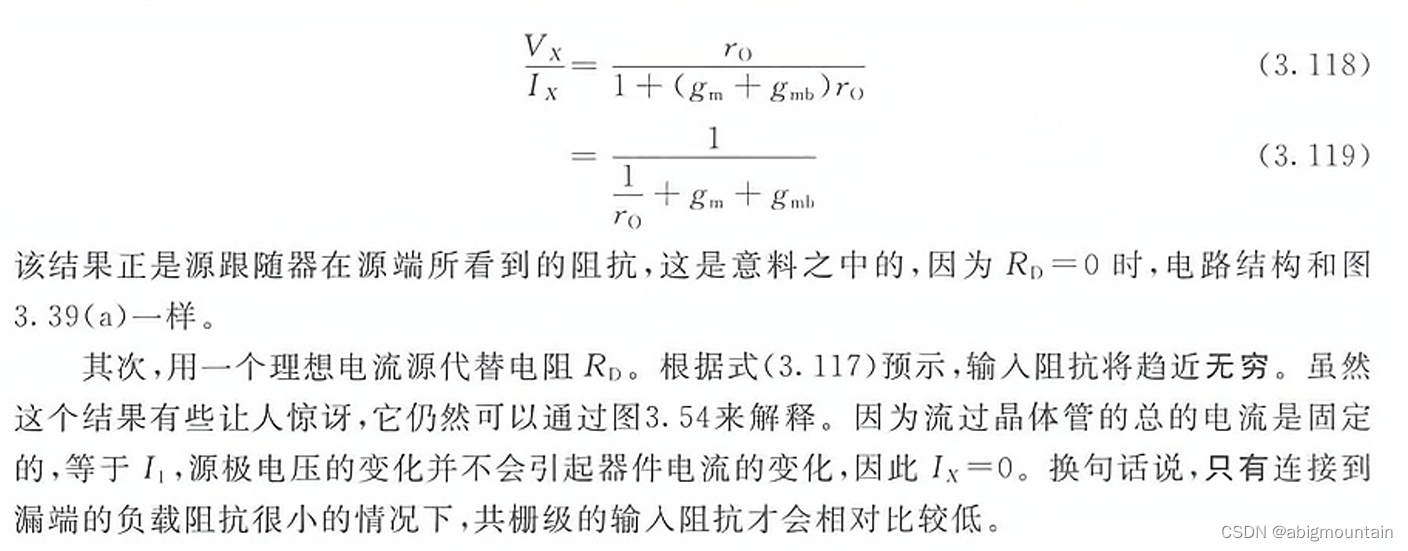

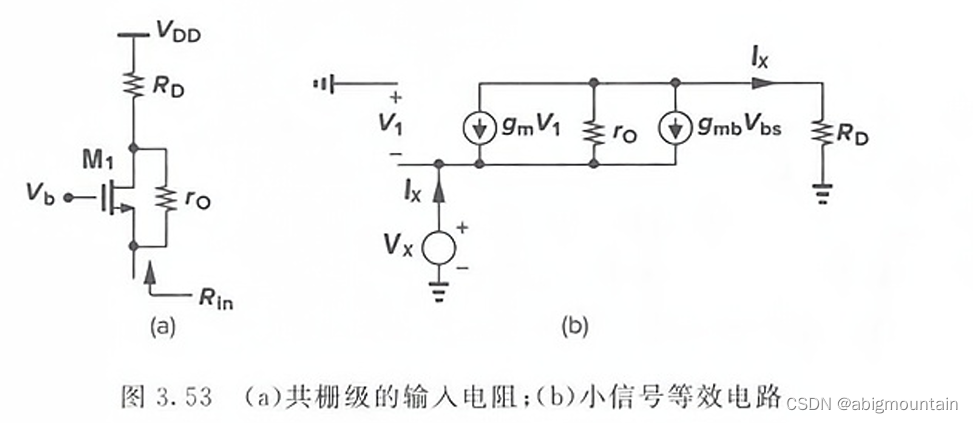

3.2输入输出阻抗

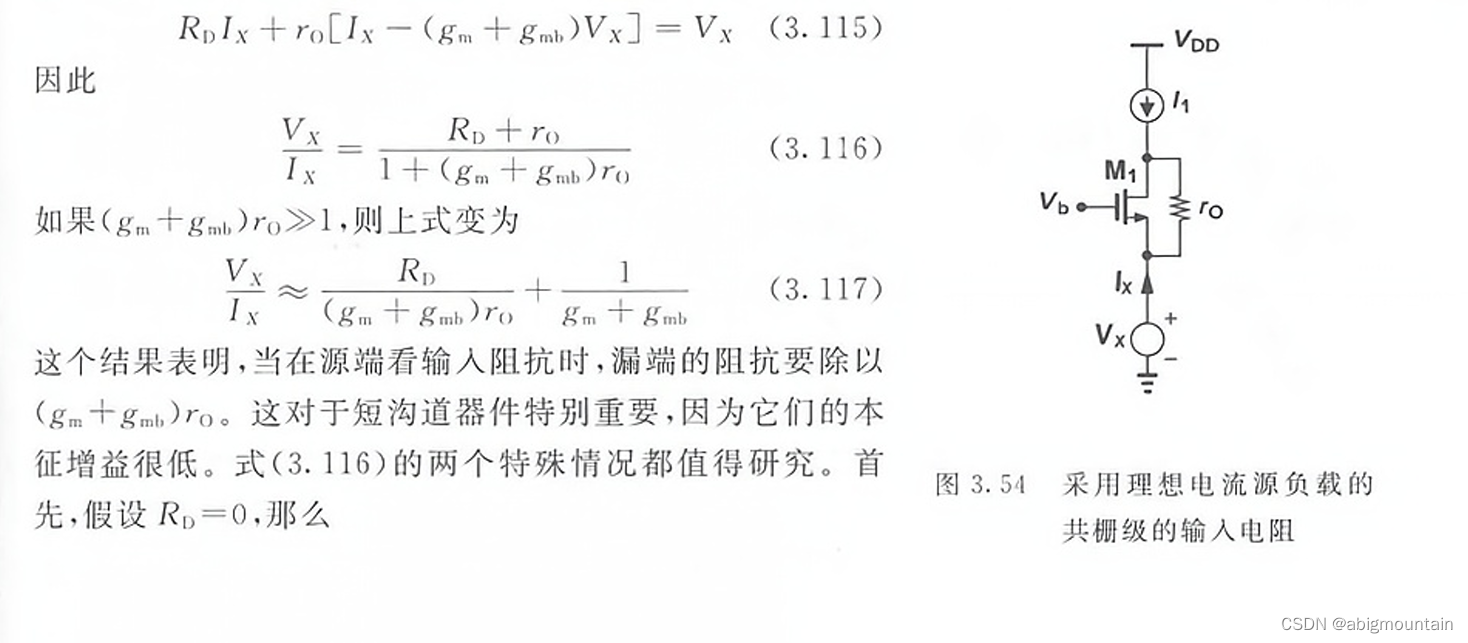

3.2.1输入阻抗

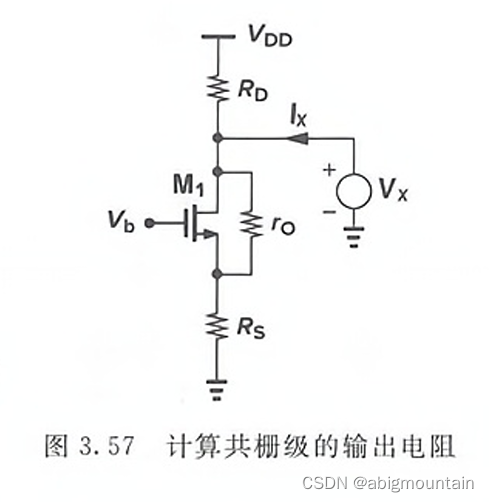

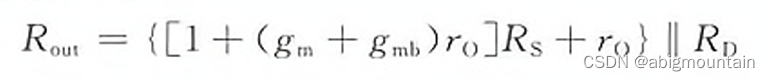

3.2.2输出阻抗

3.2.2输出阻抗

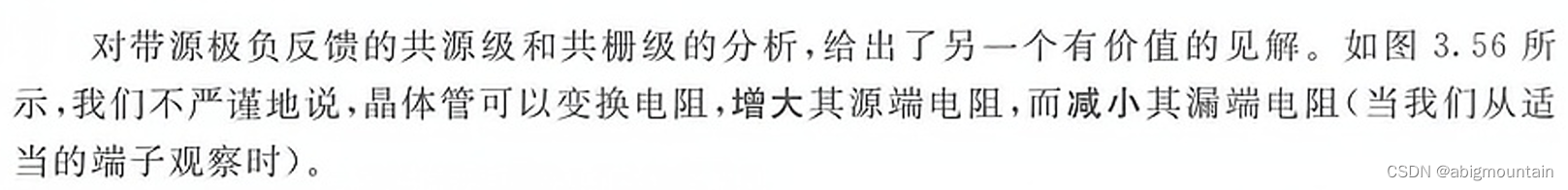

3.2.3MOSFET的阻抗变换(这点的作用还不太懂)

3.2.3MOSFET的阻抗变换(这点的作用还不太懂)

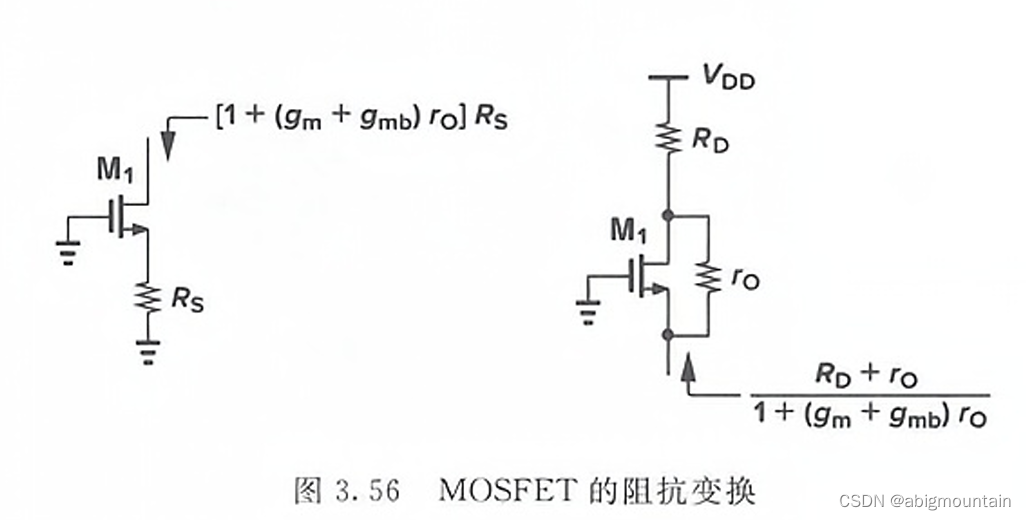

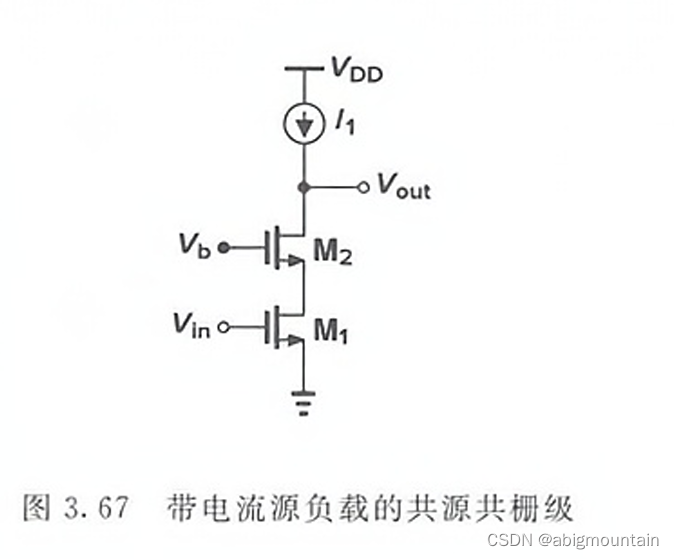

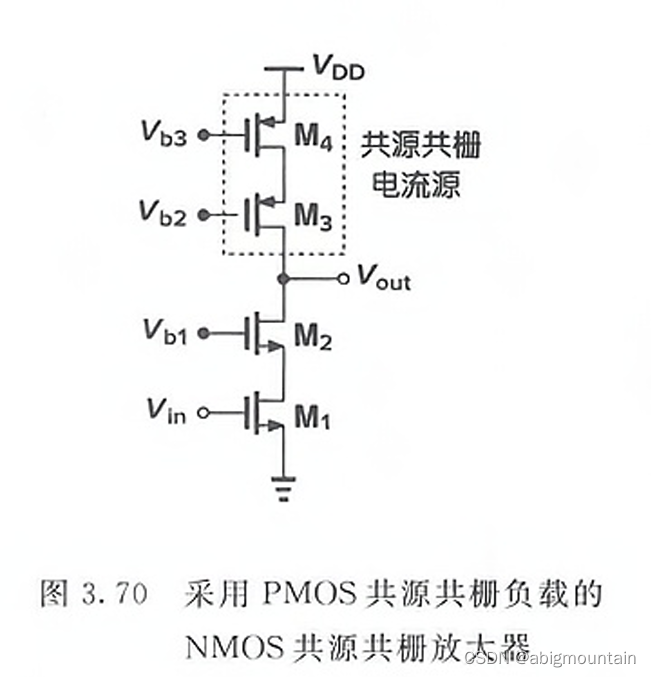

四、共源共栅极 cascode(共源级S输入,共栅极D输出)

4.1套筒式共源共栅

因为输入器件产生的漏电流必定流过共源共栅器件,所以电压增益与共源级的电压增益相同。(都在饱和区,不考虑沟道长度调制效应)

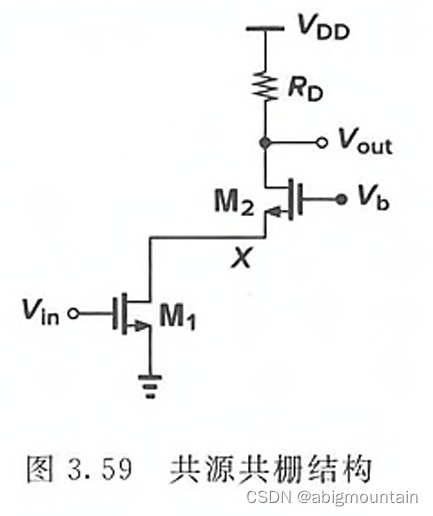

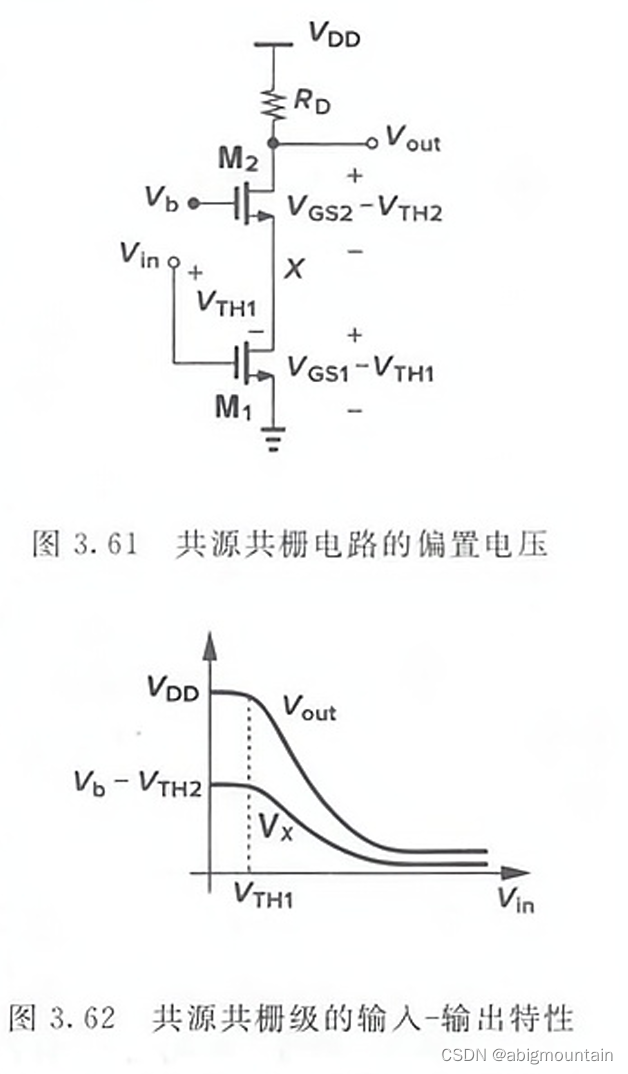

4.1.1偏置条件分析

因此,M1和M2工作在饱和区的最小输出电平等于M1和 M2的过驱动电压之和。换句话说,电路中 M2管的增加会使电路的输出电压摆幅减小,减小的量至少为 M2的过驱动电压。我们也说成 M2“层叠”在 M1上。

也可不严格地讲,最小输出电压为 2个过驱动电压2VD,sat

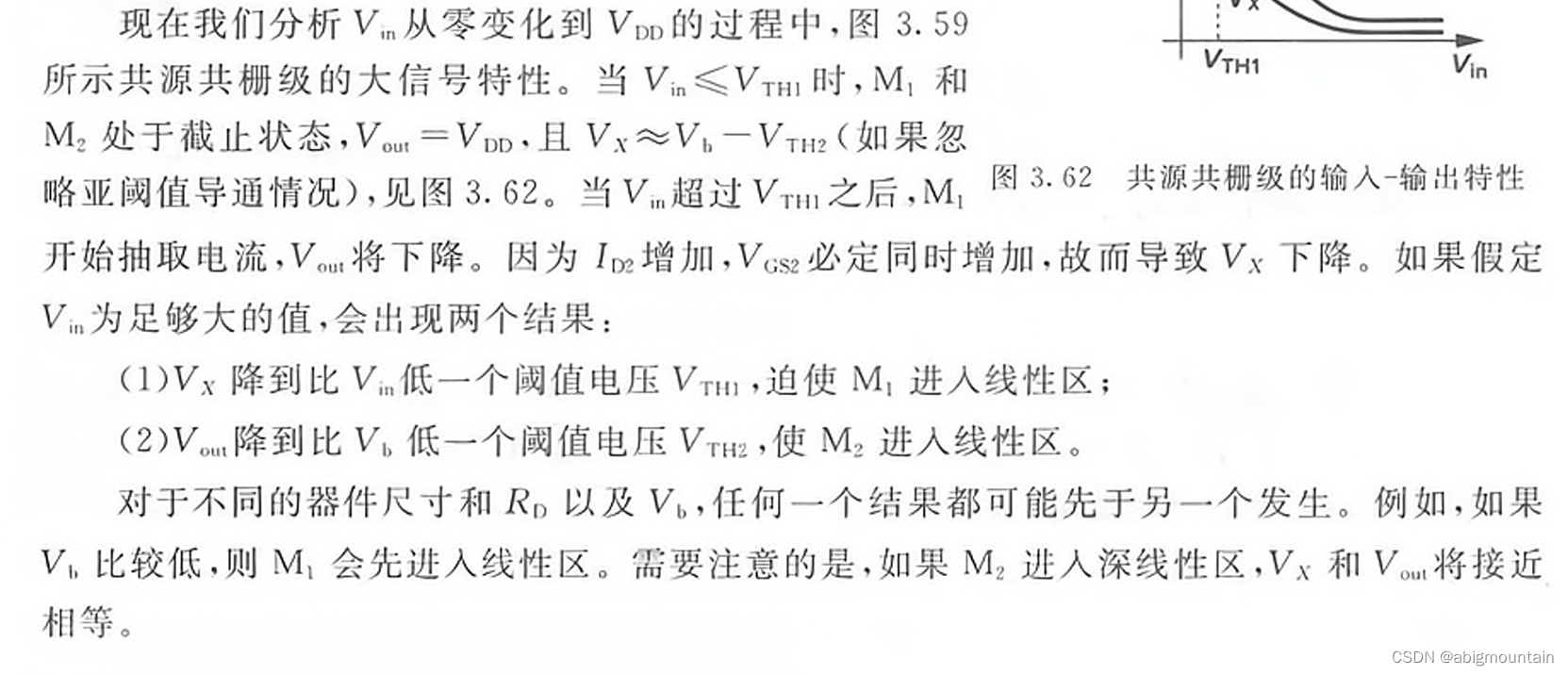

4.1.2大信号分析

4.1.3优势之一:输出阻抗高;缺点之一:电压余度减小

缺点:所需要的额外的电压余度使这样的结构缺少吸引力。例如,三层共源共栅电路的最小输出电压等于三个过驱动电压之和。

输出阻抗高的好处:

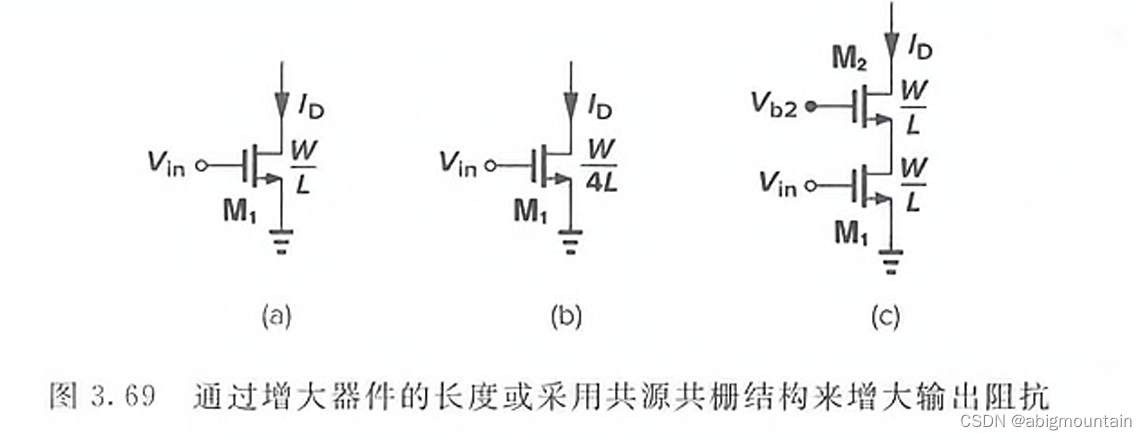

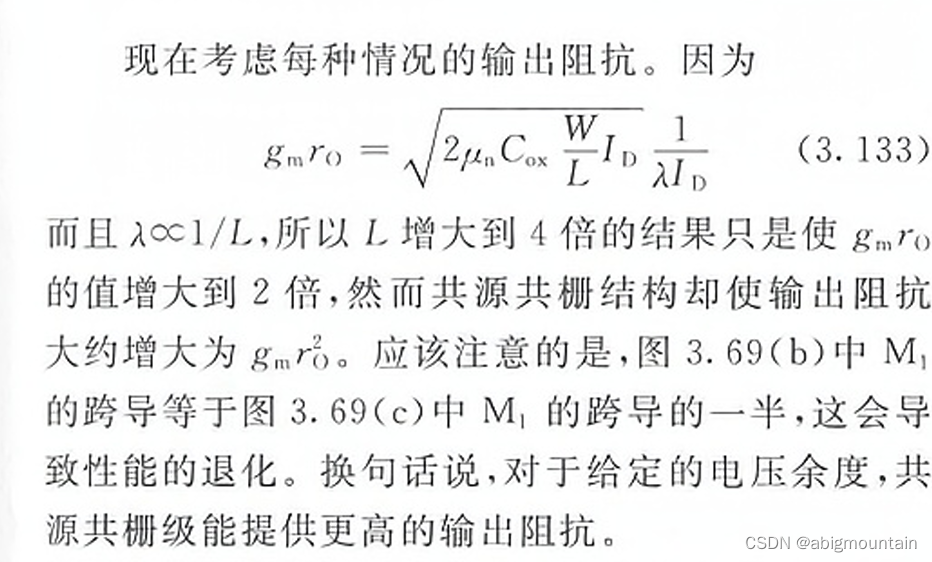

4.1.4比较提高输出阻抗方法:采用共源共栅和增大输入晶体管的沟道长度

4.1.4.1从电压摆幅约束分析

4.1.4.2从输出阻抗分析

总结:电压摆幅约束一样,但共源共栅极能提供更高的输出阻抗

4.1.5应用之一:作恒定电流源

共源共栅结构不一定起放大器的作用。这种结沟的另一种普遍应用是构成恒定电流源。高的输出抗提供一个接近理想的电流源,但这样做的代价是牺牲了电压余度。

注意事项:

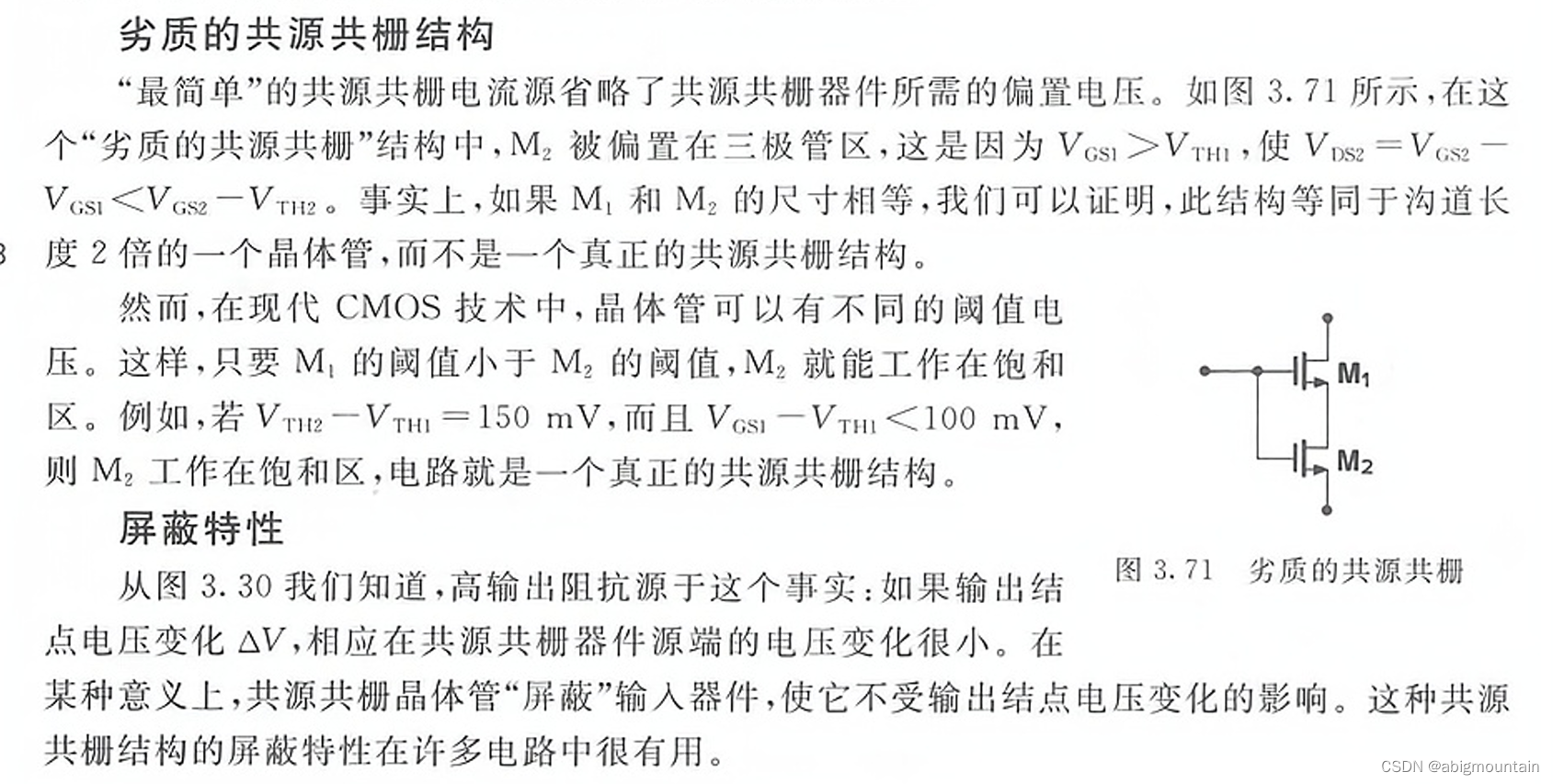

4.1.6优势之一:屏蔽特性

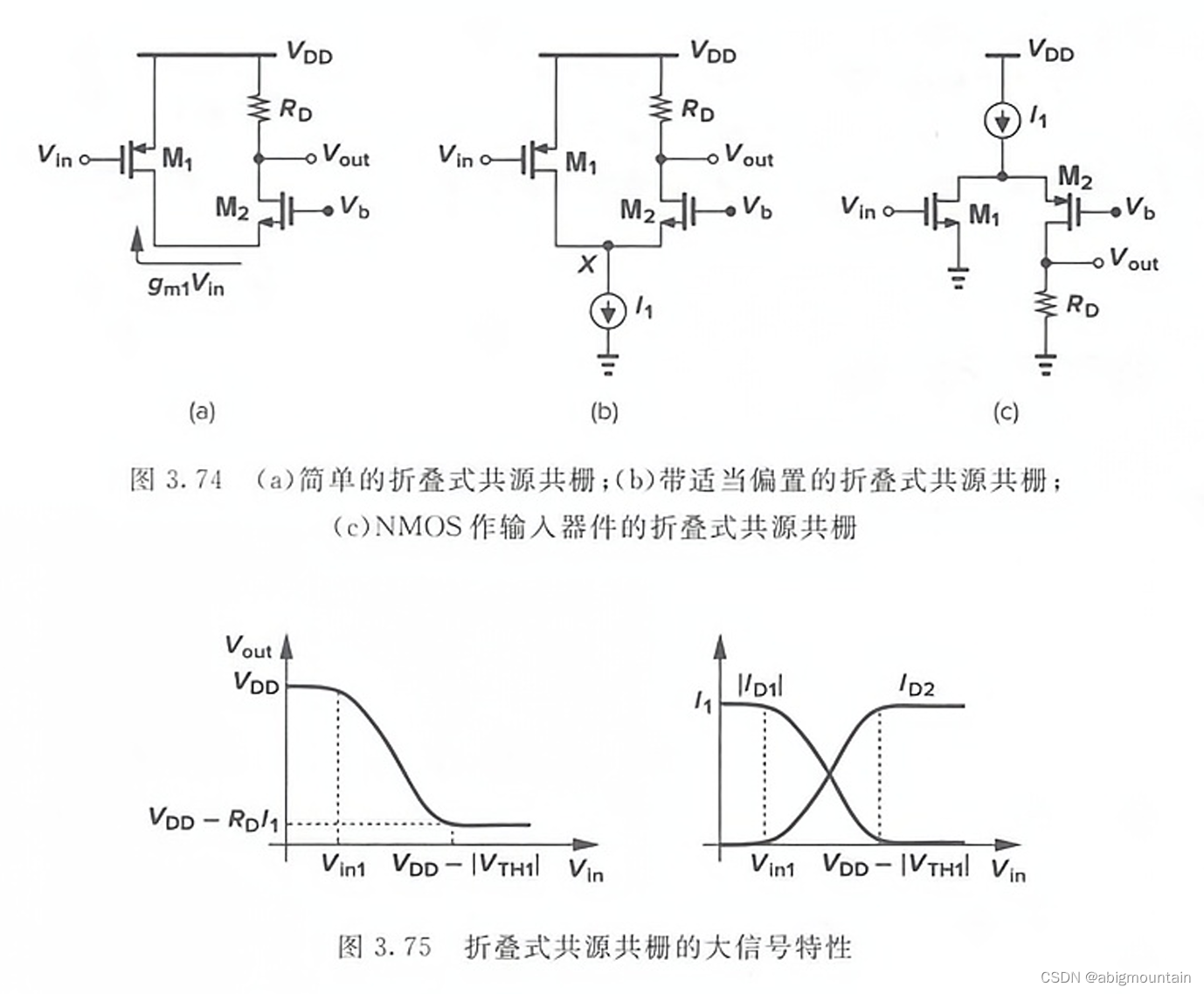

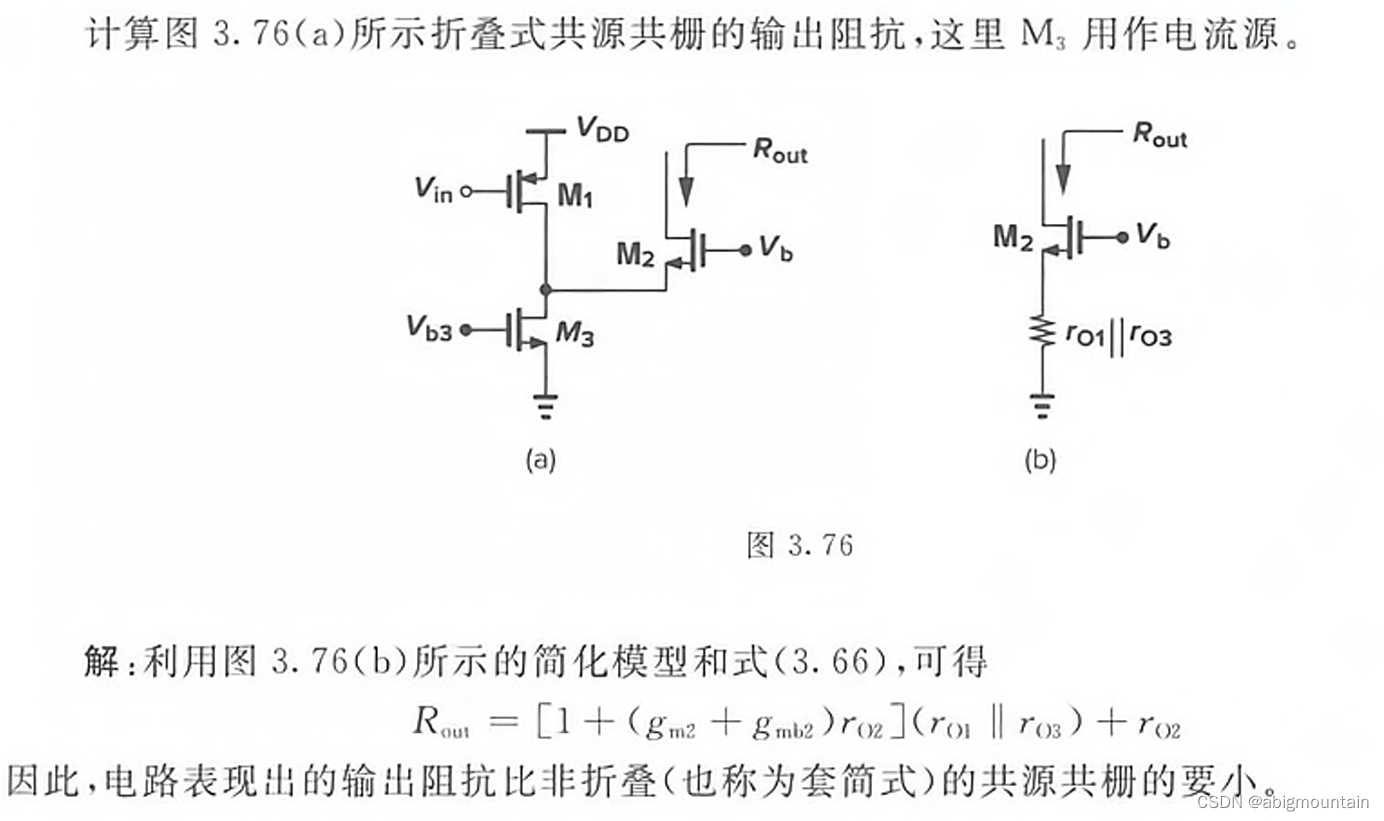

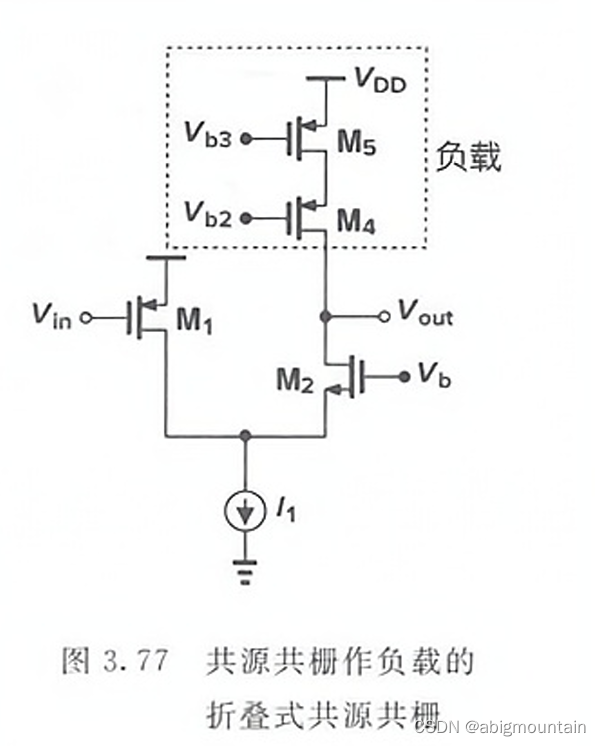

4.2折叠式共源共栅(优缺点说是后面会讲)

4.2.1输出阻抗(比套筒式的小)

4.2.2提高增益的方法

4.2.3电路速度容易负载影响?

1142

1142

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?