目录

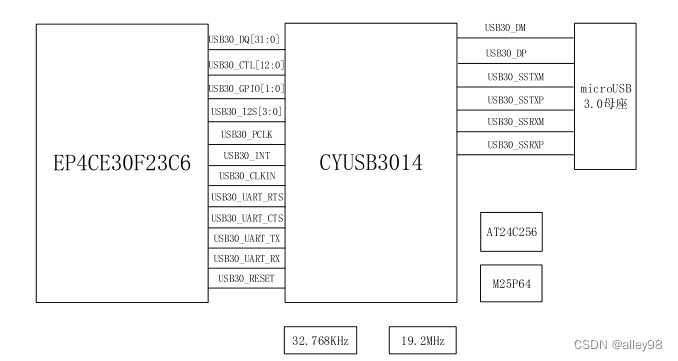

1. USB3014连接框图

为了充分发挥 USB3.0芯片的特性,特将 CYUSB3014芯片的所有数字 IO与 FPGA连接,包括 32根数据线,13根控制线、4根 I2S信号线以及 UART线等。

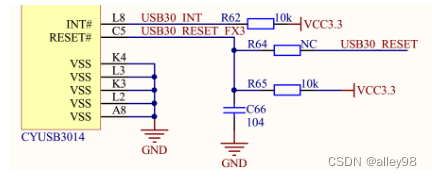

2. 复位设置

CYUSB3014有一个复位输入接口,当复位输入为低电平时,芯片处于复位状态。只有当该引脚为高电平时,芯片才能正常工作,AC6102开发板在设计时,充分考虑了实际应用和系统调试时的情况,给 CYUSB3014设计了两种复位方式,分别为 FPGA控制复位和上电自动复位。默认使用上电自动复位方式,该方式非常适合我们调试系统原型时使用,这样不必担心因为重新下载 FPGA 的 sof固件而导致 USB芯片复位,影响 USB3.0芯片的正常运行。增加调试时候的工作量。(如果使用 fpga控制复位,那么每次下载完 fpga的 sof后,都会对USB芯片执行一次复位操作,从而使芯片内烧写的固件丢失,那么用户只能再烧写一次 usb芯片固件,从而增加了调试时候的工作量)。如下图,R64默认没有焊接,即断开了 CYUSB芯片与 FPGA芯片的连接,从而避免受到 FPGA固件的影响,如果产品最终定型需要测试使用 FPGA直接控制 USB芯片复位,给 R64安装 100R左右的电阻即可。

对比USRP B2X0系列FPGA芯片,对于复位则是加了按键复位操作,见下图,也是大多数FPGA的通用复位方法。

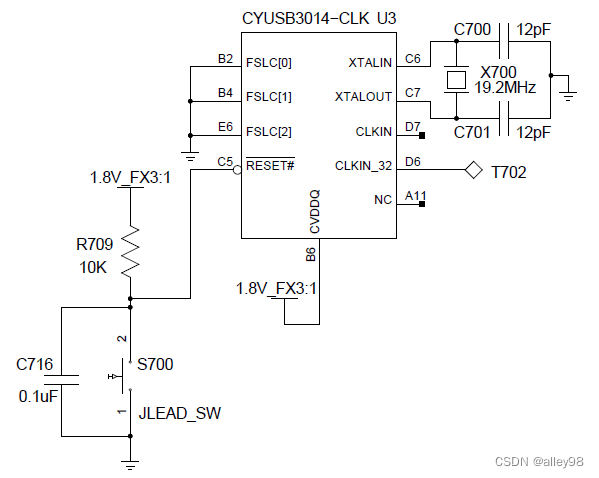

3. 时钟晶振

CYUSB3014支持外部晶振提供时钟信号,支持 19.2、26、38.4和 52MHz的时钟频率,AC6102开发板上使用 19.2MHz的晶振为 CYUSB3014提供时钟源。另外,CYUSB3014内部有一个看门狗定时器,用来在需要的时候对全局系统服务,看门狗定时器使用外部 32.768KHz时钟输入,所以 AC6102上也设计了一个 32.768KHz的晶振。当然,

本文详细介绍了如何将CYUSB3014 USB3.0芯片与FPGA进行连接和配置,涵盖了复位设置、时钟源、IIC存储器和SPI闪存等方面,重点解析了复位方式和引导模式的选择,以及IIC和SPI存储器在FPGA设计中的应用。

本文详细介绍了如何将CYUSB3014 USB3.0芯片与FPGA进行连接和配置,涵盖了复位设置、时钟源、IIC存储器和SPI闪存等方面,重点解析了复位方式和引导模式的选择,以及IIC和SPI存储器在FPGA设计中的应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3981

3981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?