使用synopsis vcs + verdi进行verilog测试

前言

VCS是由Synopsys公司开发的一个特定EDA工具,全称为Verilog Compiled Simulator。它是一个高性能的仿真器,用于验证RTL设计的行为;

Verdi是Synopsys公司提供的一款先进的调试和验证工具,它是SystemVerilog和VHDL设计的黄金标准。Verdi工具主要用于对复杂SoC(System on Chip)设计的验证过程,提供了丰富的调试功能和强大的分析能力,帮助设计者确保设计满足预期的功能和性能要求。

一、VCS三步法进行Verilog代码编译运行

1. analysis:

作用:分析VHDL代码和verilog代码,并将分析后的中间文件存储到设计中或者工作库中

语法:

% vlogan [vlogan_options] <Verilog_source_filename>

% vhdlan [vhdlan_options] <VHDL_filename_list>

其中 vlogan用于针对 Verilog文件的分析,而 vhdlan用于针对vhdl文件的分析

2. Elaboration:

作用: 执行设计的编译/细化,并创建模拟可执行文件

语法:

% vcs [libname.]design_unit [options]

3. Simulation:

作用: 运行Elaboration环节产生的可执行文件,进而进行case测试,也可以dump对应的波形进行分析对比

语法:

./simv_exe [runtime_options]

具体的runtime_options就不再过多介绍,可以自行到官网查找

举个例子

目前我有如下两个源码文件:

gcb.v top.v

其中top.v为例化了gcb.v的testbench,且为了使用verdi观察波形,我们在top.v的最后加入了如下代码: 使用$fsdbDumpvars 方法进行波形的dump

initial begin

$fsdbDumpfile("./simwave/top.fsdb");

$fsdbDumpvars(0,top,"+mda");

//$fsdbDumpvars(1,top.uut);

end

为了方便,我将以上三步写在一个Makefile文件中,代码如下:

// Makefile

OUTPUT := gcd_top

SIMV_EXECUTABLE := top_simv

### Step1. Clean all existed stuff ###

comp:

@echo "******************************************"

@echo "VCS Compile DUT"

@echo "******************************************"

vlogan $(COMP_OPTS) \

$(MC_COMP_OPTS) \

-l comp_dut.log

@echo "******************************************"

@echo "Compile DUT Done"

@echo "******************************************"

COMP_OPTS += -sverilog -full64 +define+VCS -timescale=1ns/1ps \

-debug_access+all -kdb \

MC_COMP_OPTS += gcd.v top.v

elab:

vcs $(ELAB_OPTS) top -o $(SIMV_EXECUTABLE) \

-l elab.log \

@echo "******************************************"

@echo "Elab Done"

@echo "******************************************"

ELAB_OPTS = +vcs+lic+wait -full64 -debug_access+all \

+warn=noINAV +warn=noTFIPC +warn=noFRCREF +warn=noTIME-RESOLUTION-WRN-SRC -lca -kdb -j4

sim:

./$(SIMV_EXECUTABLE) -l ./sim.log \

+vpdfile+$(TESTCASE).vpd \

+FSDB $(SIM_OPTS) \

+OUTDIR=./sim_out \

+SEED=$(SEED)

几点说明:

1.comp 阶段:

这个阶段需要注意的有一点,那就是源文件的指定,通常来说有两种方式:

1.直接通过 -v a.v b.v的方式(这里a.v b.v为所需编译的源文件)

2.如果文件较多,可以将所有源文件的路径写在一个filelist当中,通过 -f filelist的方式来指定【需要注意的是,如果源文件中有使用 #include 语句,需要将所包含文件的路径在filelist给出】

例如:

// b.v (the path of a.v is /source/code/

# include "a.v"

......

.......

则在filelist中,需要加入 +incdir+/source/code,否则编译时可能会提示找不到a.v

2.elab 阶段:

1.顶层模块的指定:在comp阶段过后,会为每个module进行编译,产生一个同名的design_unit

例如:b.v在comp之后会产生一个名为b的design_unit

这时便可以通过指定对应unit为顶层模块进行elab,产生对应的输出文件

2.输出文件的指定:通过-o SIMV_EXE_NAME选项给定

3.sim 阶段:

这一阶段较为简单,直接调用elab阶段生成的可执行文件,进行仿真即可;

这一步之后,会产生对应的fsdb波形文件**【波形文件具体路径是在 tb 中指定的】**

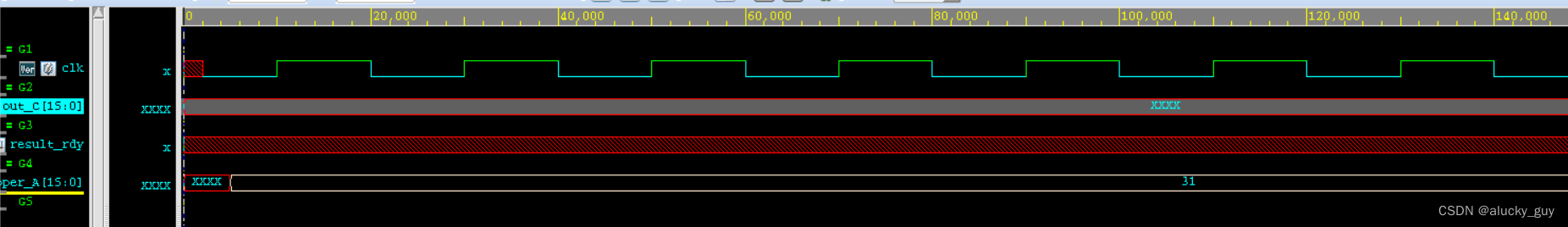

二、verdi进行波形查看

1.首先打开verdi程序

2.点击file中的import design,将对应的设计导入【也可以直接导入filelist.f文件】

3.点击 new waveform,然后将产生的.fsdb文件导入

4.随后即可通过将源程序中对应的信号拉进波形窗口的形式得到对应信号的波形:

完结撒花 !!

2778

2778

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?