| 实验3.2模十BCD计数器模块设计

| 主从JK触发器Verilog HDL数据流描述源代码 | 文件名:lab3_1 | | module lab3_1(Q,QN,J,K,CLK,CLR); // 主从jkT 触发器 Verilog HDL 数据流描述 input J,K,CLK,CLR; //负向沿时钟和高电平清零 output Q,QN; //Q 为 1 位输出 wire net1,net2,net3,net4,net5,net6; //定义内部线 assign net1 = !(net3 && (!CLK)); assign net2 =!(net4 && (!CLK)); assign net3=!(net5 && net4); assign net4=!(net3 && net6 && CLR); assign net5=!(QN && J && CLK && CLR); assign net6=!(Q && CLK && K); assign QN =!(Q && CLR && net2), Q =!(net1 && QN); endmodule |

| 模十BCD计数器Verilog HDL门级结构描述源代码 | 文件名:module lab3_2 | | module lab3_2(Q,CLK,CLR,CTR); //模十BCD计数器 Verilog HDL 门级结构描述 input CLK,CLR,CTR; //负向沿时钟和高电平清零 output [3:0]Q; //Q 为输出总线,线宽为 4 位 lab3_1 lab3_1r0(Q[0], ,CTR,CTR,CLK,CLR), //隐式调用,注意端口顺序 lab3_11(Q[1], ,QN,CTR,Q[0],CLR), //counter模块 QN 端口未使用,用空格表示该端口悬çᄅ ᄎ lab3_12(Q[2], ,CTR,CTR,Q[1],CLR), lab3_13(Q[3],QN,Q[1]&&Q[2],CTR,Q[0],CLR); endmodule |

| 模十BCD计数器Verilog HDL行为描述源代码 | 文件名: | | module lab3_3(Q,CLK,CLR,CTR); input CTR, //数据输入端 CLK, //时钟信号下降沿触发 CLR; //清零信号 output [3:0]Q; //输出 reg [3:0]Q; //定义为寄存器类型 always@(negedge CLK or negedge CLR or negedge CTR)//每当CLK,CLR,CTR负向沿的时候 begin //always只能有一个语句,多个语句用begin end if(!CLR) //当CLR=0,无,表示1 Q<=4'b0; //数据清零 else if(!CTR)//其他情况 begin //??else多个语句用begin end Q<=Q; //暂停保持不变 end else if(Q==4'b1001)//计数到第十个清零 begin Q<=4'b0000; end else begin Q<=Q+1;//正常计数 end //?? else if?? end //??always?? endmodule //计数器模块结束 |

| 模十BCD计数器testbench Verilog HL源码 | 文件名: | | `timescale 10ns/1ns module lab3_4; reg CLK,CLR,CTR; //输入端口 wire [3:0] QA; wire [3:0] QB; //对应移位寄存器的输出总线 lab3_2 lab3_20(QA,CLK,CLR,CTR);//调用移位寄存器描述模块 lab3_3 lab3_30(QB,CLK,CLR,CTR); initial // begin $monitor($time, "Q_SD = %b Q_BD = %b CTR =%b CLR =%b",QA,QB,CTR,CLR);//输出结构描述的结果 CLK = 0; //将所有信号的寄存器初始值赋值为0 CLR = 0; CTR=0; #22 CLR = 1; //退出清0状态 #22 CTR = 1; //退出暂停状态,开始计数 #200 CLR = 0; //中途清零状态 #20 CLR=1;//继续计数 #100 CTR = 0; //中途暂停 #22 CTR = 1; //继续计数 #50 $stop; end always #5 CLK = ~CLK; //时钟5个时间单位翻转一次 always @(posedge CLK); endmodule |

实验3.3四位同步计数器模块设计

| 主从JK触发器Verilog HDL门级结构描述或数据流描述源代码 | 文件名: | | module lab3_1(Q,QN,J,K,CLK,CLR); // 主从jkT 触发器 Verilog HDL 数据流描述 input J,K,CLK,CLR; //负向沿时钟和高电平清零 output Q,QN; //Q 为 1 位输出 wire net1,net2,net3,net4,net5,net6; //定义内部线 assign net1 = !(net3 && (!CLK)); assign net2 =!(net4 && (!CLK)); assign net3=!(net5 && net4); assign net4=!(net3 && net6 && CLR); assign net5=!(QN && J && CLK && CLR); assign net6=!(Q && CLK && K); assign QN =!(Q && CLR && net2), Q =!(net1 && QN); endmodule . |

| 四位同步计数器Verilog HDL门级结构描述源代码 | 文件名:lab3_5 | | module lab3_5(Q,CLK,CLR,EN); //四位同步计数器 Verilog HDL 门级结构描述 input CLK,CLR,EN; //负向沿时钟和高电平清零 output [3:0]Q; //Q 为输出总线,线宽为 4 位 lab3_1 lab3_10(Q[0], ,EN,EN,CLK,CLR), //隐式调用,注意端口顺序 lab3_11(Q[1], ,EN&&Q[0],EN&&Q[0],CLK,CLR), lab3_12(Q[2], ,EN&&Q[0]&&Q[1],EN&&Q[0]&&Q[1],CLK,CLR), lab3_13(Q[3], ,EN&&Q[0]&&Q[1]&&Q[2],EN&&Q[0]&&Q[1]&&Q[2],CLK,CLR); endmodule |

| 四位同步计数器Verilog HDL行为描述源代码 | 文件名: | | module lab3_6(Q,CLK,CLR,EN); input EN, //数据输入端 CLK, //时钟信号下降沿触发 CLR; //清零信号 output [3:0]Q; //输出 reg [3:0]Q; //定义为寄存器类型 always@(negedge CLK or negedge CLR or negedge RN)//每当CLK,CLR,RN负向沿的时候 begin //always只能有一个语句,多个语句用begin end if(!CLR) //当CLR=0,无,表示1 Q<=4'b0; //数据清零 else if(RN)//其他情况 begin //??else多个语句用begin end Q<=Q; //暂停保持不变 end else if(Q==4'b11111)//计数清零 begin Q<=4'b0000; end else begin Q<=Q+1;//正常计数 end //?? else if?? end //??always?? endmodule //计数器模块结束 |

根据实验要求编写计数器电路的测试激励文件,比较全面分析计数器的功能,并能对比门级结构描述(或数据流描述)和行为描述的结果。

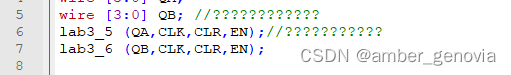

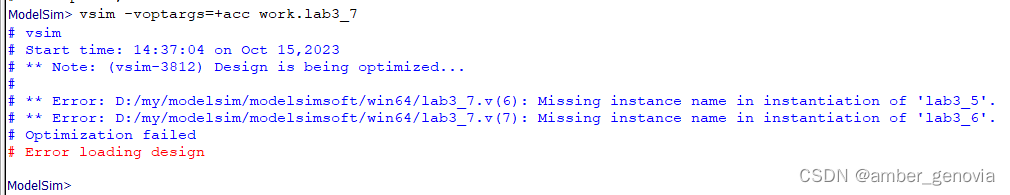

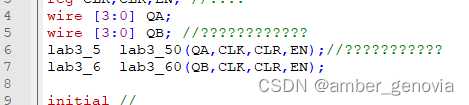

| 四位同步计数器testbench Verilog HL源码 | 文件名: | | `timescale 10ns/1ns module lab3_4; reg CLK,CLR,EN; //输入端口 wire [3:0] QA; wire [3:0] QB; //对应移位寄存器的输出总线 lab3_5 lab3_50(QA,CLK,CLR,EN);//调用移位寄存器描述模块 lab3_6 lab3_60(QB,CLK,CLR,EN); initial // begin $monitor($time, "Q_SD = %b Q_BD = %b EN =%b CLR =%b",QA,QB,EN,CLR);//输出结构描述的结果 CLK = 0; //将所有信号的寄存器初始值赋值为0 CLR = 0; EN=0; #22 CLR = 1; //退出清0状态 #22 EN = 1; //退出暂停状态,开始计数 #300 CLR = 0; //中途清零状态,完整周期 #20 CLR=1;//继续计数 #100 EN = 0; //中途暂停 #22 EN = 1; //继续计数 #50 $stop; end always #5 CLK = ~CLK; //时钟5个时间单位翻转一次 always @(posedge CLK); endmodule |

|

5080

5080

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?