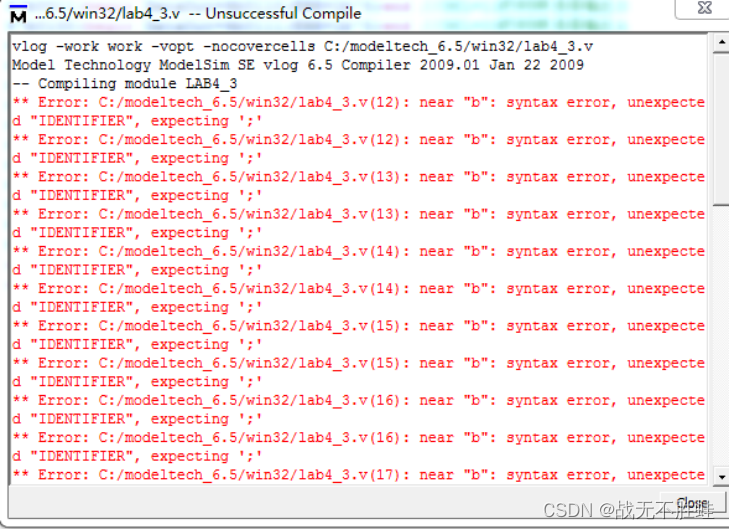

1.case 语句后面多个语句要也begin end 第二个卡在这,case还有其他表示法,用{}之类的

2.最开始一直卡在这,搞半天发现是 4'b1111,不是4b'1111

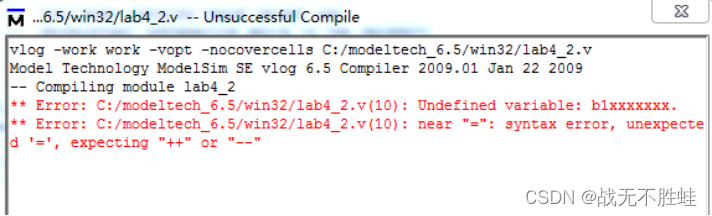

** Error: C:/modeltech_6.5/win32/lab4_2.v(10): Undefined variable: b1xxxxxxx.

** Error: C:/modeltech_6.5/win32/lab4_2.v(10): near "=": syntax error, unexpected '=', expecting "++" or "--"

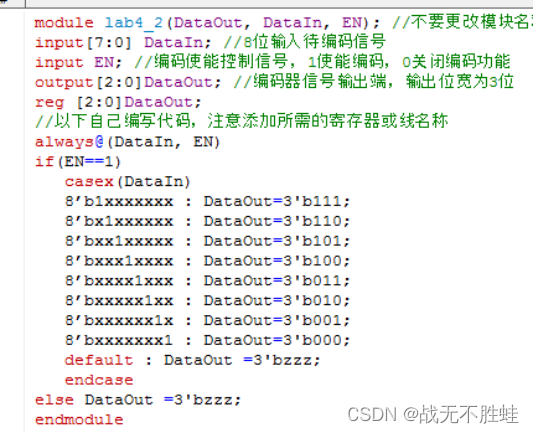

| 83优先编码器Verilog HDL行为描述源代码 | 文件名: |

| module lab4_2(DataOut, DataIn, EN); //不要更改模块名称和端口名称,否则影响后面模块调用 input[7:0] DataIn; //8位输入待编码信号 input EN; //编码使能控制信号,1使能编码,0关闭编码功能 output[2:0]DataOut; //编码器信号输出端,输出位宽为3位 reg [2:0]DataOut; //以下自己编写代码,注意添加所需的寄存器或线名称 always@(DataIn, EN) //????SEL?????????? if(!EN) begin DataOut=3'bzzz; end else begin casex(DataIn) //?????? 8'b1xxxxxxx:DataOut=3'b111; //SEL=00???????A 8'b01xxxxxx:DataOut=3'b110; //SEL=01???????B 8'b001xxxxx:DataOut=3'b101; //SEL=10???????C 8'b0001xxxx:DataOut=3'b100; 8'b00001xxx:DataOut=3'b011; 8'b000001xx:DataOut=3'b010; 8'b0000001x:DataOut=3'b001; 8'b00000001:DataOut=3'b000; //SEL=11???????D default:DataOut=3'bzzz; //SEL??????????8?11111111?????????0 endcase end //???????? endmodule | |

实验4.3BCD码转余3码编码器模块设计

根据给定的编码器的功能描述及真值表,完成编码器的行为描述,注意注释代码

| BCD码转余3码编码器Verilog HDL行为描述源代码 | 文件名: |

| module lab4_3(DataOut,ERR,DataIn); //不要更改模块名称和端口名称,否则影响后面模块调用 input[3:0] DataIn; //4位输入待编码BCD信号 output[3:0]DataOut; //编码器余3码输出端,输出位宽为4位 output ERR; //编码错误编码标志端口,1为错误编码 reg [3:0]DataOut=0; reg ERR; //以下自己编写代码,注意添加所需的寄存器或线名称 always@(DataIn) //????SEL?????????? case(DataIn) //多路分支语句 4'b0000:begin DataOut=4'b0011;ERR=1'b0;end //SEL=00的时候选择输出A 4'b0001:begin DataOut=4'b0100;ERR=1'b0;end //SEL=01的时候选择输出B 4'b0010:begin DataOut=4'b0101;ERR=1'b0;end //SEL=10的时候选择输出C 4'b0011:begin DataOut=4'b0110;ERR=1'b0;end //SEL=11的时候选择输出D 4'b0100:begin DataOut=4'b0111;ERR=1'b0;end //SEL=00的时候选择输出A 4'b0101:begin DataOut=4'b1000;ERR=1'b0;end //SEL=01的时候选择输出B 4'b0110:begin DataOut=4'b1001;ERR=1'b0;end //SEL=10的时候选择输出C 4'b0111:begin DataOut=4'b1010;ERR=1'b0;end 4'b1000:begin DataOut=4'b1011;ERR=1'b0;end//SEL=00的时候选择输出A 4'b1001:begin DataOut=4'b1100;ERR=1'b0;end //SEL=01的时候选择输出B 4'b1010:begin DataOut=4'b0000;ERR=1'b1;end//SEL=10的时候选择输出C 4'b1011:begin DataOut=4'b0000;ERR=1'b1;end 4'b1100:begin DataOut=4'b0000;ERR=1'b1;end //SEL=00的时候选择输出A 4'b1101:begin DataOut=4'b0000;ERR=1'b1;end //SEL=01的时候选择输出B 4'b1110:begin DataOut=4'b0000;ERR=1'b1;end //SEL=10的时候选择输出C 4'b1111:begin DataOut=4'b0000;ERR=1'b1;end endcase //多路分支语句结束 endmodule | |

实验4.4独热码编码器模块设计

根据给定的独热码编码器的功能描述及真值表,完成编码器的行为描述,注意注释代码

| 独热码编码器Verilog HDL行为描述源代码 | 文件名: |

| module lab4_4(DataIn,RST,DataOut); //不要更改模块名称和端口名称,否则影响后面模块调用 input[2:0] DataIn,RST; //3 位输入待编码信号 output[7:0]DataOut; //独热码编码输出端,输出位宽为8位 //以下自己编写代码,注意添加所需的寄存器或线名称 reg[7:0] DataOut; always@(RST,DataOut,DataIn) begin if(RST==1) casex(DataIn) 3'b000:DataOut=8'b00000001; 3'b001:DataOut=8'b00000010; 3'b010:DataOut=8'b00000100; 3'b011:DataOut=8'b00001000; 3'b100:DataOut=8'b00010000; 3'b101:DataOut=8'b00100000; 3'b110:DataOut=8'b01000000; 3'b111:DataOut=8'b10000000; default:DataOut=8'b00000000; endcase else DataOut=8'b00000000; end endmodule | |

2819

2819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?