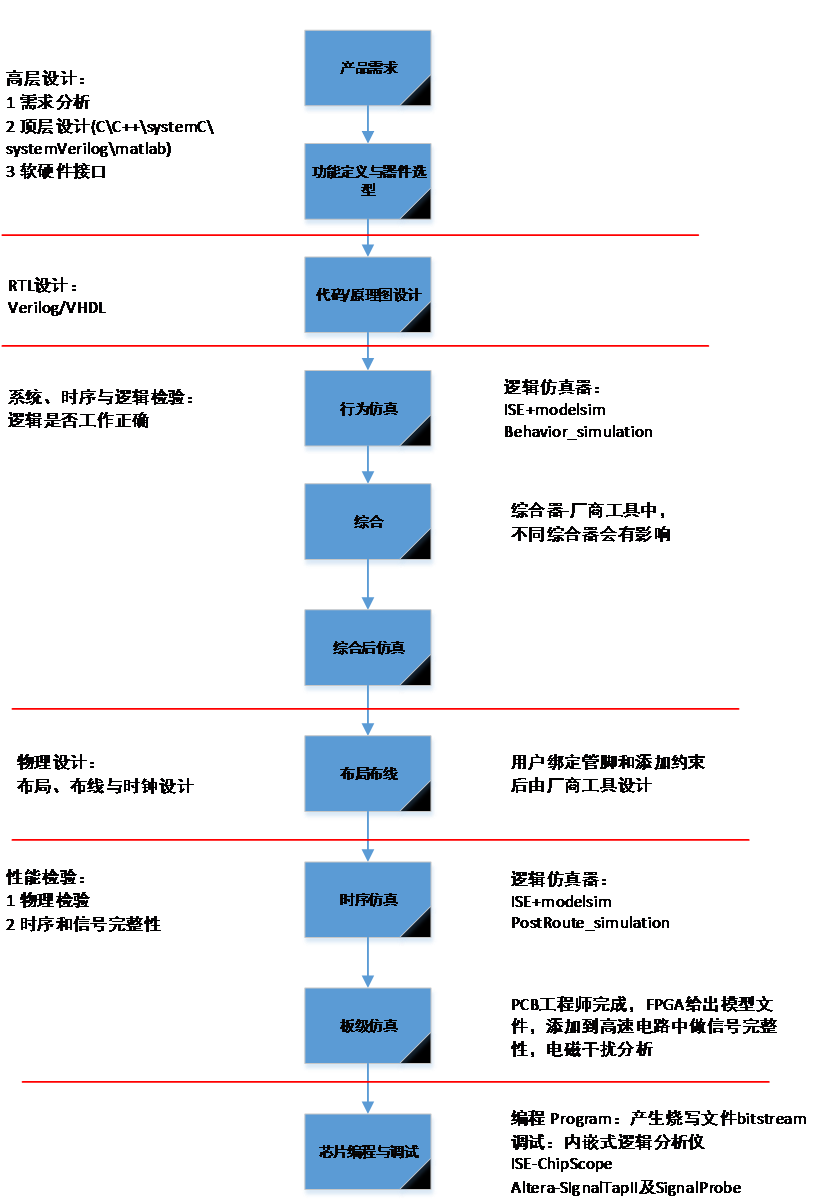

流程:

1 功能定义与器件选型

自顶向下设计,以实现某一功能的为基本模块。FPGA可以用IP核,但是比较僵化,user只作为连线工具,如果想在后期做成ASIC,少用。

2 代码/原理图设计

Verilog-HDL(hardware description[描述,不是设计design] language )

3 行为仿真

Behavior_simulation是指在编译之前对设计的电路进行逻辑功能仿真,没有延迟信息,只知道功能是否正确。

编写Testbench,在modelsim中看报告文件和输出信号波形。

4 综合

Synthesis 将较高级的抽象层次的描述转化成较低层次的描述。

就是将user编写的Verilog code编译成由与门,或门,非门,RAM,触发器等基本逻辑单元组成的逻辑连接网表,并非真实的FPGA内部电路。

综合器都支持到RTL级,门级。一般做到RTL级就行。

5 综合后仿真[一般不做,省略]

仿真综合后的结果是否和设计意图一致,可以估计门延时影响,但不能估计线延时,所以不完全。

一般小型的电路直接看综合后的RTL电路是否和设计意图一致,大型的直接做布局布线后的时序仿真分析。工程出错,时序仿真找不到问题,再通过综合后仿真找具体问题!

6 布局布线

Place&Router—利用实现工具吧逻辑映射到目标器件中。物理上的实现过程,把综合产生的网表具体到FPGA芯片内部电路上。

用户做(时序)约束条件和引脚绑定,从而布局布线工具得出满足条件的最佳布局与连线,并产生相应的文件(配置文件和报告有关设计中各部分资源的使用情况)

7 时序仿真

Post_Route-simulation是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规(即不满足时序约束条件或器件固有的时序规则,如建立时间,保持时间等)现象。

所以不光要看modelsim的波形图,还要看ISE产生的报告!

不同芯片,不同管脚配置,不同约束条件,都会对布局布线有影响。

重新进行了布局布线,也必须重新通过时序仿真。

8 板级仿真

板级仿真主要用于高速电路设计中,用第三方工具,由PCB工程师主导。FPGA只看成一个元件,FPGA工程师提供设计产生FPGA的模型文件,PCB工程师将模型加入到整体电路中,做信号完整性和电磁干扰等分析。

9 芯片编程和调试

芯片编程是指产生烧写到FPGA芯片上的数据文件(Bitstream Generation),并下载。

调试目前多指用FPGA芯片自带的嵌入式逻辑分析仪(如ISE-ChipScope,QuartusII-SignalTapII 和SignalProbe),比额外用逻辑分析仪(logic analyzer)降低了成本,但是要占用芯片部分资源

Compare FPGA and ASIC

ASIC前端比FPGA设计更牛!

规模上,FPGA设计的工程规模比ASIC小的多

流程上,FPGA虽然同时完成了ASIC前端和后端工作,但实际上,FPGA核心的后端主要依赖厂商工具

架构上,FPGA属于半定制化的芯片,属于二次开发

3704

3704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?