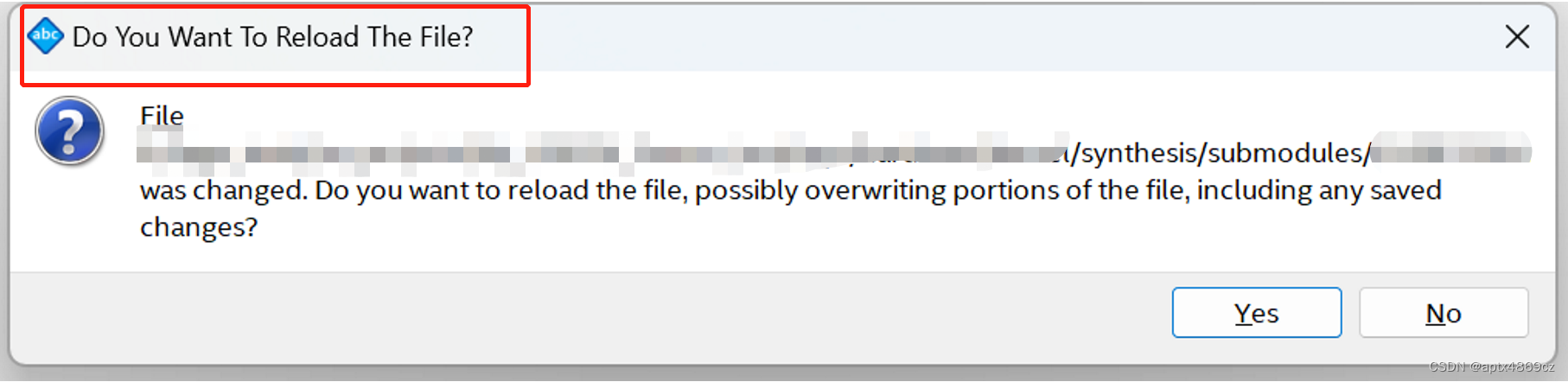

笔者在NIOS的学习尝试使用自己定义的IP核,流程为:在quartus编写verilog文件->通过编译->在platform designer中自定义IP核->在quartus修改IP核的verilog文件->在platform designer中更新自定义IP核->回quartus中,此verilog文件弹出更新界面,确定后,变回没有修改过的版本。如图1。

详细分析如下:

1)首先,我们的初始设计的verilog文件(文件1)放在my_ip文件夹里面;

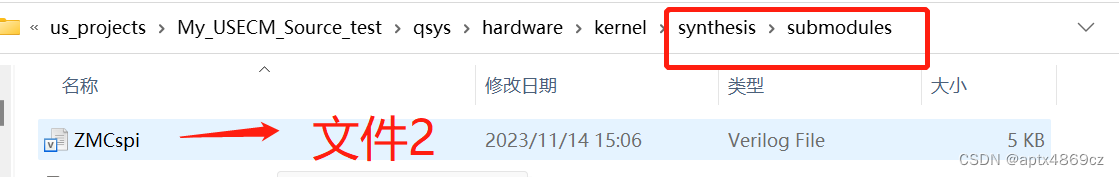

2)然后,我们以这个文件夹的文件1为基础自定义了nios中的IP核,此时quartus会自动在nios的hardware/kernel/sythesis/submodules文件夹中保存一份同名的verilog文件(文件2);

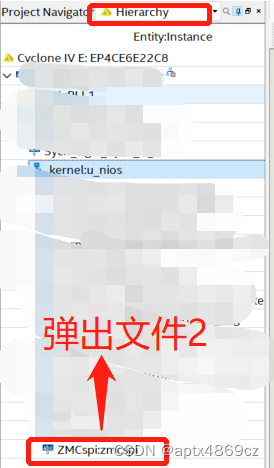

3)然后在quartus中编译后,会在hierarchy下面出现kernel,然后在kernel下会出现我们调用的ip核;

4)当双击这些ip核,其弹出来的是quartus复制在sythesis/submodules中的文件2;

5)修改文件2,crtl+k,然后在paltform designer中更新文件2对应的ip核,然后回到quartus中就会报错,并说要更新,已更新就变回了没改过的版本;

6)上述情况是因为改的是submodules中复制的文件2,而自定义ip核中文件对应的是文件1,所以paltform designer会按照文件1修改submodules的文件2,而文件1没改,所以出现了quartus的文件2变回原来的版本的bug;

7)建议nios在paltform designer自定义IP核的流程:编写verilog(文件1)->通过编译->platform designer自定义IP核->修改IP核参考的文件1->编译->完成修改,这个流程不容易出错;

理论上,直接一步到位,把自定义ip核参考的verilog文件放在sythesis/submodules文件中,可以根治这种问题的出现,笔者还没有尝试过。

笔者不才,或有谬误,烦请指出或沟通学习。

转载请复制此文链接。

788

788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?