这里以STM32F4-Cortex-M4内核为例,来记录下面这些配置是什么意思。

/* The lowest interrupt priority that can be used in a call to a "set priority"

function. */

#define configLIBRARY_LOWEST_INTERRUPT_PRIORITY 0xf

这个是内核优先级分组的位数,对于STM32F4来说,使用了4位来表示优先级。这里把优先级

设置到最低,主要是能够为了其它中断能够打断内核的中断(滴答,pendsv),以达到实时性

/* The highest interrupt priority that can be used by any interrupt service

routine that makes calls to interrupt safe FreeRTOS API functions. DO NOT CALL

INTERRUPT SAFE FREERTOS API FUNCTIONS FROM ANY INTERRUPT THAT HAS A HIGHER

PRIORITY THAN THIS! (higher priorities are lower numeric values. */

*/

#define configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY 2

上面的优先级说的意思就是,不要让抢占优先级大于configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY的中断调用rtos的api(_fromISR). 注意这里,在使用中断时,一定不要忘记配置中断优先级(默认为2),设置的优先级一定要小于这个值(数字要大于) 比如下面配置为2,那么优先级number小于2的,一定不要调用rtos api。如果调用了,rtos的一些状态就乱了(比如中断嵌套层数)系统就跑死掉了。

/* Interrupt priorities used by the kernel port layer itself. These are generic

to all Cortex-M ports, and do not rely on any particular library functions. */

#define configKERNEL_INTERRUPT_PRIORITY ( configLIBRARY_LOWEST_INTERRUPT_PRIORITY << (8 - configPRIO_BITS) )

//M4的抢占优先级在高四位,即[7:4],所以下面这个要左移动4为

上面这个主要是为了获取到当前平台所支持的最小优先级。这里上面已经配置了configLIBRARY_LOWEST_INTERRUPT_PRIORITY 为0xf,因为configPRIO_BITS在cmisc中配置为4。所以这里是左移4.之所以减掉4,是为了获取剩余不用的位数。为什么要把kernel设置为最低优先级,这个我认为是为了确保系统实时性。因为已经有了pendsv中断,有些中断是能延迟响应的。

/* !!!! configMAX_SYSCALL_INTERRUPT_PRIORITY must not be set to zero !!!!

See http://www.FreeRTOS.org/RTOS-Cortex-M3-M4.html. */

#define configMAX_SYSCALL_INTERRUPT_PRIORITY ( configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY << (8 - configPRIO_BITS) )

这个同上面一样,获取最大允许使用系统API的应用权限等级。目前configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY 定义为2,则2<<(8-4) 即32.,只允许中断优先级大于2的中断调用系统API。

调度器代码记录:

BaseType_t xPortStartScheduler( void )

{

#if( configASSERT_DEFINED == 1 )

{

volatile uint32_t ulOriginalPriority;

volatile uint8_t * const pucFirstUserPriorityRegister = ( uint8_t * ) ( portNVIC_IP_REGISTERS_OFFSET_16 + portFIRST_USER_INTERRUPT_NUMBER );

volatile uint8_t ucMaxPriorityValue;

/* Determine the maximum priority from which ISR safe FreeRTOS API

functions can be called. ISR safe functions are those that end in

"FromISR". FreeRTOS maintains separate thread and ISR API functions to

ensure interrupt entry is as fast and simple as possible.

Save the interrupt priority value that is about to be clobbered. */

//下面pucFirstUserPriorityRegister为应用程序第一个中断优先级寄存器,从中断向量表看到这个是WWDG

ulOriginalPriority = *pucFirstUserPriorityRegister;

/* Determine the number of priority bits available. First write to all

possible bits. */

*pucFirstUserPriorityRegister = portMAX_8_BIT_VALUE; //portMAX_8_BIT_VALUE=0xFF

/* Read the value back to see how many bits stuck. */

ucMaxPriorityValue = *pucFirstUserPriorityRegister;

//虽然上面设置的是0xff,当请看下面日志打印,打印出来读过来的是0xf0.这个主要是Cortex-M4,只用4为来表示优先级

LOGD("armwind:%x,%x",ucMaxPriorityValue, portMAX_8_BIT_VALUE);

/* The kernel interrupt priority should be set to the lowest

priority. */

configASSERT( ucMaxPriorityValue == ( configKERNEL_INTERRUPT_PRIORITY & ucMaxPriorityValue ) );

LOGD("ucMaxPriorityValue:%x,KER_INT:%x", ucMaxPriorityValue, configKERNEL_INTERRUPT_PRIORITY);

/* Use the same mask on the maximum system call priority. */

ucMaxSysCallPriority = configMAX_SYSCALL_INTERRUPT_PRIORITY & ucMaxPriorityValue;

/* Calculate the maximum acceptable priority group value for the number

of bits read back. */

//计算最大的优先级分组

ulMaxPRIGROUPValue = portMAX_PRIGROUP_BITS; //portMAX_PRIGROUP_BITS=0x07

while( ( ucMaxPriorityValue & portTOP_BIT_OF_BYTE ) == portTOP_BIT_OF_BYTE )

{ //ucMaxPriorityValue = 0xf0

ulMaxPRIGROUPValue--;

//下面0xf0开始左移1位,由于ucMaxPriorityValue = 0xf0,所以能左移4次,则ulMaxPRIGROUPValue -= 4 = 3;

ucMaxPriorityValue <<= ( uint8_t ) 0x01;

}

/* Shift the priority group value back to its position within the AIRCR

register. */

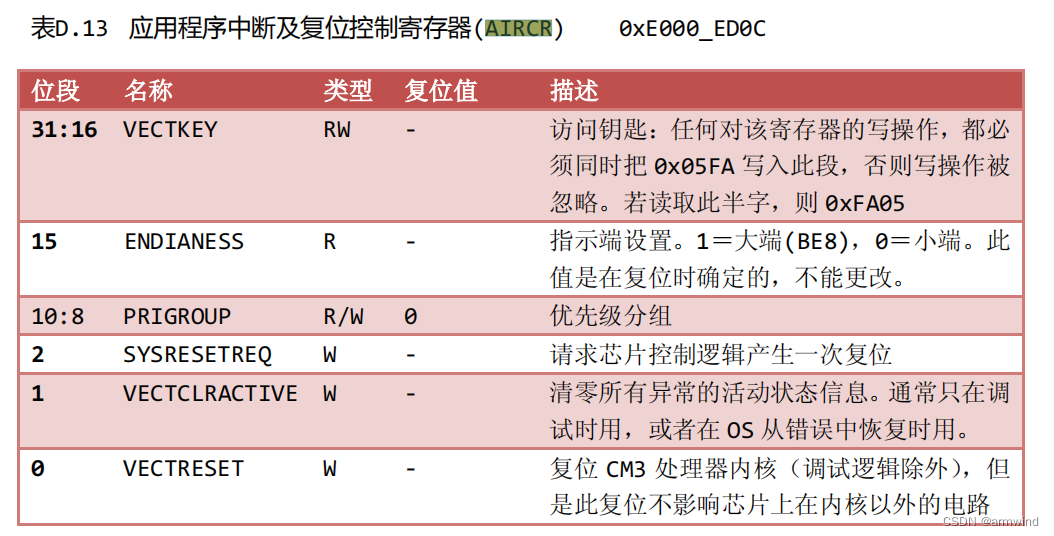

ulMaxPRIGROUPValue <<= portPRIGROUP_SHIFT; //portPRIGROUP_SHIFT = 8 即3<<8 = 0x300

ulMaxPRIGROUPValue &= portPRIORITY_GROUP_MASK;

//portPRIORITY_GROUP_MASK = (0x07UL << 8UL),则上面的与(&) 算下来为, 0x300 & 0x700 = 0x300

//此时系统记录ulMaxPRIGROUPValue = 0x300

/* Restore the clobbered interrupt priority register to its original

value. */

*pucFirstUserPriorityRegister = ulOriginalPriority; //还原原始中断优先级

}

#endif /* conifgASSERT_DEFINED */

/* Make PendSV and SysTick the lowest priority interrupts. */

//将systick和pendsv的中断优先级设置为最低,原因是为了实时性。

portNVIC_SYSPRI2_REG |= portNVIC_PENDSV_PRI;

portNVIC_SYSPRI2_REG |= portNVIC_SYSTICK_PRI;

下面是我加的日志打印出来的,可以看到明明写入的是0xff,可是读过来的是0xf0,这也就是所使用4bit作为优先级

RTOS_CORE [D] xPortStartScheduler:369 armwind:f0,ff

RTOS_CORE [D] xPortStartScheduler:373 ucMaxPriorityValue:f0,KER_INT:f0

上面可以看到最大的优先级分组为0x300,而且FREERTOS官网也建议将Cortex-M4优先级分组设置为Group4,即0x300。默认情况下如果不设置Group4,内核是跑不稳定的,一般是卡死了。这里我特意将stm32f4的中断优先级分组设置为Group3,档案是肯定的,内核卡死。来看一段日志

#if( configASSERT_DEFINED == 1 )

void vPortValidateInterruptPriority( void )

{

uint32_t ulCurrentInterrupt;

uint8_t ucCurrentPriority;

/* Obtain the number of the currently executing interrupt. */

ulCurrentInterrupt = vPortGetIPSR();

LOGI("ulCurrentInterrupt:0x%d",ulCurrentInterrupt);

/* Is the interrupt number a user defined interrupt? */

if( ulCurrentInterrupt >= portFIRST_USER_INTERRUPT_NUMBER )

{

/* Look up the interrupt's priority. */

ucCurrentPriority = pcInterruptPriorityRegisters[ ulCurrentInterrupt ];

/* The following assertion will fail if a service routine (ISR) for

an interrupt that has been assigned a priority above

configMAX_SYSCALL_INTERRUPT_PRIORITY calls an ISR safe FreeRTOS API

function. ISR safe FreeRTOS API functions must *only* be called

from interrupts that have been assigned a priority at or below

configMAX_SYSCALL_INTERRUPT_PRIORITY.

Numerically low interrupt priority numbers represent logically high

interrupt priorities, therefore the priority of the interrupt must

be set to a value equal to or numerically *higher* than

configMAX_SYSCALL_INTERRUPT_PRIORITY.

Interrupts that use the FreeRTOS API must not be left at their

default priority of zero as that is the highest possible priority,

which is guaranteed to be above configMAX_SYSCALL_INTERRUPT_PRIORITY,

and therefore also guaranteed to be invalid.

FreeRTOS maintains separate thread and ISR API functions to ensure

interrupt entry is as fast and simple as possible.

The following links provide detailed information:

http://www.freertos.org/RTOS-Cortex-M3-M4.html

http://www.freertos.org/FAQHelp.html */

LOGI("ucCurrentPriority:0x%x,ucMaxSysCallPriority:0x%x",ucCurrentPriority, ucMaxSysCallPriority);

LOGI("result:%d",ucCurrentPriority >= ucMaxSysCallPriority);

configASSERT( ucCurrentPriority >= ucMaxSysCallPriority );

}

/* Priority grouping: The interrupt controller (NVIC) allows the bits

that define each interrupt's priority to be split between bits that

define the interrupt's pre-emption priority bits and bits that define

the interrupt's sub-priority. For simplicity all bits must be defined

to be pre-emption priority bits. The following assertion will fail if

this is not the case (if some bits represent a sub-priority).

If the application only uses CMSIS libraries for interrupt

configuration then the correct setting can be achieved on all Cortex-M

devices by calling NVIC_SetPriorityGrouping( 0 ); before starting the

scheduler. Note however that some vendor specific peripheral libraries

assume a non-zero priority group setting, in which cases using a value

of zero will result in unpredicable behaviour. */

configASSERT( ( portAIRCR_REG & portPRIORITY_GROUP_MASK ) <= ulMaxPRIGROUPValue ); -------line798

}

#endif /* configASSERT_DEFINED */

上面如果我们将优先级分组设置为Group3,则前面计算出来的ulMaxPRIGROUPValue=0x300;

RTOS_CORE [D] xMBPortEventPost:137 obj:20019dcc,role:0,ev:EV_READY

RTOS_CORE [I] vPortValidateInterruptPriority:750 ulCurrentInterrupt:0x44

RTOS_CORE [I] vPortValidateInterruptPriority:781 ucCurrentPriority:0x50,ucMaxSysCallPriority:32

RTOS_CORE [E] vPortValidateInterruptPriority:798 ASSERT ERROR:0

.由于Group3对应的是0x400,所以上面的断言就为假了,就卡死在哪里。

#define NVIC_PriorityGroup_0 ((uint32_t)0x700) /*!< 0 bits for pre-emption priority

4 bits for subpriority */

#define NVIC_PriorityGroup_1 ((uint32_t)0x600) /*!< 1 bits for pre-emption priority

3 bits for subpriority */

#define NVIC_PriorityGroup_2 ((uint32_t)0x500) /*!< 2 bits for pre-emption priority

2 bits for subpriority */

#define NVIC_PriorityGroup_3 ((uint32_t)0x400) /*!< 3 bits for pre-emption priority

1 bits for subpriority */

#define NVIC_PriorityGroup_4 ((uint32_t)0x300) /*!< 4 bits for pre-emption priority

0 bits for subpriority */

优先级分组:

1960

1960

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?