PL 和PS的高效交互是zynq 7000 soc开发的重中之重,我们常常需要将PL端的大量数

据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA

的方式来进行,但是各种协议非常麻烦,灵活性也比较差,本节课程讲解如何直接通过AXI总

线来读写PS端ddr的数据,这里面涉及到AXI4协议,vivado的FPGA调试等。

1 ZYNQ 的HP端口使用

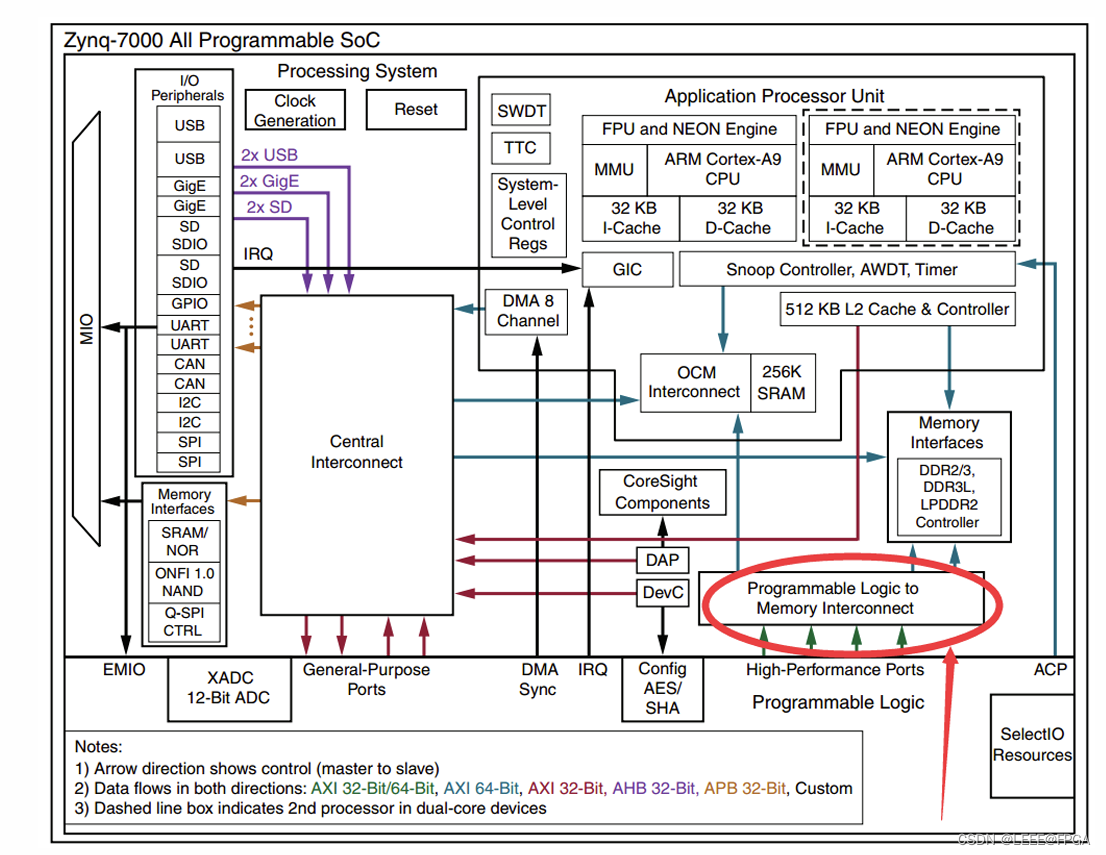

zynq 7000 SOC 的HP口是 High-Performance Ports的缩写,如下图所示,一共有4

个HP口,HP口是AXI Slave设备,我们可以通过这4个HP接口实现高带宽的数据交互。

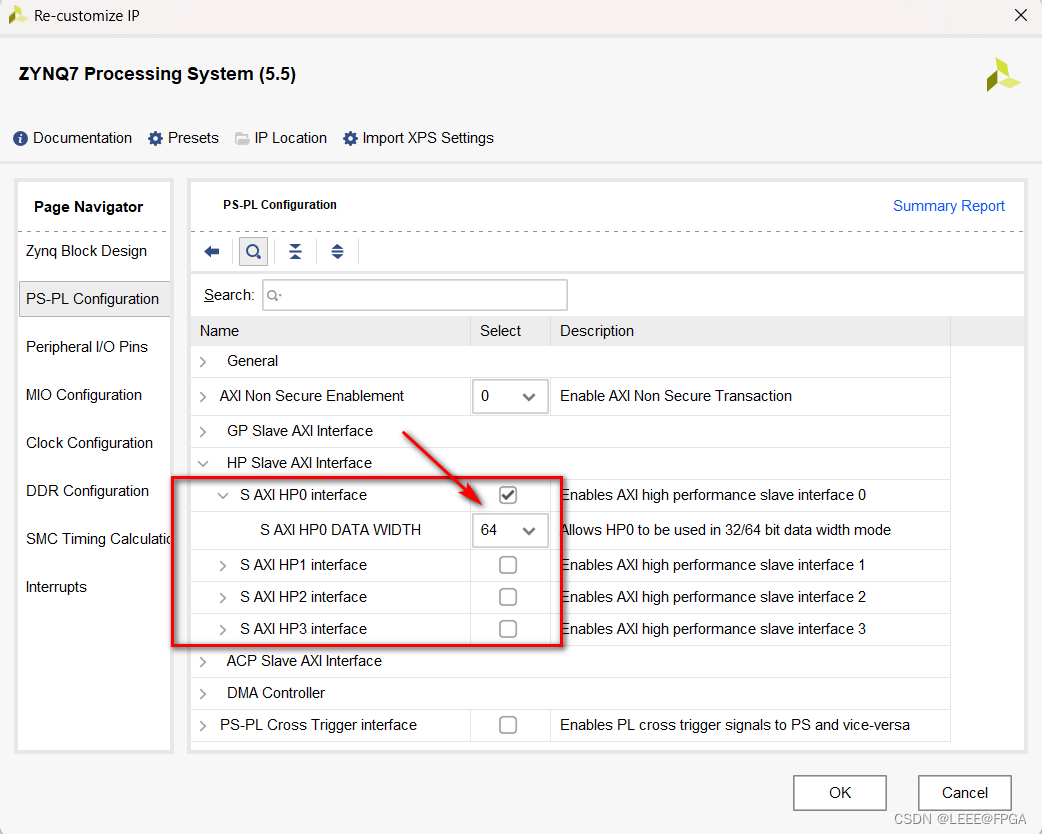

- 在vivado的界面中HP的配置如下图(HP0~HP3),这里面有使能控制,数据位宽选择,可选择32或64bit的位宽。

2)我们的实验启用HP0配置为64bit位宽&#x

本文介绍了如何在ZYNQ 7000 SoC中利用PL端的AXI Master直接读写PS端DDR内存数据,避免复杂的DMA方式。详细阐述了HP端口配置、AXI协议以及读写操作流程,并提供了参考代码资源。

本文介绍了如何在ZYNQ 7000 SoC中利用PL端的AXI Master直接读写PS端DDR内存数据,避免复杂的DMA方式。详细阐述了HP端口配置、AXI协议以及读写操作流程,并提供了参考代码资源。

订阅专栏 解锁全文

订阅专栏 解锁全文

990

990

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?