为了让自己未来好复习,从而写下”计算机系统要素:从零开始构建计算机”读书笔记——2017.7.12。

第一章 布尔逻辑

1.布尔代数

布尔代数处理布尔型(也称为二进制型)数值,比较典型的有 true/false、1/0、YES/NO、on/off.

常见的布尔运算:AND、OR、NOT.

本书中有个重要的结论:

AND/or/not算子都可以只用Nand或Nor函数来构建,既然每个布尔函数都能够通过规范化表示法由AND、OR、NOT构成,那么每个布尔函数也能仅使用Nand函数来构成。(一句话:如果实现了Nand门,就可以用Nand门直接构建其他门。)

ps: 规范化:布尔表达式f(x,y)=x+y

| x | y | f(x,y) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

只关注 输出为1:

则规范化表示为: f(x,y)=x ̅y+xy ̅+xy

2.布尔逻辑的应用

因为计算机硬件基于二进制数据的表示和处理,所以布尔函数在硬件体系结构中结构的描述、构建和优化过程中扮演这十分重要的角色。

3.实际项目

用Nand门构建第一章出现的所有门电路:

有几点:

a.HDL语言

以构建本书Xor为例:

CHIP Xor {

IN a, b;

OUT out;

// BUILTIN Xor;

PARTS://描述了所有底层电路的名称和拓扑结构

Not(in=a,out=nota);

Not(in=b,out=notb);

And(a=a,b=notb,out=w1);

And(a=nota,b=b,out=w2);

Or(a=w1,b=w2,out=out);

}需要注意的几点是:

1,HDL语言所涉及的所有关键词都区分大小写,包括上面所出现的CHIP, PARTS和芯片名等等。

2,所有句子后面都需要加分号。

3,IN和OUT声明了该CHIP的输入和输出。

4,在out表达式中,“=”符号是向右赋值的,“out”是输入管教通过运算输出的值比如上面的“Not(in=a,out=nota)” in=a,为输入,经过NOT运算输出到out,out向右赋值到nota;。

5.在调用其他函数时要注意它的调用格式比如Not(in=,out=)

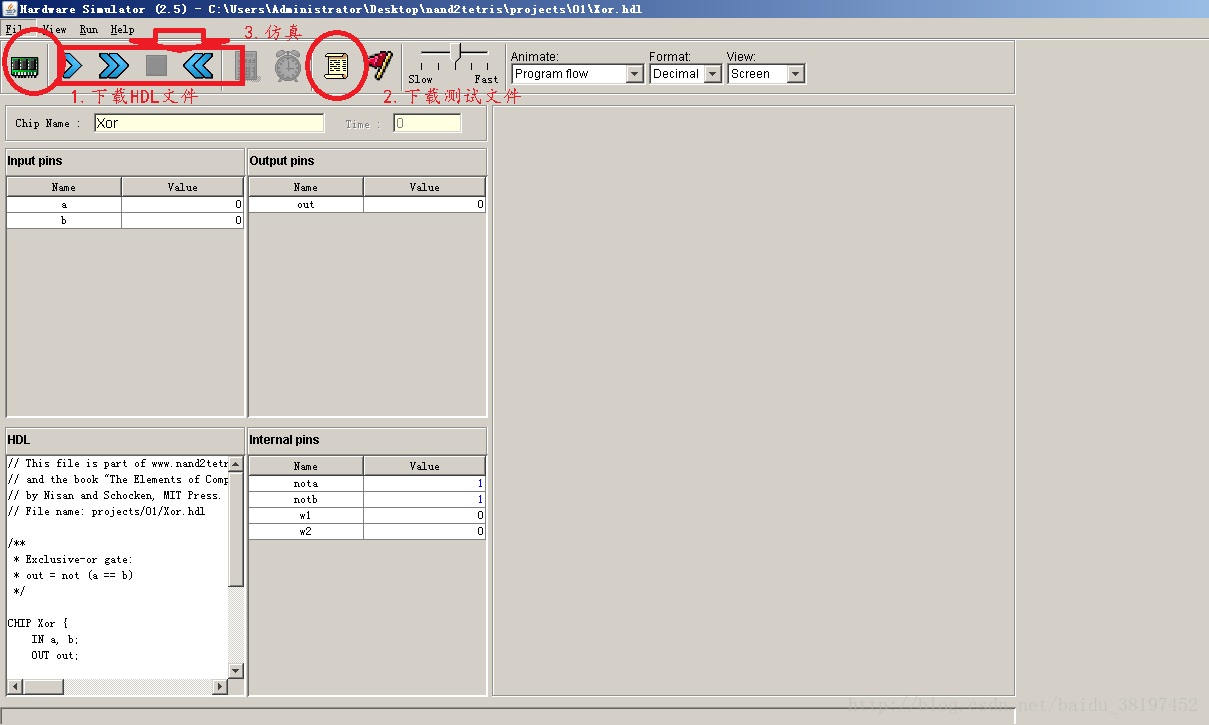

b.硬件仿真软件

开始项目:

1.NOT门

CHIP Not {

IN in;

OUT out;

PARTS:

Nand(a=in,b=in,out=out);

}

2.And门

CHIP And {

IN a, b;

OUT out;

PARTS:

Nand(a=a,b=b,out=w1);

Nand(a=w1,b=w1,out=out);//调用not也可以

}

3.Or门

CHIP Or {

IN a, b;

OUT out;

PARTS:

Nand(a=a,b=a,out=w1);

Nand(a=b,b=b,out=w2);

Nand(a=w1,b=w2,out=out);

}

4.Xor

CHIP Xor {

IN a, b;

OUT out;

PARTS:

Not(in=a,out=na);

Not(in=b,out=nb);

And(a=a,b=nb,out=w1);

And(a=na,b=b,out=w2);

Or(a=w1,b=w2,out=out);

}

5.mux

* if sel == 0 out = a

* otherwise out =b

CHIP Mux {

IN a, b, sel;

OUT out;

PARTS:

Not(in=sel,out=nsel);

And(a=a,b=nsel,out=w1);

And(a=b,b=sel,out=w2);

Or(a=w1,b=w2,out=out);

}

6.DMUX

* {a,b} = {in,0} if sel == 0

* {0,in} if sel == 1

CHIP DMux {

IN in, sel;

OUT a, b;

PARTS:

Not(in=sel,out=nsel);

And(a=in,b=nsel,out=a);

And(a=in,b=sel,out=b);

}

7.NOT16

CHIP Not16 {

IN in[16];

OUT out[16];

PARTS:

Not(in=in[0],out=out[0]);

Not(in=in[1],out=out[1]);

Not(in=in[2],out=out[2]);

Not(in=in[3],out=out[3]);

Not(in=in[4],out=out[4]);

Not(in=in[5],out=out[5]);

Not(in=in[6],out=out[6]);

Not(in=in[7],out=out[7]);

Not(in=in[8],out=out[8]);

Not(in=in[9],out=out[9]);

Not(in=in[10],out=out[10]);

Not(in=in[11],out=out[11]);

Not(in=in[12],out=out[12]);

Not(in=in[13],out=out[13]);

Not(in=in[14],out=out[14]);

Not(in=in[15],out=out[15]);

}

8.AND16

CHIP And16 {

IN a[16], b[16];

OUT out[16];

PARTS:

And(a=a[0],b=b[0],out=out[0]);

And(a=a[1],b=b[1],out=out[1]);

And(a=a[2],b=b[2],out=out[2]);

And(a=a[3],b=b[3],out=out[3]);

And(a=a[4],b=b[4],out=out[4]);

And(a=a[5],b=b[5],out=out[5]);

And(a=a[6],b=b[6],out=out[6]);

And(a=a[7],b=b[7],out=out[7]);

And(a=a[8],b=b[8],out=out[8]);

And(a=a[9],b=b[9],out=out[9]);

And(a=a[10],b=b[10],out=out[10]);

And(a=a[11],b=b[11],out=out[11]);

And(a=a[12],b=b[12],out=out[12]);

And(a=a[13],b=b[13],out=out[13]);

And(a=a[14],b=b[14],out=out[14]);

And(a=a[15],b=b[15],out=out[15]);

}

9.OR16

CHIP Or16 {

IN a[16], b[16];

OUT out[16];

PARTS:

Or(a=a[0],b=b[0],out=out[0]);

Or(a=a[1],b=b[1],out=out[1]);

Or(a=a[2],b=b[2],out=out[2]);

Or(a=a[3],b=b[3],out=out[3]);

Or(a=a[4],b=b[4],out=out[4]);

Or(a=a[5],b=b[5],out=out[5]);

Or(a=a[6],b=b[6],out=out[6]);

Or(a=a[7],b=b[7],out=out[7]);

Or(a=a[8],b=b[8],out=out[8]);

Or(a=a[9],b=b[9],out=out[9]);

Or(a=a[10],b=b[10],out=out[10]);

Or(a=a[11],b=b[11],out=out[11]);

Or(a=a[12],b=b[12],out=out[12]);

Or(a=a[13],b=b[13],out=out[13]);

Or(a=a[14],b=b[14],out=out[14]);

Or(a=a[15],b=b[15],out=out[15]);

}

10.MUX16

CHIP Mux16 {

IN a[16], b[16], sel;

OUT out[16];

PARTS:

Mux(a=a[0],b=b[0],sel=sel,out=out[0]);

Mux(a=a[1],b=b[1],sel=sel,out=out[1]);

Mux(a=a[2],b=b[2],sel=sel,out=out[2]);

Mux(a=a[3],b=b[3],sel=sel,out=out[3]);

Mux(a=a[4],b=b[4],sel=sel,out=out[4]);

Mux(a=a[5],b=b[5],sel=sel,out=out[5]);

Mux(a=a[6],b=b[6],sel=sel,out=out[6]);

Mux(a=a[7],b=b[7],sel=sel,out=out[7]);

Mux(a=a[8],b=b[8],sel=sel,out=out[8]);

Mux(a=a[9],b=b[9],sel=sel,out=out[9]);

Mux(a=a[10],b=b[10],sel=sel,out=out[10]);

Mux(a=a[11],b=b[11],sel=sel,out=out[11]);

Mux(a=a[12],b=b[12],sel=sel,out=out[12]);

Mux(a=a[13],b=b[13],sel=sel,out=out[13]);

Mux(a=a[14],b=b[14],sel=sel,out=out[14]);

Mux(a=a[15],b=b[15],sel=sel,out=out[15]);

}

11.OR8WAY

CHIP Or8Way {

IN in[8];

OUT out;

PARTS:

Or(a=in[0],b=in[1],out=w1);

Or(a=in[2],b=in[3],out=w2);

Or(a=in[4],b=in[5],out=w3);

Or(a=in[6],b=in[7],out=w4);

Or(a=w1,b=w2,out=w5);

Or(a=w3,b=w4,out=w6);

Or(a=w5,b=w6,out=out);

}

12.MUX4WAY16

CHIP Mux4Way16 {

IN a[16], b[16], c[16], d[16], sel[2];

OUT out[16];

PARTS:

Mux16(a=a,b=b,sel=sel[0],out=w1);

Mux16(a=c,b=d,sel=sel[0],out=w2);

Mux16(a=w1,b=w2,sel=sel[1],out=out);

}

13.MUX8WAY16

CHIP Mux8Way16 {

IN a[16], b[16], c[16], d[16],

e[16], f[16], g[16], h[16],

sel[3];

OUT out[16];

PARTS:

Mux4Way16(a=a,b=b,c=c,d=d,sel=sel[0..1],out=tp1);

Mux4Way16(a=e,b=f,c=g,d=h,sel=sel[0..1],out=tp2);

Mux16(a=tp1,b=tp2,sel=sel[2],out=out);

}

14.DMUX4WAY

CHIP DMux4Way {

IN in, sel[2];

OUT a, b, c, d;

PARTS:

Not(in=sel[0],out=nsel0);

Not(in=sel[1],out=nsel1);

And(a=in,b=nsel0,out=a1);

And(a=a1,b=nsel1,out=a);

And(a=in,b=sel[0],out=b1);

And(a=b1,b=nsel1,out=b);

And(a=in,b=nsel0,out=c1);

And(a=c1,b=sel[1],out=c);

And(a=in,b=sel[0],out=d1);

And(a=d1,b=sel[1],out=d);

}

15.DMUX8WAY

CHIP DMux8Way {

IN in, sel[3];

OUT a, b, c, d, e, f, g, h;

PARTS:

DMux4Way(in=in,sel=sel[0..1],a=a1,b=b1,c=c1,d=d1);

DMux4Way(in=in,sel=sel[0..1],a=e1,b=f1,c=g1,d=h1);

Not(in=sel[2],out=nsel2);

And(a=a1,b=nsel2,out=a);

And(a=b1,b=nsel2,out=b);

And(a=c1,b=nsel2,out=c);

And(a=d1,b=nsel2,out=d);

And(a=e1,b=sel[2],out=e);

And(a=f1,b=sel[2],out=f);

And(a=g1,b=sel[2],out=g);

And(a=h1,b=sel[2],out=h);

}

932

932

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?