前言:本文是Farrow滤波器相关三篇论文的学习笔记,介绍用于数字信号任意速率转化的Farrow 滤波器,主要包括原理与架构,文章分为三个部分(1)重采样过程的数学建模;(2)Farrow算法推导;(3)Farrow滤波器实现架构。

Farrow架构的两种理解:

(1)对数模混合重采样过程用全数字滤波器形式近似,并基于多项式插值公式计算滤波器系数。(完整的理论与推导,对应本文的行文组织顺序)

(2)拉格朗日多项式插值的高效数字实现。(对应最终的架构实现)

阅读提示:

如果只关注Farrow架构如何实现,可先看公式(2)中重采样的数学模型,然后直接跳到2.3小节看基于拉格朗日多项式插值对应的数字实现架构以及第三章节中的实现,属于“make-it"。前面的内容第一到第二章节是只是为了建立完整的理论基础,是属于“tell-a-good-story”。

一、问题建模

1.1 背景

数字信号处理系统中,不同处理模块往往工作在不同的处理速率,因而需要对信号进行速率转换。

Farrow滤波器通过插值实现数字信号的采样速率转换,尤其是转换前后速率比值为无理数时(incommensurate,irrational)。当转换前后速率比值可表示为整数比时,可通过更为简单的插值/抽取+抗镜像/混叠滤波实现,此处不再赘述。

本文主要讨论Farrow滤波器用于任意速率的插值转换。

1.2 重采样过程

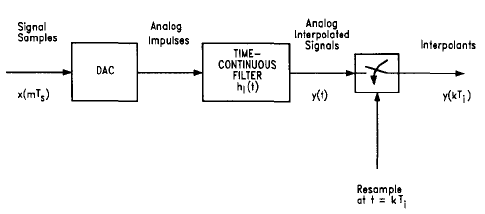

Farrow滤波器为全数字处理架构,但其插值过程仿照的是下图所示的基本的数字/模拟混合重采样架构。

对重采样架构的数学建模是Farrow滤波器的核心part!理解这个重采样过程也就理解了整个Farrow架构背后的原理,后面剩下的只是公式推导和实现简化了。

基于DAC与ADC的重采样过程(图自参考文献[1])

二、Farrow数字滤波算法

Farrow算法本质:对于数模混合重采样过程的纯数字运算的近似,并以数字滤波器的架构实现。

下面,研究如何用数字滤波器结构来近似实现(2)中的重采样过程:

2.1 数字滤波的近似形式

2.2 插值系数的确定

2.3 拉格朗日多项式插值

Farrow滤波器架构,本质其实就是拉格朗日多项式插值的数字高效实现形式,前文一系列的建模与推导是为了给更多泛化的实现架构提供理论基础。

下面,从拉格朗日多项式插值的角度出发,推导Farrow滤波器结构以及相应系数。

Q2:为什么不用简单的一阶线性插值?

A2:Farrow滤波器阶数越低,通带平坦性越差,带外限制能力越弱。对于窄带信号,信号带宽<<采样率时,线性插值也能保障性能。而对于宽带信号,阶数过低时一是带内会畸变,二是插值过程中带外镜像无法被有效抑制,继而在重采样时造成混叠。

Q3:滤波器阶数越高越好吗?

A3:理论上来说是的,但当阶数增大时,计算复杂度幂次增长,系统延迟增大,因此实际系统中阶数不能过大,一般不超过4阶。

三、Farrow的数字架构实现

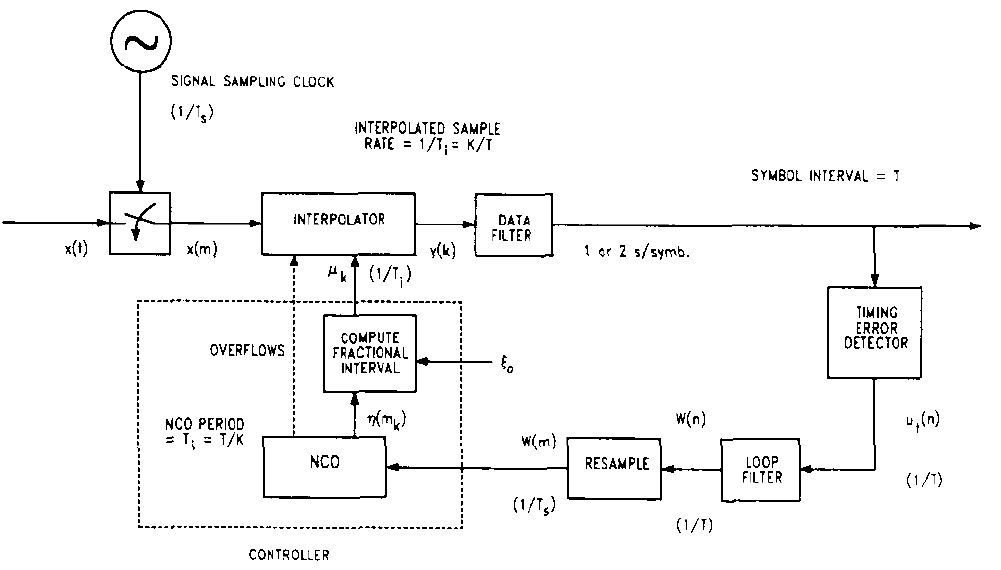

Farrow滤波器的架构主要由两个模块组成:(1)定时控制模块;(2)多项式插值模块。

-

定时控制模块 由计数控制振荡器NCO(number-controlled oscillator)和环路滤波器共同控制前后两套时钟 的转换,完成基点样本点 位置的确定与分数阶间隔 的计算。

定时控制模块(图自参考文献[1])

-

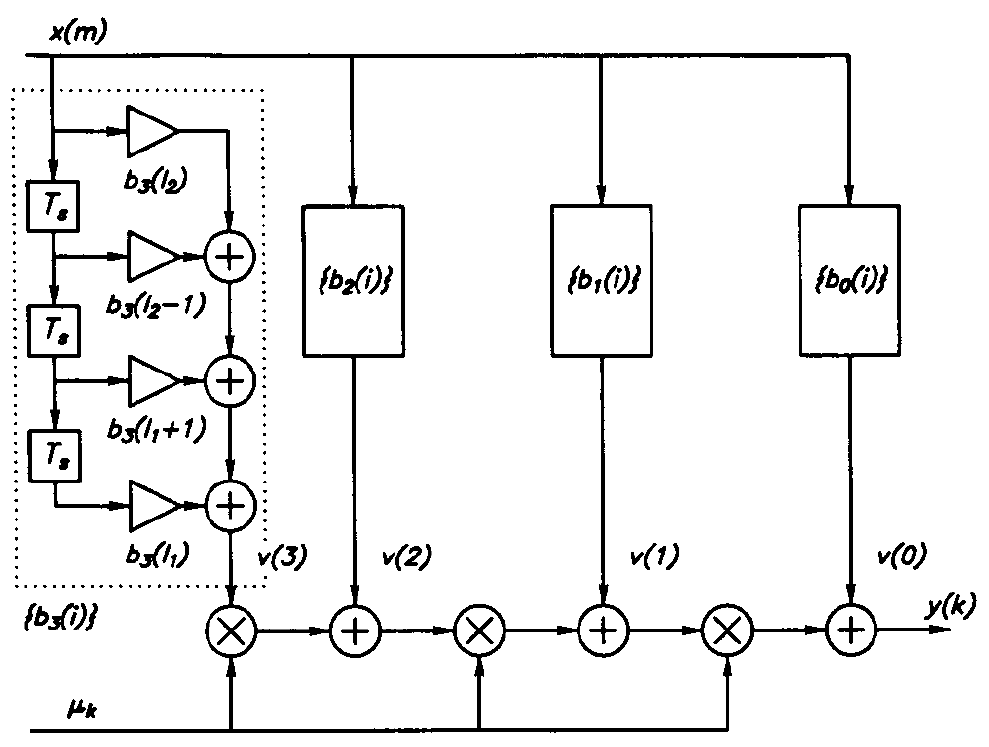

多项式插值模块 根据Homer法则三阶多项式的和可写为: 据此,构建方形滤波器架构,高效实现多项式插值:

三阶Farrow插值滤波器架构,源自参考文献[2]

Q5:转换前后速率可以差异很大吗?

A5:由于滤波器阶数有限,Farrow架构要求输入输出采样率量级较为接近,才能保证插值误差较小.

Matlab有封装好的函数"dsp.FarrowRateConverter"可以实现Farrow Rate Convert的功能仿真:

frc_fil = dsp.FarrowRateConverter('InputSampleRate',fs_in, ...

'OutputSampleRate', fs_out, ...

'PolynomialOrder',N_order, ...

'Specification','Polynomial order');

out = frc_fil(in); % only column vector is allowed注:(1)仅支持列向量的运算;(2)支持的最大多项式阶数为4阶;(3)允许自定义滤波器组的系数;(4)基本参数:输入采样率fs_in,输出采样率fs_out,插值阶数N_order。

参考文献

[1] F. M. Gardner, "Interpolation in digital modems. I. Fundamentals," IEEE Transactions on Communications, vol. 41, no. 3, pp. 501-507, March 1993.

[2] L. Erup, F. M. Gardner and R. A. Harris, "Interpolation in digital modems. II. Implementation and performance," IEEE Transactions on Communications, vol. 41, no. 6, pp. 998-1008, June 1993.

[3] C. W. Farrow, "A continuously variable digital delay element,"1988., IEEE International Symposium on Circuits and Systems, Espoo, Finland, 1988, pp. 2641-2645 vol.3.

5210

5210

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?