在进行数字电路实验时,经常需要对时钟信号进行分频,以实现输出不同频率的时钟信号。

以下题为例:要求将50MHz的时钟信号进行分频,产生1MHz的时钟信号。其Verilog描述如下:

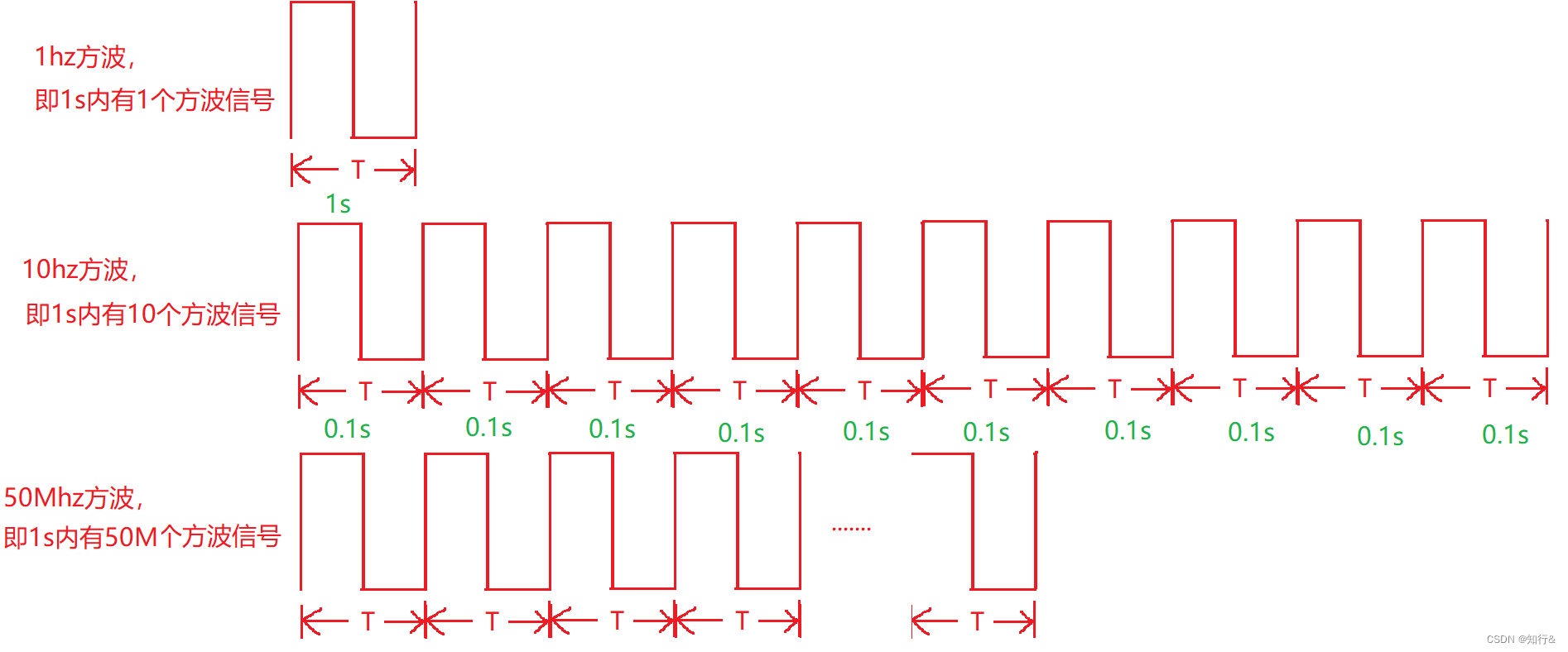

首先,精确理解一下50MHz的时钟频率究竟是什么概念?

50MHz的时钟信号,其周期为1/50M秒,1秒有50M个方波信号。

module example(clk_out,clk_in);

output reg clk_out;

input clk_in;

reg [30:0]cnt;

always@(posedge clk_in)

begin

if(cnt==24999999)

begin

clk_out<=!clk_out;

cnt<=0;

end

else

cnt<=cnt+1;

end

endmodule

端口列表非常简单,只有一个输入的时钟信号和一个输出的时钟信号。

50MHZ÷1HZ=50000000,那么可将50MHZ的时钟信号进行计数,设置初始值cnt=0。当计数cnt没有达到50000000/2即25000000次时,cnt自增1;

当计数cnt达到50000000/2即25000000次时。clo_out <= ~clkout,即翻转,并且cnt从0开始重新计数。

如此反复即可实现clk_out的输出信号为1HZ。

本文内容结束,如有不足,欢迎交流!

238

238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?