文章目录

- APB:2.0 3.0 4.0

- AHB: 2.0 3.0 5.0

- AXI: 3.0 4.0

1.AMBA-APB 协议

APB:Advanced Peripheral Bus,用于慢速外设模块。

APB主要用在低速且低功率的外围,可针对外围设备做功率消耗及复杂接口的最佳化。APB在AHB和低带宽的外围设备之间提供了通信的桥梁,所以APB是AHB的二级拓展总线。

- 它的架构不像AHB总线是多主设备的架构,主要应用在低带宽的外设上,如UART、I2C。

- APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些request/grant信号。

- APB的协议十分简单,甚至不是流水的操作,固定两个时钟周期完成一次读或写的操作,支持最大32-bit的数据位宽。

- 其特性包括:两个时钟周期传输,无需等待周期和回应信号,控制逻辑简单,只有四个控制信号。由于APB的两个通道没有自己的握手信号,因此两个通道不会同时使用,即不支持读写并行操作

APB Slave(UART…):左侧的输入信号是来自bridge的,输出只有一个,那就是读出来的数据送给AHB

1.1 APB信号

APB2协议主要定义了基本的总线接口,没有握手协议,只有基本的读写传输

APB3增加了PREADY,PSLVERR信号。PREADY用于表示APB传输的完成,可以实现slave的等待功能。PSLVERR用以指示slave的错误状态。

APB4增加了PPROT,PSTRB。PPROT信号实现安全和非安全的数据传输,可实现系统在不同安全属性的控制传输,保证系统的安全性。PSTRB信号用于实现部分数据的写操作,可以指示一笔传输中的一部分数据有效。PPROT可实现APB传输的保护控制。PPROT[0]表示不同优先级的传输,可实现salve对不通优先级数据的特殊处理操作。PPROT[1]表示对不同安全属性的数据传输。PPROT[2]用来指数此时传输是数据传输还是指令传输。APB的这个升级是集成的AHB与AXI的属性,也是为了更加符合现在系统设计的需求。

1.2 APB传输时序

apb通过实现状态机来实现

对每一笔数据的传送,均需花2个周期的时间

一是SETUP cycle,另一个是ENABLE cycle

1.3 APB读写

Write/read transfer with no wait states

- PENABLE表示传输的ENABLE阶段的开始

- PREADY表示slave可以在PCLK的下一个上升沿完成传输

Write/read transfer with wait states

Write

Read

- 当ENABLE阶段开始时,如果PENABLE拉高时,PREADY为低,那么传输会一直等待,直到PREADY拉高为止

- 当PENABLE拉低时,PREADY可以取任何值。

- 当PREADY保持低位时,其他信号应保持不变

- 建议地址和写信号在传输后不要立即改变,而是保持稳定,直到另一个访问发生。这样可以降低功耗

关于APB2.0协议,PENABLE信号是否必要?

从时序来说是不必要的

从组合逻辑来说,节省功耗

关于APB协议,在第一个clk,控制信号先使能(PSEL,PADDR、PWRITE),在第二个clk,使能信号(PENABLE)拉高,读写数据(DATA)才有效,你认为APB协议为什么要这样做?不能在一拍中做完所有这些事情吗?

APB协议将片选信号(PSELx)和地址信号(PADDR)与使能信号(PENABLE)分开是出于以下原因:

首先,在访问外设时,需要确保外设选择的正确性。在一些数据交换系统中,当多个外设共享相同的总线时,必须使用片选择信号来告诉这个信号表示处理器要对哪个外设进行数据访问或者控制操作。

其次,在处理器和外设之间的通信过程中,需要精确地检测时序。如果将片选计时、地址传输和数据传输全部放在一个时钟拍中完成,并且在单个clk周期内直接进行数据读取或写入,则会面临会时序问题难以解决的情况。在拆分成两拍之后,可以明确地区分每个步骤的执行时间,从而保证数据传输的正确性和时效性。

为了确保通信的精度,APB协议通过两个时钟拍周期的方式来逐步推进访问事务的状态,从而保证了在访问外设时信号传递的准确性。此外,分别分阶段执行访问事务,还能够有效解决由于信号传输延迟而导致的发生时序问题的潜在风险。

APB的外设基本是由寄存器组成的,访问寄存器

系统通过软件轮询的方式不断查看状态寄存器,判断外设是否ready去接收处理器信号

从APB3.0开始引入硬件的方式,引入了PREADY信号

1.4 APB-slave

一个APB4 Slave的Demo,简化起见,不支持PPROT信号,PREADY常为1,不支持wait state,PSLVERR常为0,不返回错误。

(APB的外设可以选择产生或者不产生error response,如果不产生的话,只需要把连接APB外设的模块(比如APB bridge)对应PSLVERR端口接0即可)

IP内部register的定义,这个IP很简单,没有control register和status register,只有data register。

2.AMBA-AHB 协议

AHB:Advanced High-performance Bus,用于高性能、高时钟工作频率模块。

- AHB的ADDR没有分读和写的ADDR:AHB是半双工的,读和写不能同时进行

- AHB总线将微控制器,RAM,外部存储器接口,DMA等各种具有AHB总线接口的控制器连接起来,构成独立的完整的SoC系统

- AHB-Lite Slave一般是内存器件(MCU),外部存储器接口和高带宽外围器件

AMBA2.0-AHB2.0

- 某一时刻只允许一个主设备使用总线;

- 仲裁器(Arbiter)用于仲裁多个主设备(Master)同时访问总线的情况

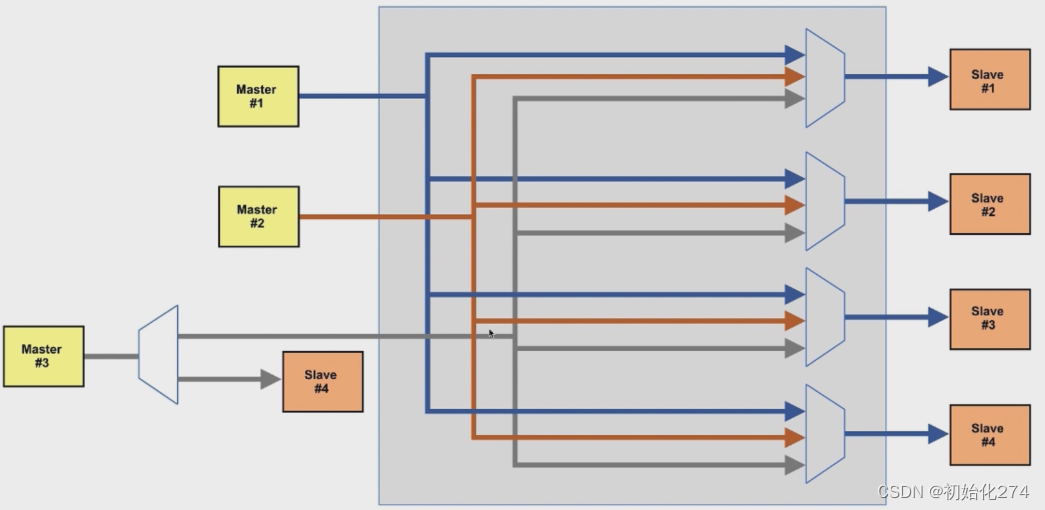

AMBA3.0-AHB-lite

- AHB-lite单个master访问多个slave

- AHB-lite多个master访问多个slave

或

- 实际应用

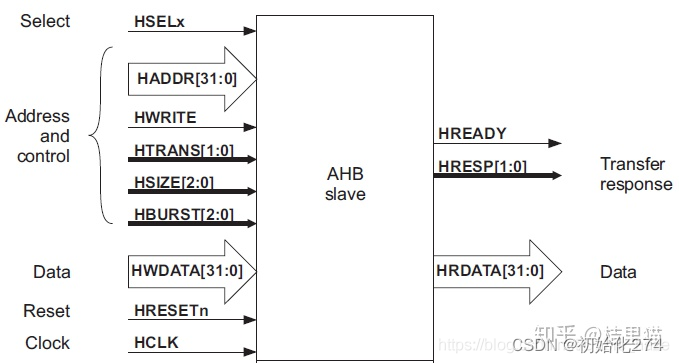

2.1 AHB信号

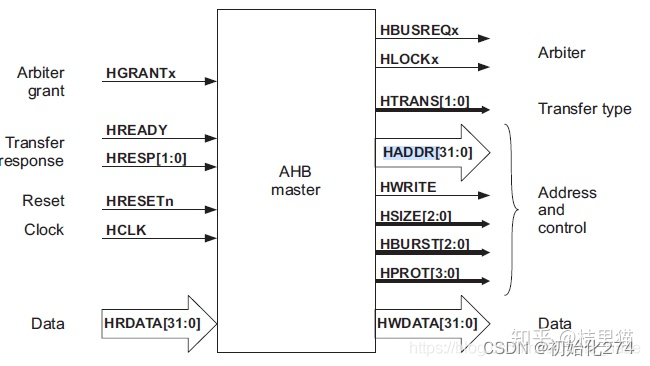

AHB2.0

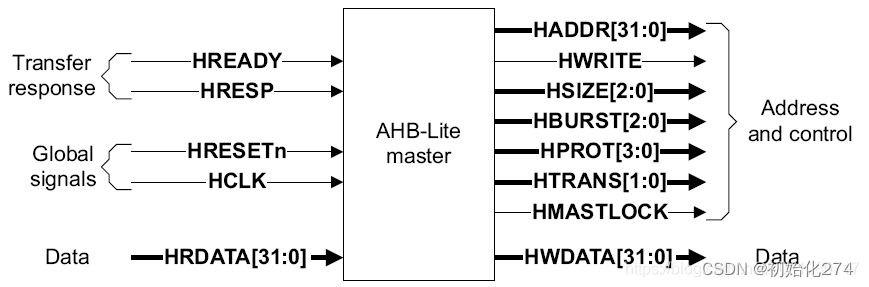

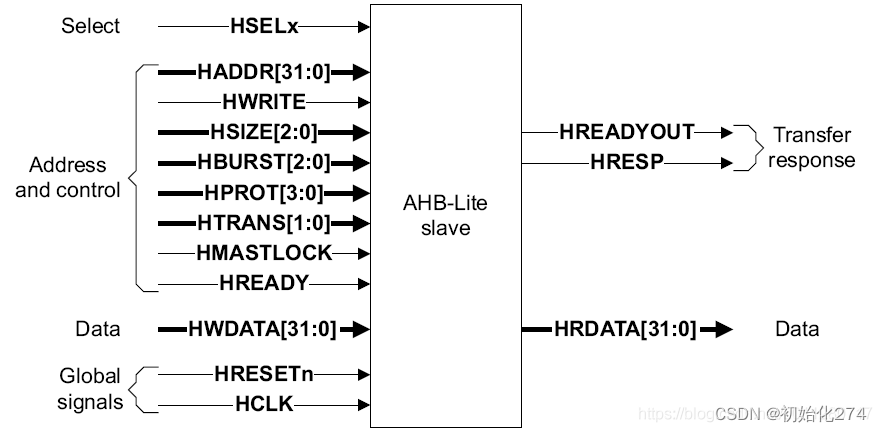

AHB-lite

AHB-Lite Master接口

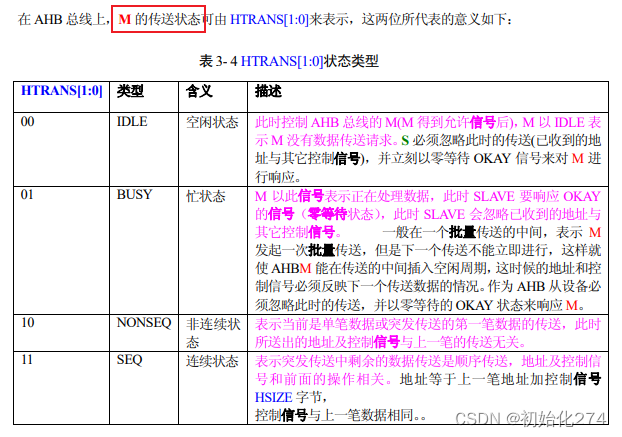

HTRANS[1:0]//指示当前传输类型,可以是:IDLE/ BUSY/ NONSEQUENTIAL/ SEQUENTIAL

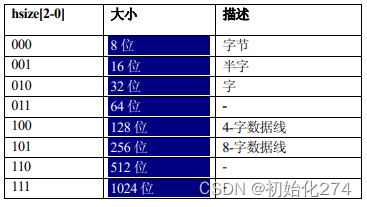

HSIZE[2:0]//传输大小,标识数据位宽,表示一个时钟周期传输的数据的位宽

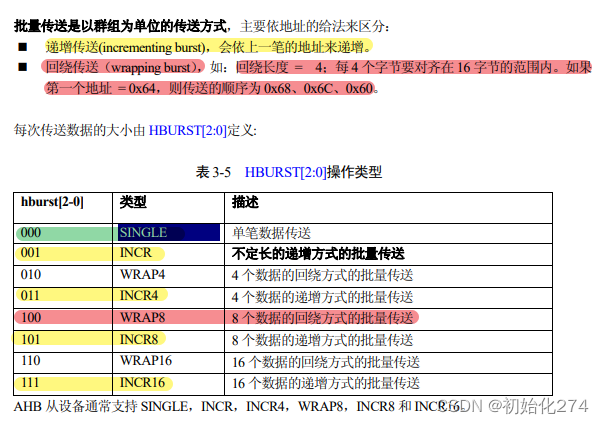

HBURST[2:0]//Burst类型,支持固定长度的4,8和16拍,即一次连续传输要传多少个数

- NONSEQUENTIAL只能对应single或seq的第一笔

- single对应HTRANS只能为IDLE/NONSEQUENTIAL

- HSIZE[2:0]与 HBURST[2:0]两个信号可合起来定义回绕地址的范围。

AHB总线的地址位宽和数据位宽(HR/WDATA[31:0])一般都是32bit,一个字节(8位)占用一个地址空间

HSIZE是字节(byte/8位),一个时钟周期完成一个8bit数据传输,地址增量是0x1,HR/WDATA[31:0]32bit需要4个时钟周期

HSIZE是半字(half word/16位),一个时钟周期完成2个8bit数据传输,地址增量是0x2,HR/WDATA[31:0]32bit需要2个时钟周期

HSIZE是字(word/32位),一个时钟周期完成4个8bit数据传输,地址增量是0x4,HR/WDATA[31:0]32bit需要1个时钟周期

- HSIZE必须小于或等于数据总线位宽(HRDATA/HWDATA)。

例如,一个32位数据总线(HRDATA/HWDATA),HSIZE只能是8, 16或32- HSIZE可以实现总线和slave数据位宽的匹配

例如,总线位宽比较低(HRDATA/HWDATA),是32bit

需要一个高带宽的slave,是64bit的,HSIZE就设置为64bit来告诉总线一个数是64bit的

总线的处理就是,第一个数放到slave的DATA[31:0],第二个数放到slave的DATA[63:32](顺序可能相反),两个整合在一起再把64位整体传给slave。

- 既然每次(每个beat)master都要传对应的地址,slave接收到地址之后对应进行读/写操作,为什么需要还要HBURST信号来告诉slave有几个burst?

一般来说,确实slave按部就班根据地址操作就行了。但是对于有的slave,提前知道了burst长度有助于提高效率,比如提前腾出burst长度的buffer。

Burst传输就是提高了传输效率。如果不使用burst,普通访问模式下,主设备发出的传输命令到达从设备,由于仲裁等原因,传输会产生一定的延时。如果主设备读一个数据,处理一个数据的话,由于延时的存在,处理速度会极低。在进行突发传输时,只要发送一次地址,内存就会依次地自动对后面相应数量的存储单元进行读/写操作。而不再需要控制器连续地提供访问地址。所以,第一次数据的传输需要若干个周期,而其后每个数据只需一个周期的即可获得。AHB-Lite Slave接口

- 多了一个HSELx信号,该信号是从AHB译码器用来选择哪个Slave的信号

- 多了一个HREADY信号,该信号提示Master和所有的Slave,先前的传输完成

如果单个master对单个slave,那HREADYOUT要与HREADY相连,然后把HREADY接到master和slave上。

如果是单个master对多个slave,那就要把各个slave的HREADYOUT通过一个MUX,产生HREADY相连,然后把HREADY接到master和各个slave上。

如果slave1没完成transfer,slave2和slave3完成,那么此时slave2和slave3要等待slave1完成后,才能接收下一个transfer。

其他信号

HPROT[3:0] //保护控制信号 ,用来定义存取的型态与特性,指示传输是操作码获取还是数据访问,以及传输是特权模式访问或用户模式访问。要求slave具有保护功能,一般不使用

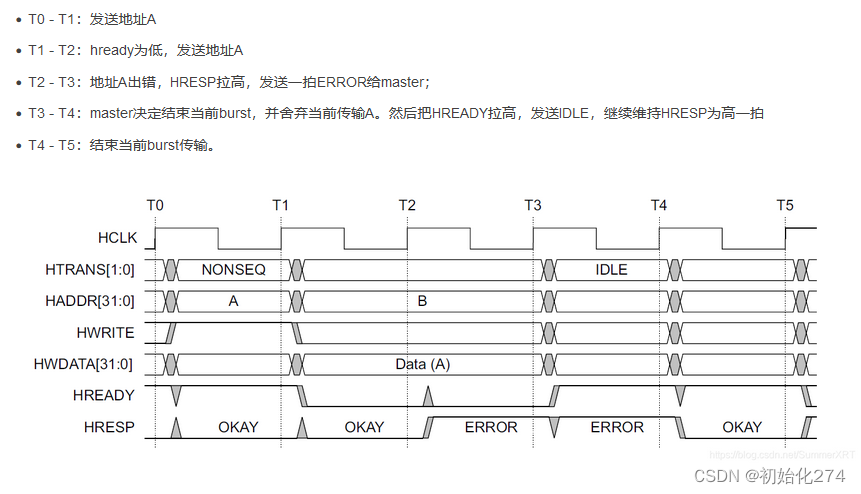

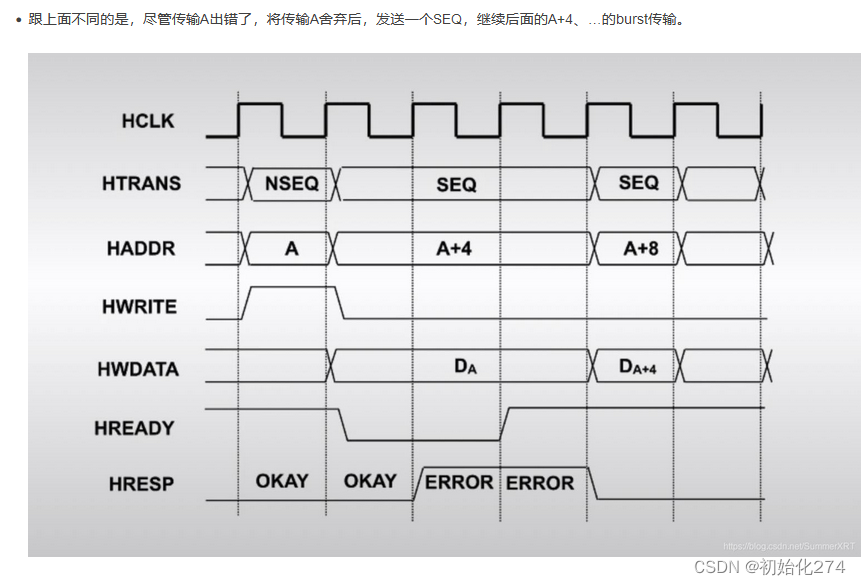

HRESP //传输响应信号,经过多路器处理,给master反馈传输状态。为高时表示传输状态为ERROR,为低时则表示传输状态为OKAY

(1)如果master收到error后,master要取消BURST传输

(2)如果master收到error后,master仍然继续burst传输

ABMA5.0-AHB5.0中新增信号

HMASTLOCK信号,若为高则开启lock 传输

HEXCL和HMASTER[3:0]信号,用以设置Exclusive Transfer,设计中需要有一个Exclusive Access Monitor

HNONSEC信号,指示当前传输是否是个secure或non_secure传输

HPROT[6:4] 用来增加扩展的memory type

HEXOKAY信号,用来表示Exclusive Transfer的成功或失败状态,经过多路器处理,返回给master

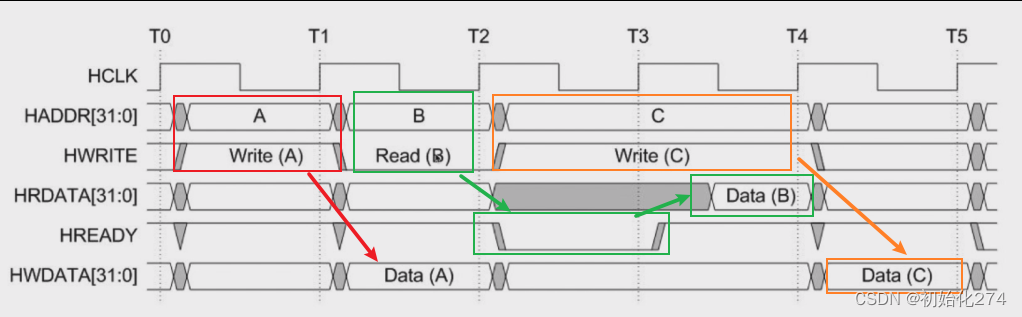

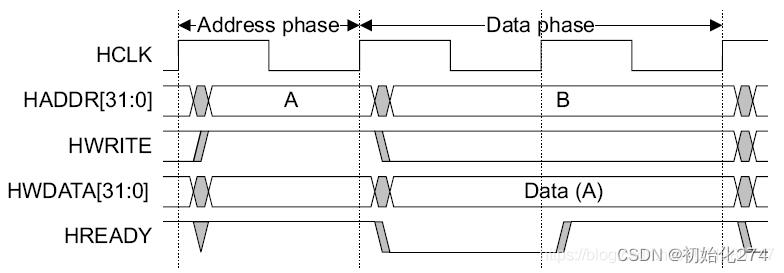

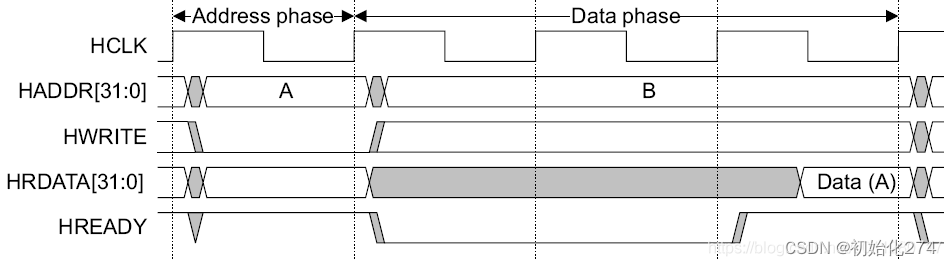

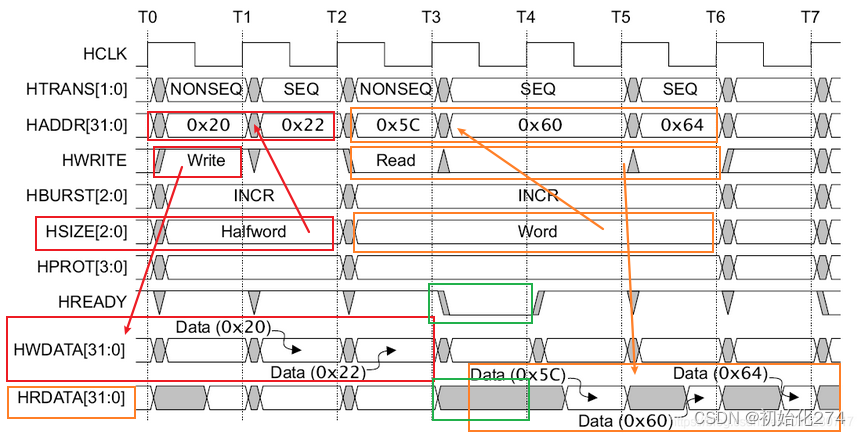

2.2 AHB读写传输时序

2.2.1 基本传输

Write/read transfer with no wait states

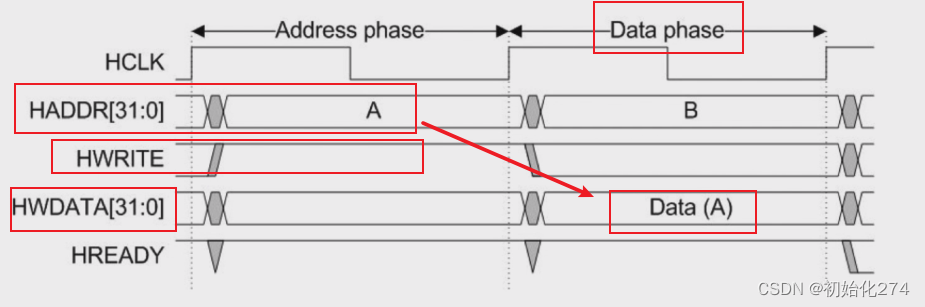

Write

read

Write/read multiple transfer

Pipline流水线

Write/read transfer with wait states

Write

- Master在Address phase送出地址,在Data phase将HWRITE拉高

- 等待Slave的HREADY拉高,否则Master一直将HWDATA维持在Data(A)

- 直到接受到Slave的HREADY拉高,表明一次写传输完成

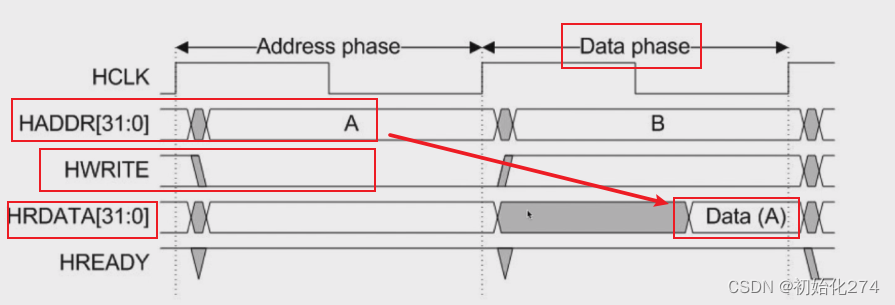

read

- Master在Address phase上驱动HADDR

- Slave将HREADY信号拉低,SLAVE等待若干个Clock之后送出data,在完成传输后,将HREADY拉高,此时Master采样得到Data(A)

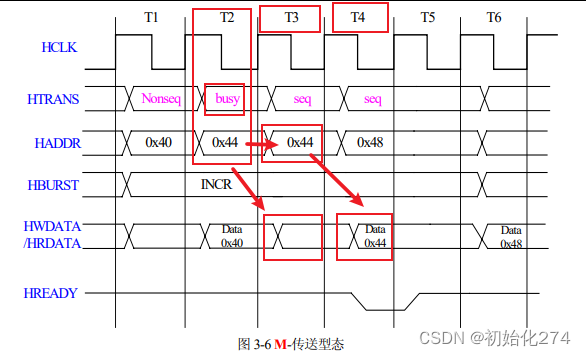

2.2.2 传输状态

HTRANS[1:0],指示当前传输类型,可以是:IDLE/ BUSY/ NONSEQUENTIAL/ SEQUENTIAL

一般不会出现busy

2.2.3 Burst传输

突发(Burst):是指在同一行中相邻的存储单元连续进行数据传输的方式, 连续传输所涉及到存储单元(列)的数量就是突发长度 (Burst Lengths,简称BL)。

就是地址只发一次,首个地址发出就决定了后面的地址是什么。而不是发送一个地址,再传一个数据的方式。

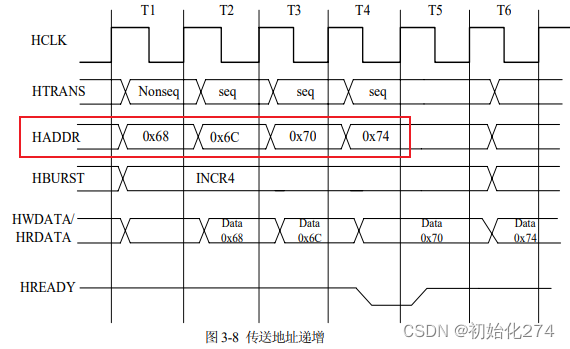

递增传送(incrementing burst)

限长(INCRx)

以递增的方式计算传送地址分别为,0x68、0x6C、0x70、0x74

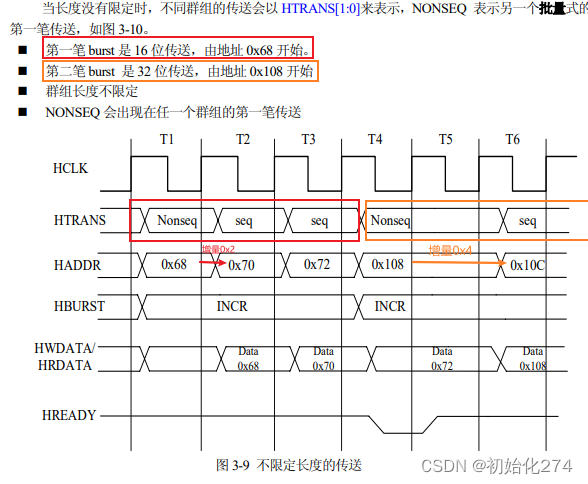

不限长度(INCR)

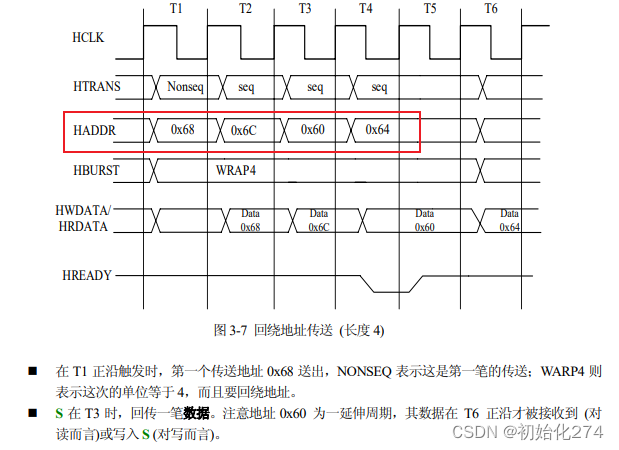

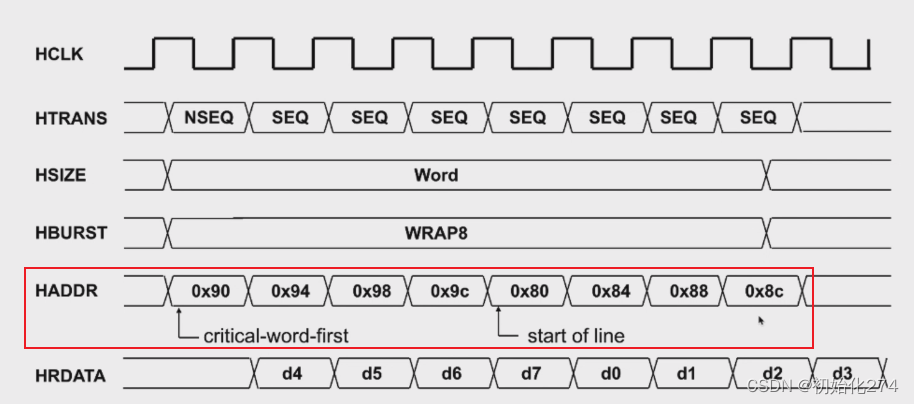

回绕传送(wrapping burst)

限长(WRAPx)

以回绕的方式计算传送地址分别为,0x68、0x6C、0x60、0x64

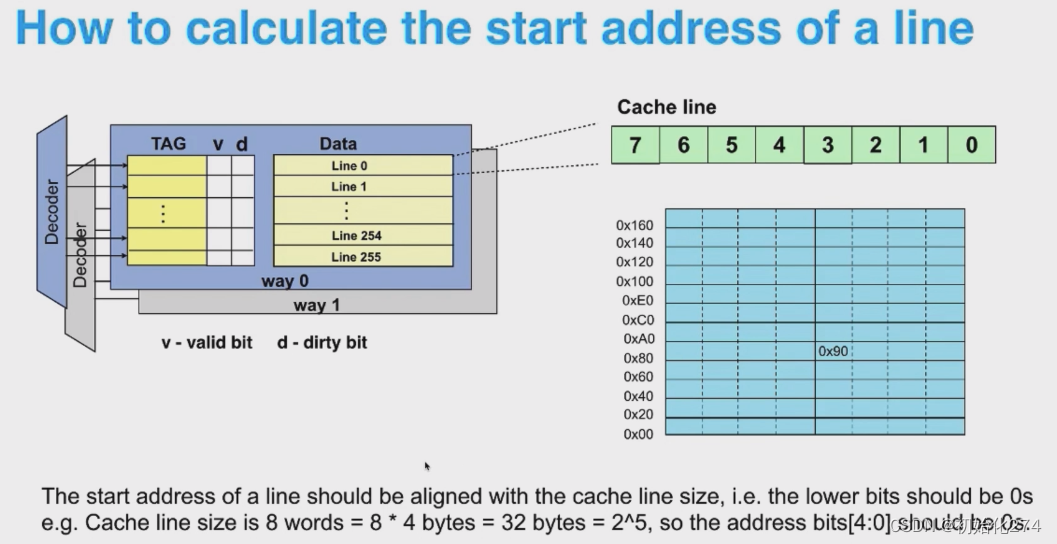

计算开始地址

WRAP起始地址位置的确定?

起始地址根据cache line的大小确定。每个cache line完全是在一个突发读操作周期中进行填充或者下载的,即使CPU只存取1bit的存储器数据,cache也会启动整个存取器访问周期并请求整个数据块。cache line的每条line的地址总是burst length的倍数。比如,cache line是由8个word组成,即4 x 8word = 32 Byte = 256 bit ,所cache line的各条line的起始地址是按加16’h20递增的,即 0x00 、0x20、0x40、0x60、0x80…

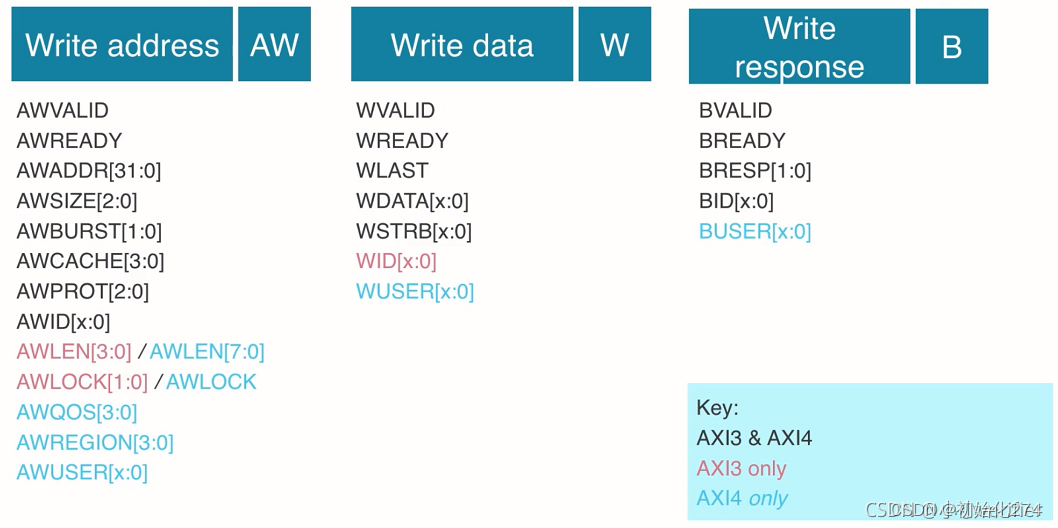

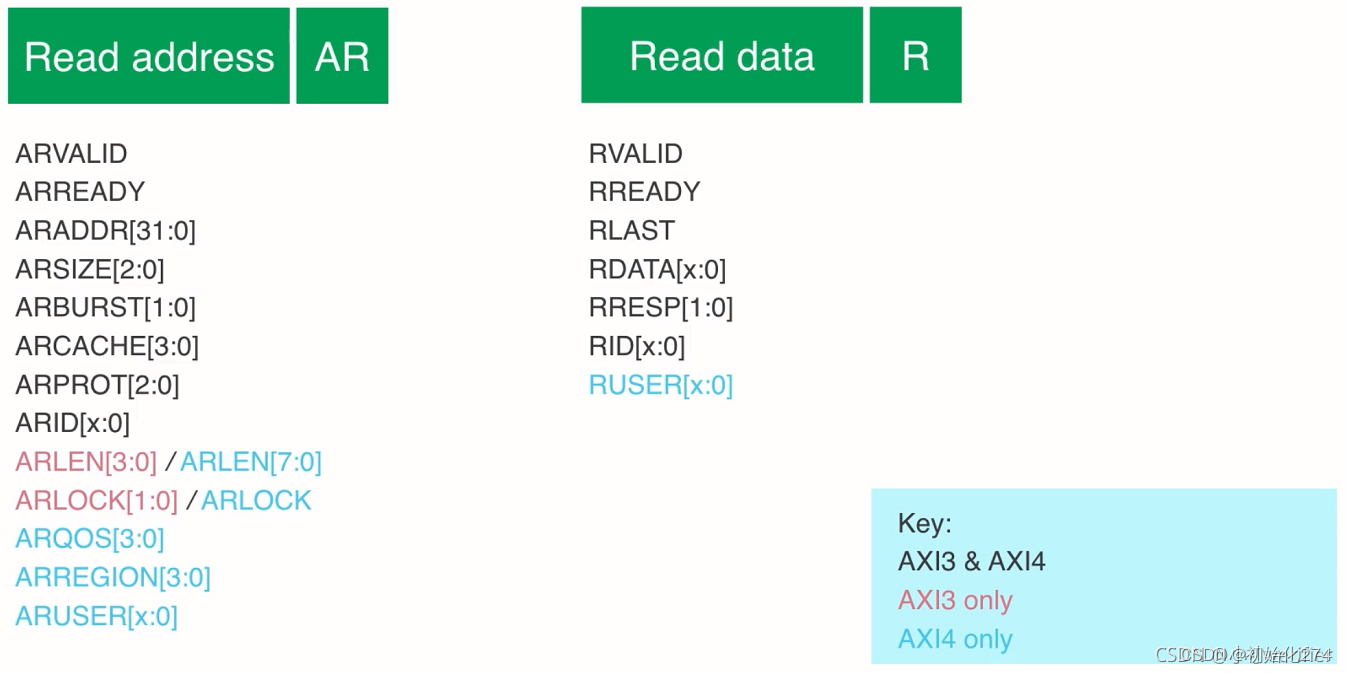

3.AMBA-AXI 协议

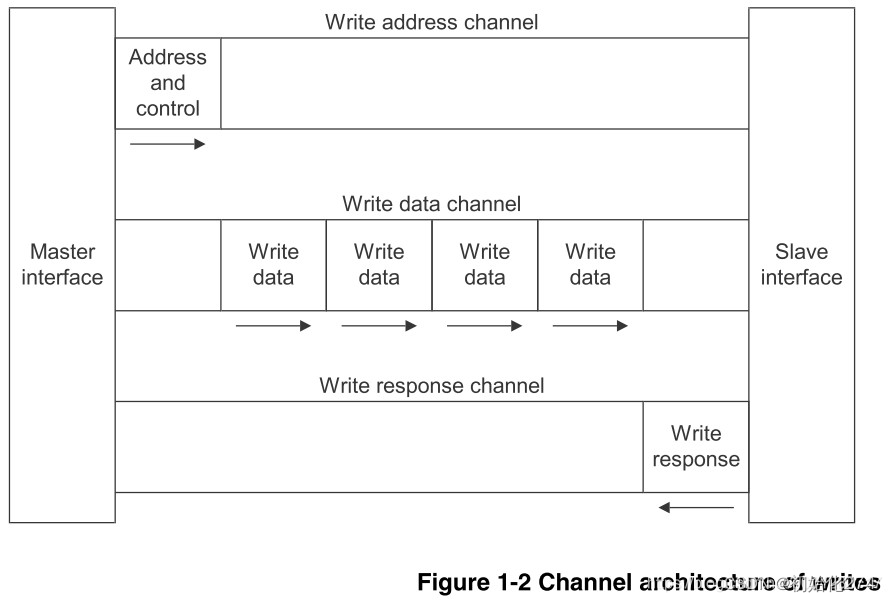

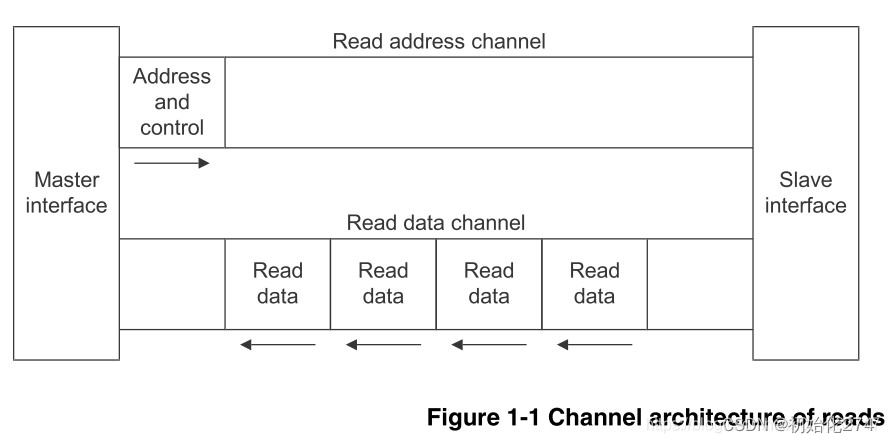

AXI有5个channel,AHB 只有3个channel

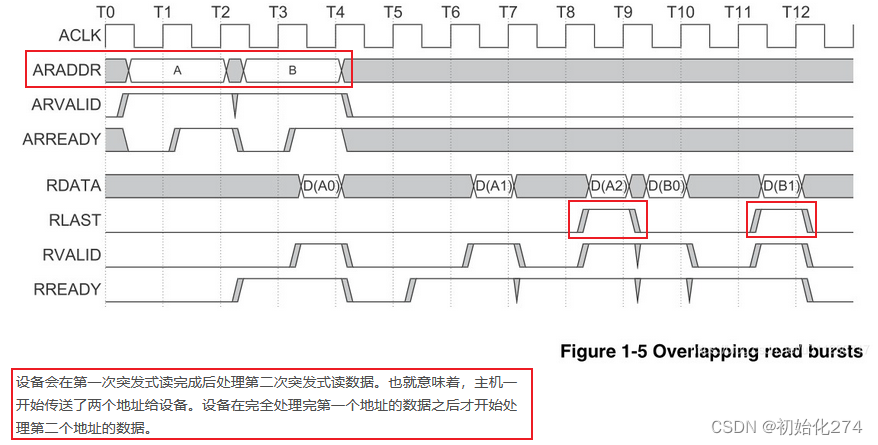

- 读写通道分离; 支持多次对数据操作的请求(multiple outstanding address),一般支持8、16、32个outstanding

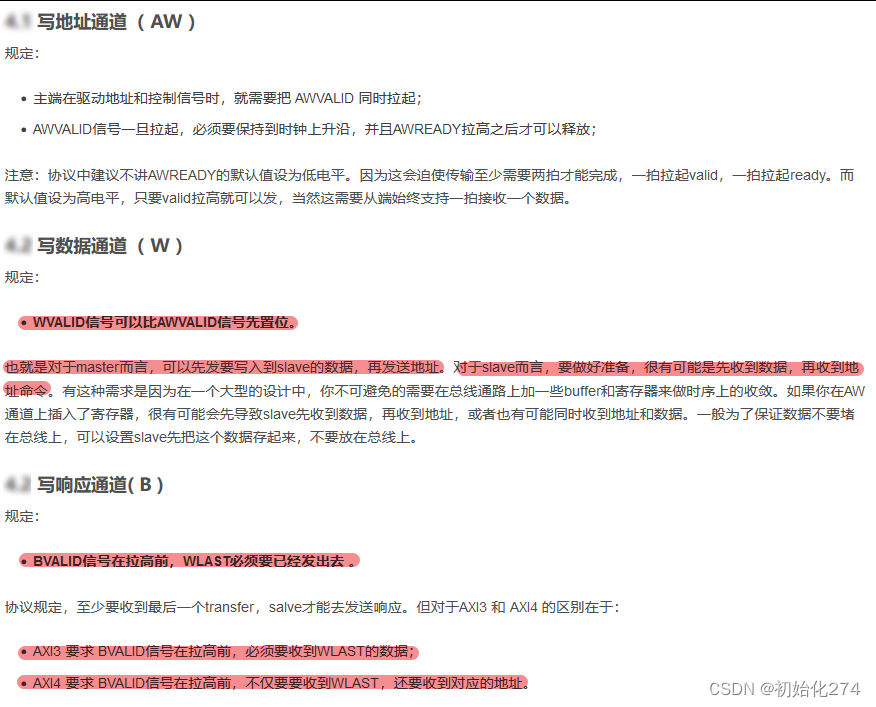

- 写地址和数据之间不是严格的先地址再数据,有些可能是先数据再地址

- 支持不对齐的数据传输

- 支持乱序访问

- burst传输时不需要像AHB那样每笔传输都指定它的burst类型和地址,只需要指定首地址和对应的属性

本节笔记阅读顺序为左边写操作,右边读操作,上下对应

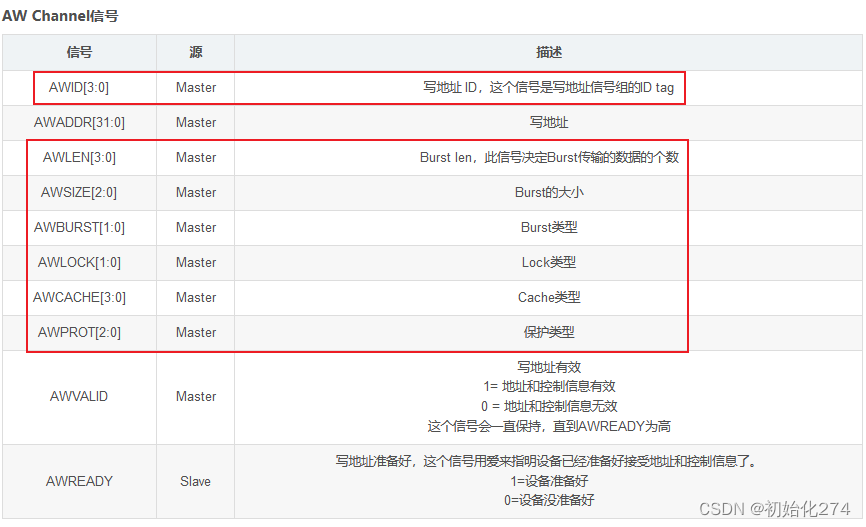

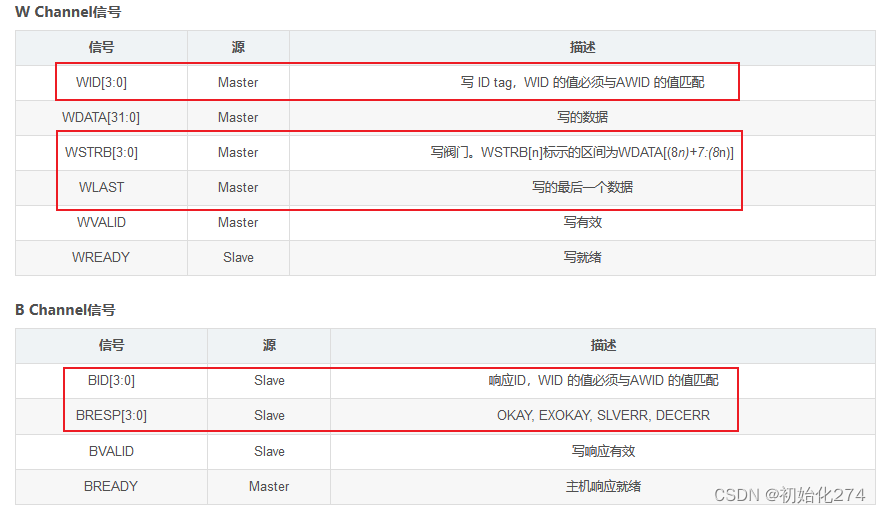

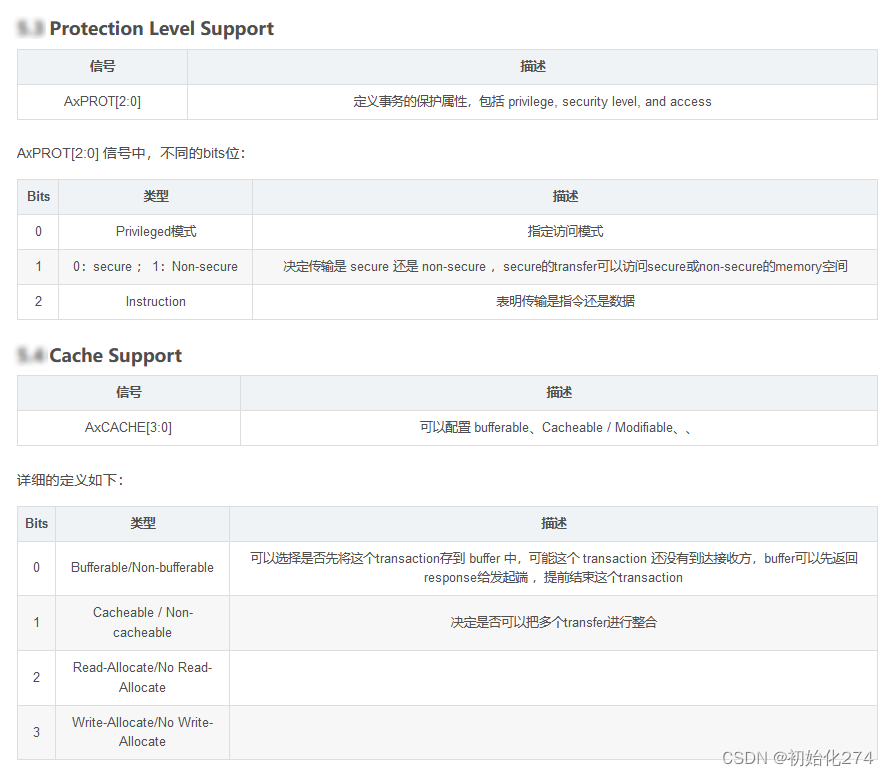

3.1 AXI通道信号

5个单向channel分别对应的信号

这 5 条独立的通道都包含一个信息信号和一个双路的VALD、READY 握手机制。

每个通道都要发送VALD和READY ,当VALID 和READY 同时为高时最后发送传输地址信息或者数据

- 存在三种握手时序:valid先拉起,ready后拉起;ready先拉起,valid后拉起;ready 和 valid 同时拉起

- 可以发送方想发数据,就先拉起 valid,也可以接收方有接受能力,就先准备好ready

- 握手信号间的约束

(1)为了避免死锁问题,协议规定:当 valid 信号被拉高后,不能随意地不经过 ready 信号握手,就将 valid 拉低。就是发送方可以根据自己的需求随时发起传输,不用判断接收方是否能够有能力接收,同时发送方一旦发起传输,就不能随意中止;

(2)对于接收方,如果没有准备好接收就可以不拉高READY,这样就可以反压发送方的传输了,即便接收方在拉高READY后,只要发送方没拉高VALID,接收方还可以拉低READY信号;

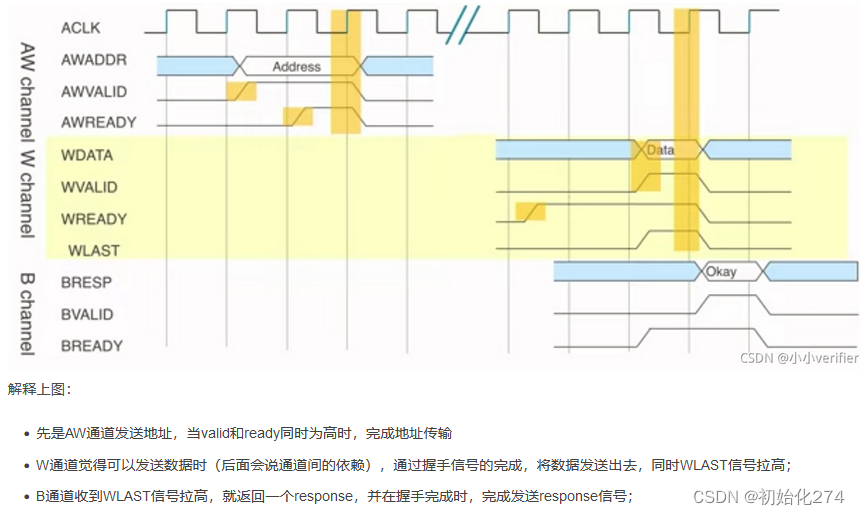

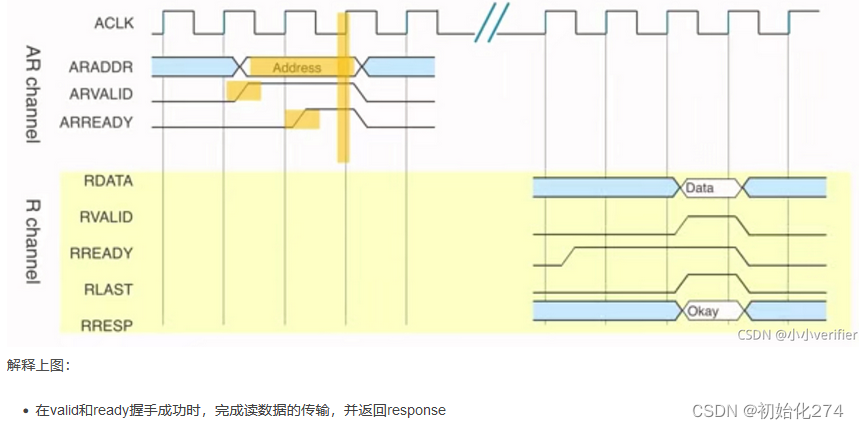

3.2 AXI读写传输时序

3.2.1 single传输

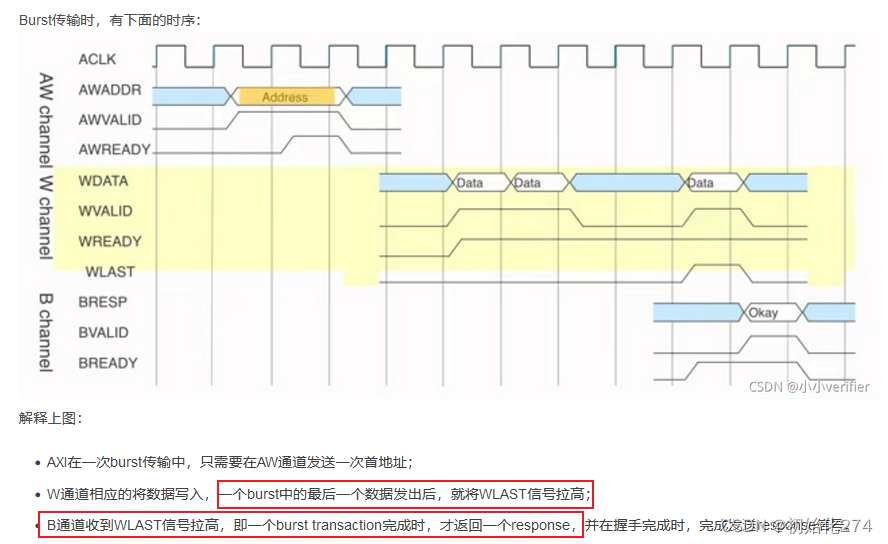

3.2.2 Burst传输

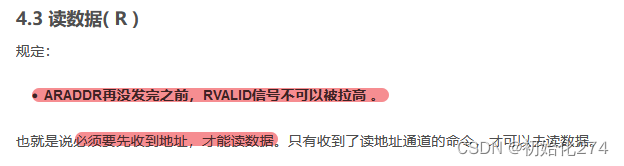

3.3 AXI通道依赖关系

3.4 AXI信号详解

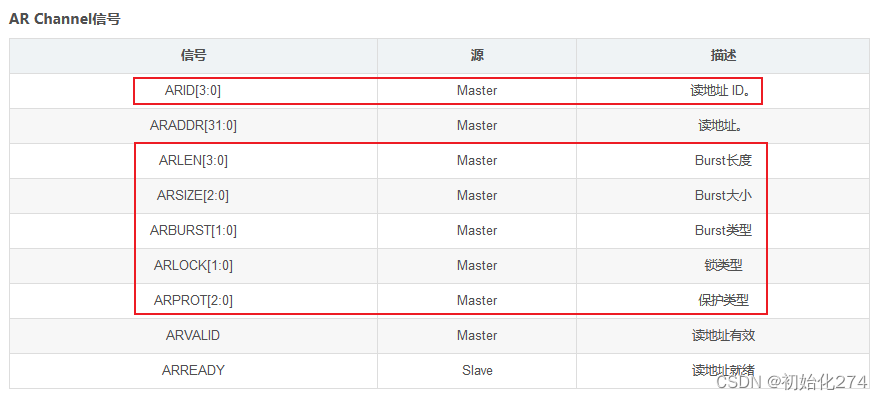

按通道信号详解

按类别详解

AHB的频率为什么比APN频率快?

AHB是流水线传输,位宽大,burst传输,而且APB一次只能传一笔,1笔是2拍,不能burst,多传几笔就浪费好多拍,且AHB没有enable阶段,AHB是单周期读写,AHB的下一拍就可以写下一个数据的地址了,APB两拍,传输多个数据时,APB是2n拍,AHB是n+1拍。

9616

9616

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?