1.变量类型

reg:寄存器型变量,占用存储资源,其赋值必须在always块中,作为接口时只能output reg。

Wire:导线型变量,起导线连接作用,其赋值可以使用assign,作为接口时可input/output wire。

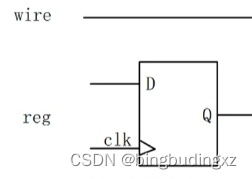

Reg型变量物理结构:在clk上升沿/下降沿存入D中数据,接下来的下降沿/上升沿Q输出数据,中间保持。

变量类型至于变量得赋值方式有关,且内部变量只需要定义变量类型和名称,不需要定义方向。

2.n = {$random}

KaTeX parse error: Expected '}', got 'EOF' at end of input: …产生0~255之间的随机数:{random} %256

%符号为求模运算,返回值为随机数除以256后的余数。

3. 组合逻辑使用阻塞赋值,不使用时钟沿控制的电路;时序逻辑使用非阻塞赋值,由时钟沿控制电路。需要注意的是,在设计电路时,减少非必要组合逻辑的使用,因为信号在组合逻辑下过多会损失时序特性,再用于时序特性时,抓取不到。

同时,由于组合逻辑变化容易出现竞争现象(假设A和B相与,设计A和B同时变化,但由于实际线路延时不能完全相同,因此结果可能产生预料之外的毛刺),导致电路出现毛刺,所以减少使用,提高可靠性。

时序逻辑在时钟上升沿采集,采到毛刺概率低;如果采到,那就是亚稳态。

4.没有赋值过的信号为高阻态;对信号有操作,但信号状态不能确定的为不定态。

5.&按位与,属于位运算符,运算结果位数不变;&&条件与,逻辑运算符,运算结果为1或者0。

6.条件运算符((x)? a : b),相当于if条件语句,举例(嵌套使用):

assign n = ( x > 1 ) ? 1’b1 😦 x < 0 ) ? 1’b1 : 1’b0 ;

5. Else if叠加不宜过多--------条件语句if 、else if理论上可以无限多,但是每一个else if 都会生成一个选择器,过多使用else if,链路变长,延时增多,功能仿真虽然正常,但时序较差,电路会有问题。可理解为:执行else if的语句时长变大,已经大于他本来应该完成的一个clk时间。

8.在数字时钟部分,没有pll核的情况下,只能分频,不可倍频。建议使用IP核(全局时钟)分频倍频,时钟偏斜小。

9. Task任务:

定义任务:

1)可以定义自己的仿真时间

2)可以没有或者有多个类型的变量

3)可以支持计算多个结果,这些结果只能被调用的任务输出或总线端口送出。

任务定义与调用:

定义:

Task my_task;

Input a,b ;

Inout c ;

output d,e ;

......

//执行工作相应语句

......

c = num1 ; //赋初值

d = num2 ; //对任务的输出变量赋值

e = num3 ;

endtask

任务调用:

my_task(v,w,x,y,z);

任务定义变量(a,b,c,d,e)和调用变量(v,w,x,y,z)一一对应的,任务启动时,v,w,x,的值赋给a,b,c,当任务完成后,输出通过c,d,e又赋给x,y,z。

在仿真时可以做如下应用:

initial begin

#1000;

my_task();//执行第一次

#100;

my_task();//执行第二次

End

task my_task;

integer i;

begin

for (i=0;i<500;i=i+1)begin

@(posedge clk);

if(i <=200)begin

a = {$random};

end

else

a = 1'b0;

end

end

@(posedge clk);

a = 1'b1;

end

endtask

3030

3030

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?