有的时候我们自己用Verilog代码写的rom或ram会被quartus ii综合成查找表,并没有使用到block memory资源。

以下是在网上查到的一段说明:(没找到原创链接,都是转载,,,)

To use the ramstyle attribute in a Verilog Design File (.v), specify the synthesis attribute delimited by (* and *) preceding the Variable Declaration of an inferred RAM whose implementation you want to control. Specify the synthesis attribute value as “logic”, “M512”, “M4K”, “M9K”, “M20K”, “M144K”, “MLAB”, or “M-RAM” depending on the type of memory block you want the Quartus II software to use when implementing the inferred RAM. If you use the synthesis attribute on anything but a variable that represents a RAM, or if you specify an illegal value, the Quartus II software ignores that synthesis attribute.

By setting the value to “M512”, “M4K”, “M9K”, “M20K”, “M144K”, “MLAB”, or “M-RAM”, you can choose the type of memory block that the Quartus II software uses when implementing the inferred RAM. If the attribute is set to “logic”, then the RAM is implemented in logic cells.

大致意思是说如果我们想要quartus指定一个寄存器数组在布局布线时使用block memory资源。可以通过代码告诉综合工具(只对寄存器数组有效,其他类型的寄存器综合工具会忽略掉)。

具体方法是这样的:

For example, in the following code, the ramstyle synthesis attribute specifies that the inferred RAM my_ram should be implemented using an M512 memory block:

(* ramstyle = "M512" *) reg [0:7] my_ram[0:63];

那现在来实践一下。

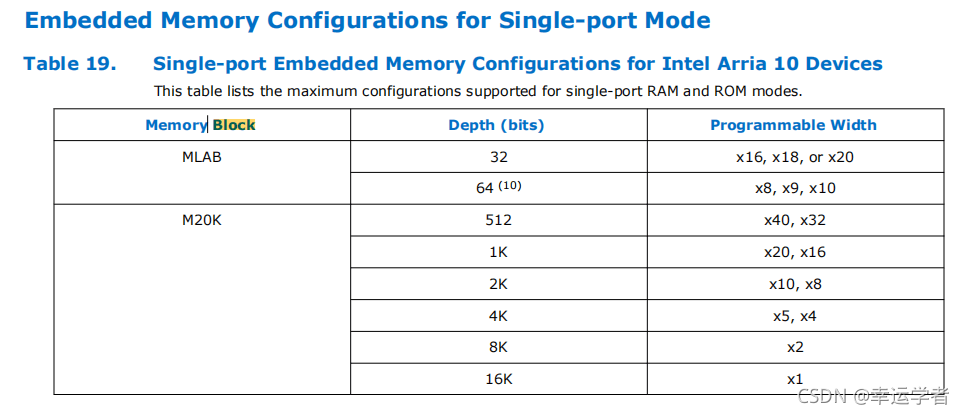

我使用的是Arria 10系列的芯片,先来看看该系列芯片的block memory资源都有什么类型,如下图:

(不同系列的芯片其block memory类型是不一样的,写之前要先查看手册,不要照搬我的)

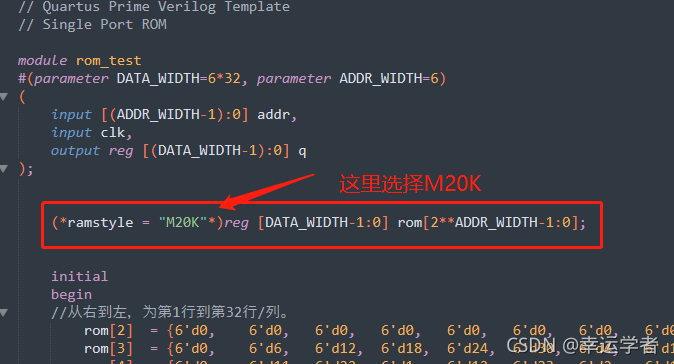

可以看到有MLAB和M20K,那根据上面的例子我就可以把自己写的rom综合到memory block中了。这里我指定到M20K。代码如下图:

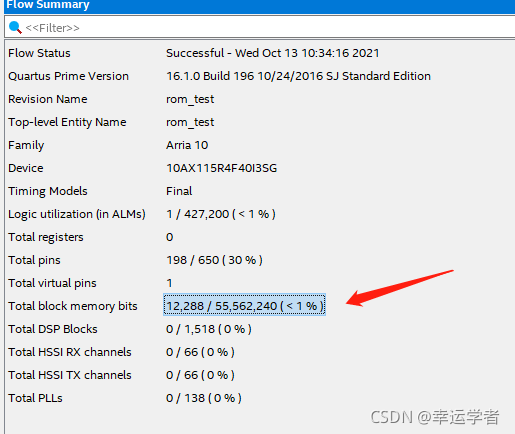

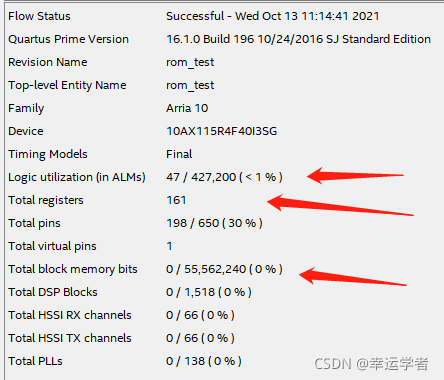

这样就会布局到block memory中了

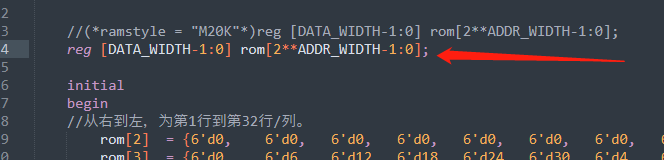

如果不加那个条件

布局的时候就会用寄存器和查找表搭建。

3809

3809

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?