文章目录

1. 前言

之前的文章介绍了如何基于S32K148快速调试TJA1101,链接如下:

这篇文章将接着介绍TJA1101B的硬件设计。

2. 原理图设计

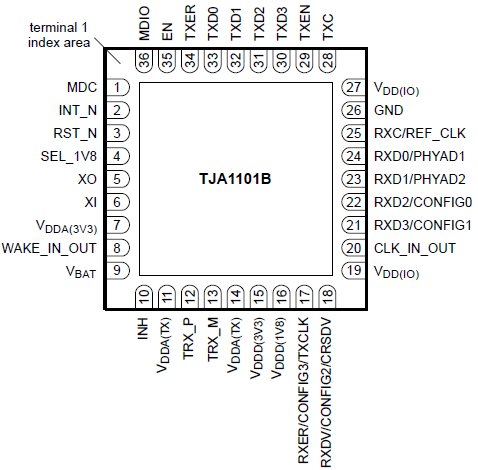

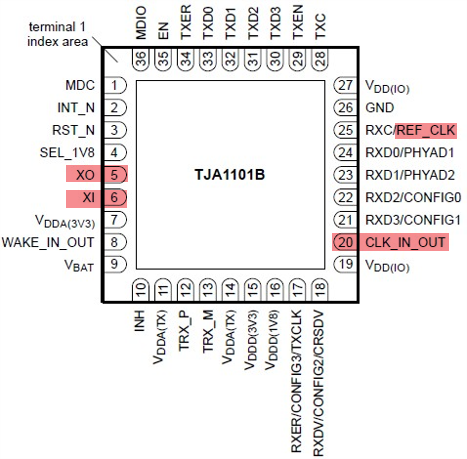

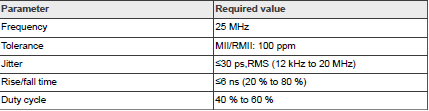

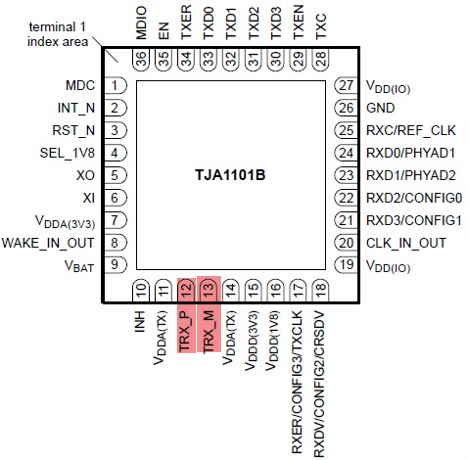

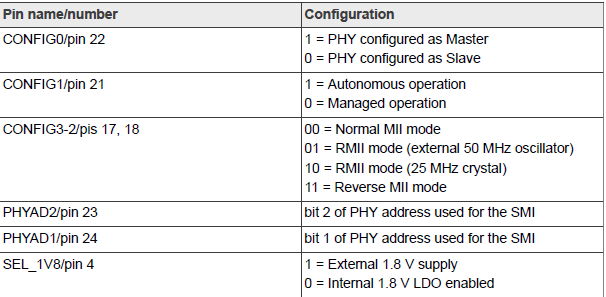

- TJA1101B的引脚分布图如下所示:

因为100base-T1允许全双工通信,所以标准MII接口中用于半双工的

COL和CRS引脚在TJA1101B中没有使用。

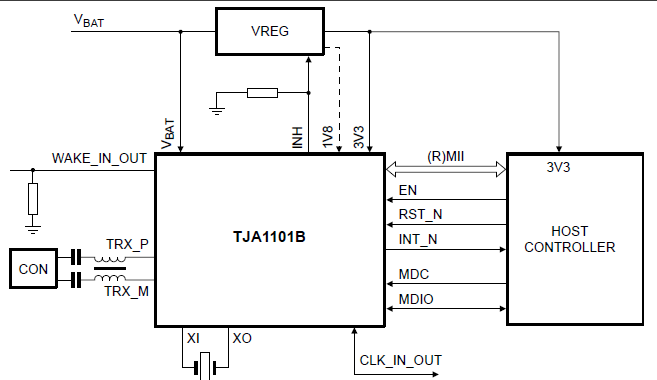

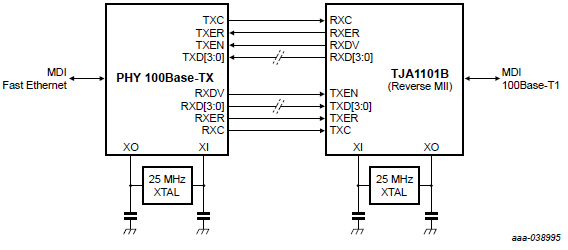

- TJA1101B的典型应用图如下所示:

下面将按照功能对相应的引脚以及设计注意事项进行说明。

2.1 电源

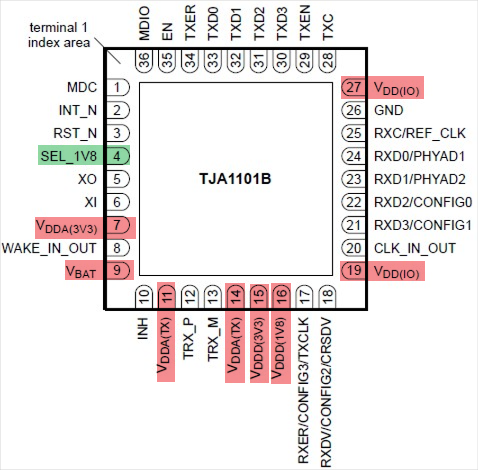

下图红色的引脚为TJA1101B的供电引脚,绿色的SEL_1V8引脚和1.8V供电有关。

有关这些引脚的说明如下表:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| SEL_1V8 | 内部1.8V LDO的模式选择 | 接下拉电阻时使能内部的1.8V LDO |

| V D D A ( 3 V 3 ) V_{DDA(3V3)} VDDA(3V3) | 3.3V模拟供电引脚 | 靠近引脚放一个对地的470nF电容 |

| V B A T V_{BAT} VBAT | 电池供电引脚 | 上电斜率小于10V/us,掉电斜率小于1V/us |

| V D D A ( T X ) V_{DDA(TX)} VDDA(TX) | 发射器的3.3V模拟供电引脚 | 两个 V D D A ( T X ) V_{DDA(TX)} VDDA(TX) 内部是连接的,PCB上也要连接 |

| V D D D ( 3 V 3 ) V_{DDD(3V3)} VDDD(3V3) | 3.3V数字供电引脚 | 靠近引脚放一个对地的100nF电容 |

| V D D D ( 1 V 8 ) V_{DDD(1V8)} VDDD(1V8) | 1.8V数字供电引脚 | 如果选择内部供1.8V,需要增加一个10nF的对地电容 |

| V D D ( I O ) V_{DD(IO)} VDD(IO) | 3.3V IO供电引脚 | 两个 V D D ( I O ) V_{DD(IO)} VDD(IO) 内部是连接的,PCB上也要连接 |

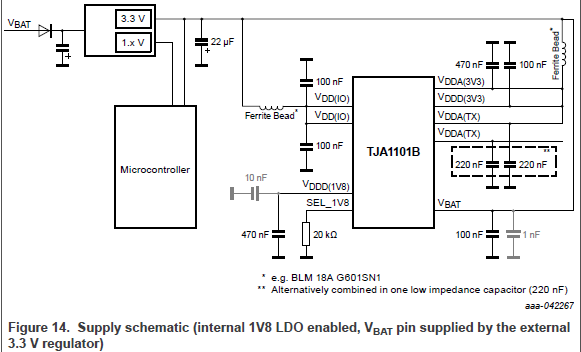

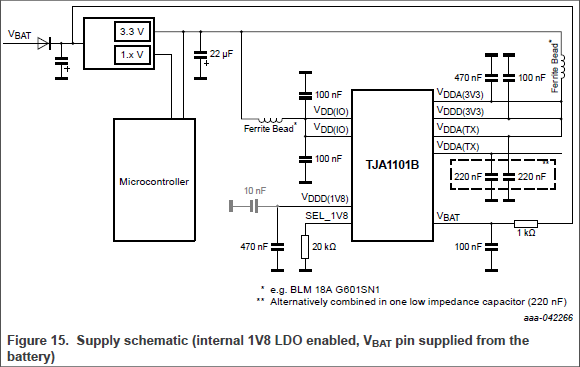

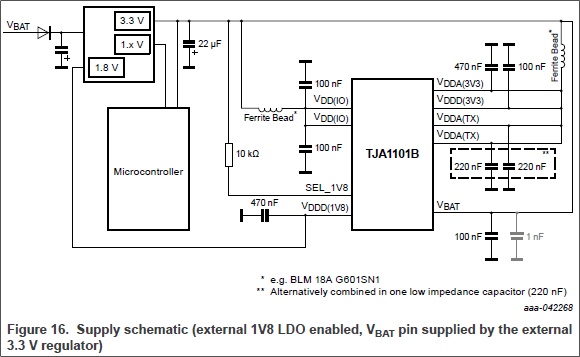

TJA110B的常见电源电路有三种:

- 1.8V电源来源于内部, V B A T V_{BAT} VBAT 引脚从外部的3.3V LDO取电,电路图如下:

- 1.8V电源来源于内部, V B A T V_{BAT} VBAT 引脚直接从电池取电,电路图如下:

- 1.8V电源来源于外部, V B A T V_{BAT} VBAT 引脚从外部的3.3V LDO取电,电路图如下:

TJA1101B对于几个电源引脚的上电顺序没有严格的要求。例如,3.3V引脚和 V B A T V_{BAT} VBAT 引脚谁先供电都可以。

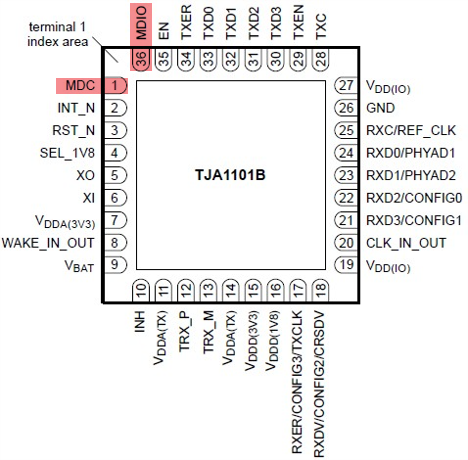

2.2 时钟

下图红色的引脚为时钟引脚:

有关这些引脚的说明如下表:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| XO | 晶体反馈引脚 | 只能用于25MHz的晶体 |

| XI | 晶体输入引脚 | 只能用于25MHZ的晶体 |

| CLK_IN_OUT | 25MHz参考时钟的输入输出引脚 | 通过register 27配置 |

| REF_CLK | RMII模式下的参考时钟输入输出 | 50MHz振荡器输入或25MHz时钟输出 |

TJA1101B支持MII模式,Reverse MII模式和RMII模式,在这两种模式下,时钟的选择有些不一样,说明如下。

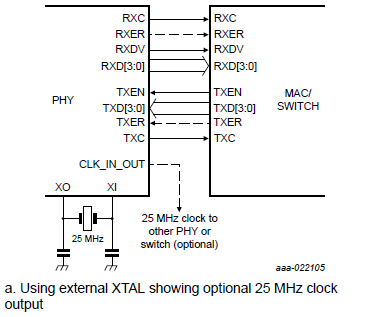

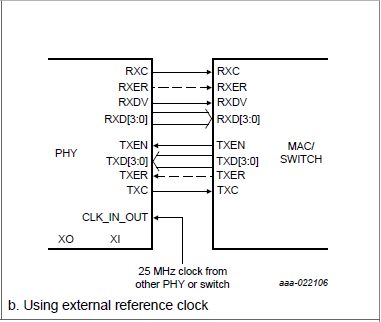

2.2.1 MII模式下的时钟选择

MII模式下,25号引脚无法用作REF_CLK功能,所以时钟相关的引脚主要是XI,XO和CLK_IN_OUT。

- 第一种方式为使用外部25MHz的晶体,即无源晶振,同时CLK_IN_OUT引脚也可向外输出25MHz的时钟(软件配置),用于其他的PHY或者switch芯片。典型电路图如下:

- 第二种方式为给CLK_IN_OUT引脚输入25MHZ的时钟信号,这个时钟信号可以从其他的PHY或者switch芯片获取。典型电路图如下:

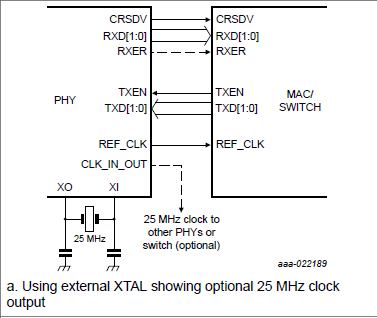

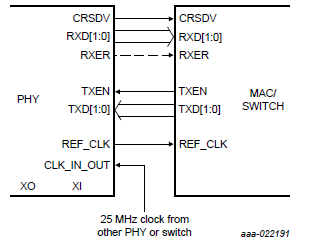

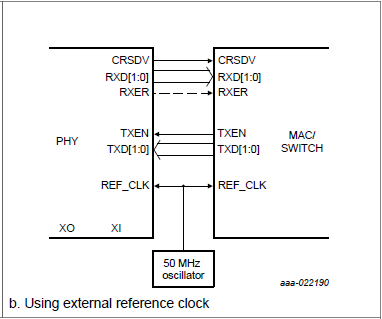

2.2.2 RMII模式下的时钟选择

RMII模式下的时钟选择有三种:

- 第一种方式使用外部的25MHz的晶体,典型电路图如下:

- 第二种方式从CLK_IN_OUT引脚输入25MHZ的时钟信号,典型电路图如下:

- 第三种方式使用50MHz的振荡器,这种方式可以让RMII达到和MII一样的数据传输速率。典型电路图如下所示:

2.2.3 Reverse MII模式下的时钟选择

Reverse MII模式一般用于传统工业网口转换为汽车的双绞线的场合下。在这种模式下,两个PHY芯片的RX和TX交叉连接,时钟选择使用如下方式。

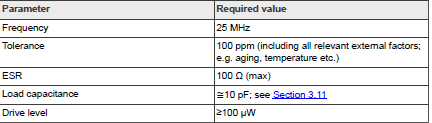

2.2.4 25MHz晶体/25MHz时钟的参数要求

- 如果使用外部25MHz的晶体,参数要求如下,其中负载电容的容值以晶体厂家的要求为准。

- 如果使用CLK_IN_OUT获取外部的25MHZ时钟信号,对其参数要求如下:

2.3 SMI接口

下图红色的引脚为SMI接口相关的引脚:

有关这些引脚的说明如下表:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| MDC | SMI接口的时钟输入引脚 | 内部集成弱下拉 |

| MDIO | SMI接口的数据传输引脚 | 内部集成弱上拉 |

MCU通过SMI接口对TJA1101B内部的寄存器进行读写操作,SMI接口的典型电路图如下:

注意事项如下:

- MDIO接口需要外接10kΩ的上拉电阻到 V D D ( I O ) V_{DD(IO)} VDD(IO),可以在MCU端或者PHY端添加,但是需要确保MDIO总线上只有一个10KΩ的上拉电阻。

- 为了更好的过EMC实验,MDC连接线建议串接一个20Ω左右的电阻

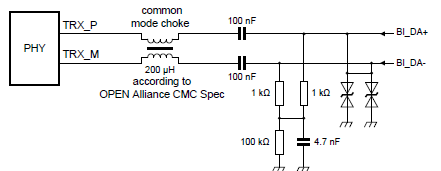

2.4 MDI接口

下图红色的引脚为MDI接口相关的引脚:

有关这些引脚的说明如下表:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| TRX_P | 差分信号线的正极 | 发送/接收数据 |

| TRX_M | 差分信号线的负极 | 发送/接收数据 |

MDI接口的典型电路图如上所示,图上相关器件的要求如下:

- 共模电感,需要符合open alliance标准的,推荐murata的DLW43MH系列

- 100nF电容:精度10%,耐压>=50V

- 1K电阻:精度1%,功率>=0.4W

- 100K电阻:精度1%,功率>=0.1W

- 4.7nF电容:精度10%,耐压>=50V

- ESD器件:需要符合open alliance标准的,推荐PESD2ETH100-T

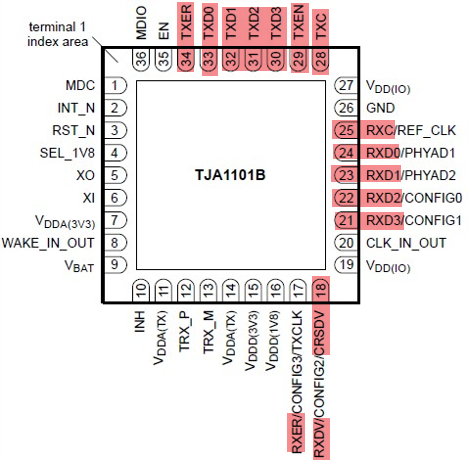

2.5 ®MII接口

下图红色的引脚为®MII接口相关的引脚:

有关这些引脚的说明如下表:

| 引脚名称 | 功能描述 |

|---|---|

| RXER | MII/RMII receive error output |

| RXDV | MII receive data valid output |

| CRSDV | RMII mode: carrier sense/receive data valid output |

| RXD3 | MII mode: receive data output, bit 3 of RXD[3:0] nibble |

| RXD2 | MII mode: receive data output, bit 2 of RXD[3:0] nibble |

| RXD1 | MII mode: receive data output, bit 1 of RXD[3:0] nibble |

| RMII mode: receive data output, bit 1 of RXD[1:0] nibble | |

| RXD0 | MII mode: receive data output, bit 0 of RXD[3:0] nibble |

| RMII mode: receive data output, bit 0 of RXD[1:0] nibble | |

| RXC | MII mode: external 25 MHz receive clock output |

| MII reverse mode: 25 MHz receive clock input | |

| TXC | MII mode: 25 MHz transmit clock output |

| MII reverse mode: external 25 MHz transmit clock input | |

| TXEN | MII/RMII mode: transmit enable input (active-HIGH; weak pull-down) |

| TXD3 | MII mode: transmit data input, bit 3 of TXD[3:0] nibble (weak pull-down) |

| TXD2 | MII mode: transmit data input, bit 2 of TXD[3:0] nibble (weak pull-down) |

| TXD1 | MII mode: transmit data input, bit 1 of TXD[3:0] nibble (weak pull-down) |

| RMII mode: transmit data input, bit 1 of TXD[1:0] nibble (weak pull-down) | |

| TXD0 | MII mode: transmit data input, bit 0 of TXD[3:0] nibble (weak pull-down) |

| RMII mode: transmit data input, bit 0 of TXD[1:0] nibble (weak pull-down) | |

| TXER | MII/RMII: transmit error input (weak pull-down) |

MII模式,Reverse MII模式和RMII模式的典型应用图在上述2.2章节已经给出,这里不在赘述。关于硬件设计的一些注意点,描述如下:

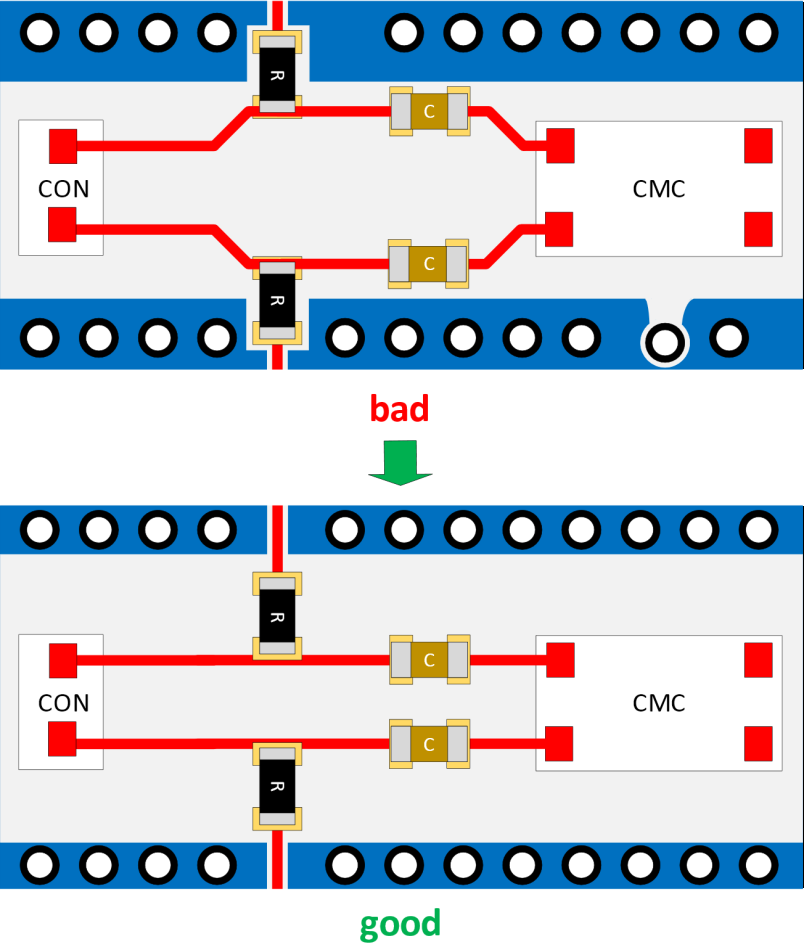

- 一般为了更好的过EMC,推荐®MII串接20Ω作用的电阻。

- MII模式相关的引脚有用不到的,输入引脚拉低,输出引脚悬空。

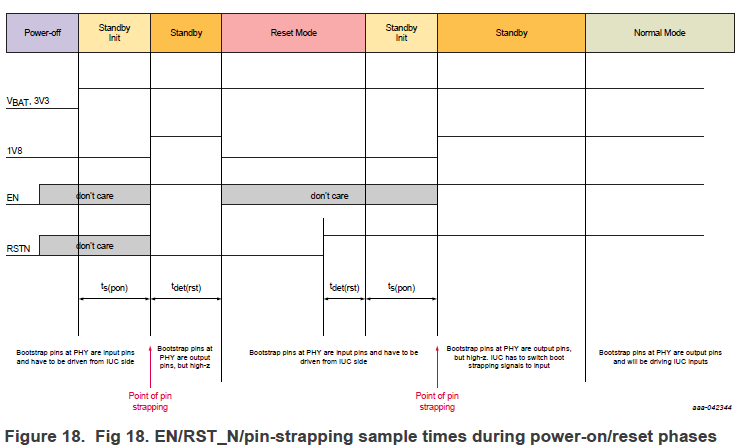

2.6 Bootstrap引脚

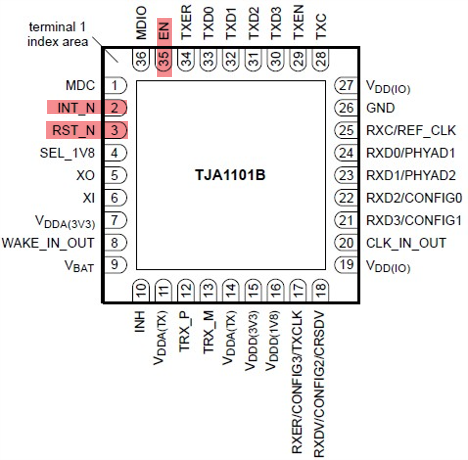

下图红色的引脚为支持pin strapping功能的自举引脚:

如下图所示,TJA1101B在上电或者复位后的一小段时间内采样这些引脚的电压,然后进行PHY的基本配置。

有关这些引脚的配置说明如下表:

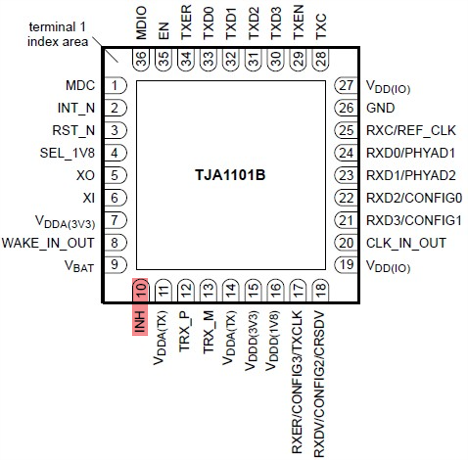

2.7 MCU控制引脚(RST_N, INT_N, EN)

下图红色的引脚为和MCU控制相关的引脚:

有关这些引脚的说明如下表:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| RST_N | 复位引脚 | 低电平有效 |

| INT_N | 中断输出引脚 | 开漏引脚,低电平有效 |

| EN | PHY使能引脚 | 高电平有效,内部集成弱下拉 |

这些引脚的典型应用图如下所示:

硬件设计的注意点如下:

- RST_N和INT_N引脚推荐加10KΩ上拉电阻到 V D D ( I O ) V_{DD(IO)} VDD(IO),EN引脚使用GPIO控制即可。

- 如果用不到TJA1101B的disable mode,将EN引脚上拉即可。INT_N引脚不用可以悬空。

- 如果在TJA1101B启动的时候EN引脚为低,TJA1101B先进入standby模式再进入disable模式。

2.8 WAKE_IN_OUT引脚

WAKE_IN_OUT引脚位置如下图红框:

有关WAKE_IN_OUT引脚的说明如下表:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| WAKE_IN_OUT | local/forwarding wake-up input/output | configurable |

WAKE_IN_OUT引脚是一个双向引脚,使用方式如下:

- 如果register18的LOCWUPHY位置1,WAKE_IN_OUT就是本地唤醒输入引脚。

- 如果register18的FWDPHYLOC位、REMWUPHY置1,WAKE_IN_OUT会将唤醒信号转发。

2.9 INH引脚

INH引脚位置如下图红框:

有关INH引脚的说明如下表:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| INH | inhibit output for voltage regulator control | VBAT-related, active-HIGH |

TJA1101B的INH引脚的用法和CAN\LIN收发器的基本一致,同时增加了INH引脚在disable模式下是否ON可配置的功能。为了防止LDO的EN引脚没有下拉导致INH悬空时无法关闭LDO的情况,推荐在INH引脚接一下5KΩ到20KΩ的下拉电阻。

3.Layout注意事项

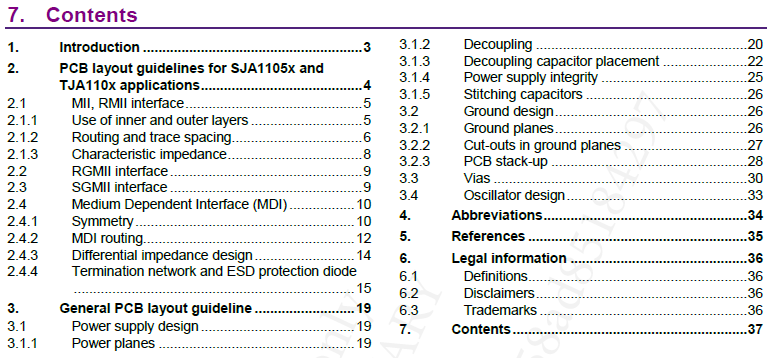

针对车载以太网,NXP有一份关于PCB设计的详细指导文档,名称为《AH544111_3-AH1806 PCB Design Guide(1.1).pdf》,目前还处于保密资料,需要和NDA协议才能拿到。

整个的文档的目录如下:

针对每部分的电路,都有详细的layout注意事项,下面是截取的文档中部分无水印的内容。

如果有使用到TJA1101B或者其他NXP的其他车载以太网产品的,建议按照这份文档的指导进行PCB设计。

4.推荐文档

-

TJA1101B, 100BASE-T1 PHY for automotive Ethernet – Data Sheet (nxp.com)

-

AN13236 - TJA1101B Automotive Ethernet PHY, Application Note (nxp.com)

-

OPEN Alliance Automotive Ethernet Specifications (opensig.org)

如果觉得本文对你有用,不妨给个一键三连!!!

本文详细介绍了TJA1101B汽车以太网PHY的硬件设计,包括电源配置、时钟选择(MII,RMII,ReverseMII模式)、SMI和MDI接口、MII接口以及MCU控制引脚等关键设计要点,同时提到了布局注意事项和相关推荐文档。

本文详细介绍了TJA1101B汽车以太网PHY的硬件设计,包括电源配置、时钟选择(MII,RMII,ReverseMII模式)、SMI和MDI接口、MII接口以及MCU控制引脚等关键设计要点,同时提到了布局注意事项和相关推荐文档。

5172

5172

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?