根据逻辑电路的不同特点,数字电路可以分为:组合逻辑和时序逻辑

-

组合逻辑

组合逻辑的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原本的状态无关,逻辑中不牵涉跳变沿信号的处理,组合逻辑的verilog描述方式有两种:

(1)always @(电平敏感信号列表)或者always @ *

always模块的敏感列表为所有判断条件信号和输入信号,但一定要注意敏感列表的完整性。在always 模块中可以使用if、case 和for 等各种RTL 关键字结构。由于赋值语句有阻塞赋值和非阻塞赋值两类,建议读者使用阻塞赋值语句“=”。always 模块中的信号必须定义为reg 型,不过最终的实现结果中并没有寄存器。这是由于在组合逻辑电路描述中,将信号定义为reg型,只是为了满足语法要求;

(2)assign描述的赋值语句

信号只能被定义为wire型;

-

时序逻辑

时序逻辑是Verilog HDL 设计中另一类重要应用,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。电路里面有存储元件(各类触发器,在FPGA 芯片结构中只有D 触发器)用于记忆信息,从电路行为上讲,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化;

与组合逻辑不同的是:

(1)在描述时序电路的always块中的reg型信号都会被综合成寄存器,这是和组合逻辑电路所不同的。

(2)时序逻辑中推荐使用非阻塞赋值“<=”。

(3)时序逻辑的敏感信号列表只需要加入所用的时钟触发沿即可,其余所有的输入和条件判断信号都不用加入,这是因为时序逻辑是通过时钟信号的跳变沿来控制的

-

组合逻辑常见的错误

(1)变量在多个always 块中赋值

reg y;

reg a,b,c,clear;

...

always @*

if(clear) y = 1'b0;

always @*

y = a&b; 尽管该代码作为异步电路是正确的,也可以进行仿真,但是无法综合,必须将y的赋值写在同一个always 块中;

(2)不完整的敏感信号列表

对于组合逻辑电路,输出是输入的函数,因此任何信号的变化都会激活电路,这要求所有的输入信号都应该包含在敏感信号列表中,例如:

always @(a or b)//a和b都在敏感列表中

y = a & b;

如果忘记包含b,则代码变成:

always @(a)

y = a & b; 尽管代码依然可以正确综合,但是行为改变了,当a发生变化时,always 块被激活,a&b的值赋给y;当b发生变化时,由于对b不敏感,依然处于中止状态,y保持之前的值不变!一般为了避免出现这一情况,推荐使用always @* ,表示包含所有相关的输入信号;

(3)不完整分支和不完整输出赋值

组合电路的输出是输入的函数,不应该包含任何内部状态(即存储器),always块中一种常见的错误就是综合出意外存储器;为了防止出现意外存储器,所有的输出信号在任何时候都应该赋予恰当值;不完整分支和不完整输出赋值是两种常见的导致意外存储器产生的错误,例如,当表达式a>b为真时,若eq没有被赋值,则会保持之前的值,从而会综合出相应的存储器。

有两种方法来解决上述问题,第一种是加上else分支并明确给出所有输出变量赋值,代码变成:

always @*

if(a > b)

begin

gt = 1'b1;

eq = 1'b0;

end

else if(a == b)

begin

gt = 1'b0;

eq = 1'b1;

end

else

begin

gt = 1'b0;

eq = 1'b0;

end另一种方法是在always块的起始部分,给每个变量赋默认值,以包含所有未指定的分支和为赋值的变量,代码变成:

always @*

begin

gt = 1'b0;

eq = 1'b0;

if(a > b)

gt = 1'b1;

else if (a == b)

eq = 1'b1;

end阻塞赋值与非阻塞赋值

1.阻塞赋值(=):阻塞赋值操作实质上是一次性连续完成的,即计算等号右边变量(或表达式)的值(RHS)并立即赋值给等号左边的变量(LHS)。其中阻塞的含义为在同一个always块中,当前赋值语句正在执行时禁止其后的所有其他赋值语句的执行。只有当前赋值语句执行完成后,其后的赋值语句才能被执行;

对于阻塞赋值,左值的变化是立刻进行的,也就是在always 的敏感事件执行完的同时,左值立刻变化;

2.非阻塞赋值(=):非阻塞赋值操作实质上是分两步完成的,即第一步:在敏感事件开始时刻(如clk正跳变沿开始时刻)开始计算等号右边变量(或表达式)的值RHS;第二步:在敏感事件结束时刻(如clk正跳变沿结束时刻)将等号右边的值赋给等号左边的变量LHS。其中非阻塞的含义为在执行当前的非阻塞赋值语句的同时允许其他的语句执行;

简而言之,在敏感时间执行的同时计算右值,然后在敏感事件结束之后再将右值赋值给左值,左值的变化在敏感事件执行完之后;与此同时,非阻塞赋值不会影响该赋值语句后面的语句的执行!

3.阻塞赋值与非阻塞赋值不要混用!!

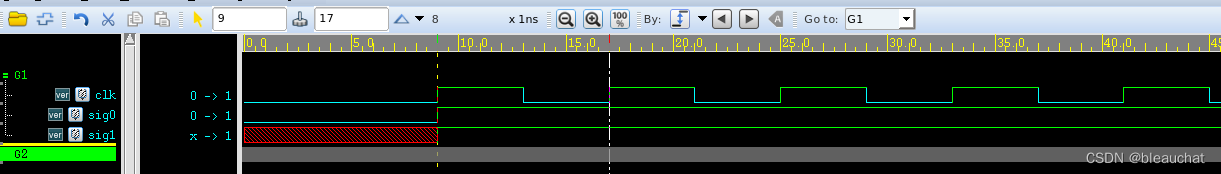

reg sig0, sig1;

always @(posedge clk) begin

sig0 = 1;

end

always @(posedge clk) begin

sig1 <= sig0;

end波形如下:

上面由于阻塞与非阻塞操作的混用,在9ns 的位置将 1 赋值给 sig0,由于是阻塞赋值所以 sig0 立刻变为1;于此同时由于 sig1 的赋值为非阻塞,但是由于此时采样到 sig0 为1,所以sig1 被非阻塞赋值为1,并且在9ns 之后生效;

7971

7971

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?