在很多时候都要对输入脉冲进行边沿检测,如PS/2时序,ps2_data数据在ps2_clk时钟下降沿接收。

边沿检测Verilog程序代码:

布线布局后仿真波形如下图:

可以注意到其中的移位寄存器用了非阻塞赋值(<=)

ps2_clk_r0<=ps2_clk;

ps2_clk_r1<=ps2_clk_r0;

ps2_clk_r2<=ps2_clk_r1;

如果用阻塞赋值的话,综合的时候会把其中两个寄存器去点,用阻塞赋值(=)

ps2_clk_r0=ps2_clk;

ps2_clk_r1=ps2_clk_r0;

ps2_clk_r2=ps2_clk_r1;

会出来这样的警告:

WARNING:Xst:646 - Signal <ps2_clk_r0> is assigned but never used.

Register <ps2_clk_r2> equivalent to <ps2_clk_r1> has been removed

Found 1-bit register for signal <ps2_clk_r1>.

WARNING:Xst:2677 - Node <ps2_clk_r1> of sequential type is unconnected in block <DetecEdge>.

从RTL可以看到,只剩ps2_clk_r1一个D触发器。

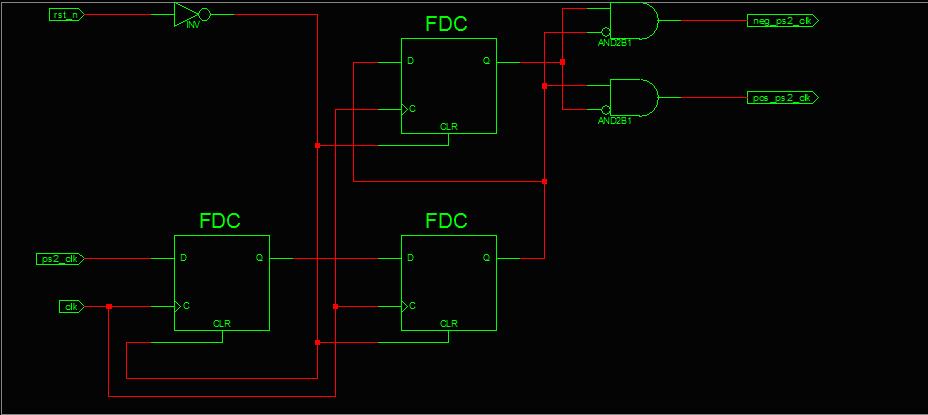

上图是非阻塞赋值综合后的RTL,可以看出,有三个D触发器做移位寄存器。通过移位,对边沿进行检测。

程序工程文件下载:http://space.ednchina.com/upload/2009/3/24/86bb5e63-8959-47c4-af52-10ac330554d3.rar

代码还有一种写法:

布线布局后仿真波形和之前程序的仿真波形一样

程序文件下载:http://space.ednchina.com/upload/2009/3/24/5286d476-c43c-4b99-b658-5d53865ce19a.rar

参考资料:

1)verilog的PS2键盘解码——特权’s blog

http://blog.ednchina.com/ilove314/153929/message.aspx

2) [FPGA][Verilog][PS2]模拟PS2协议,丢掉4x4键盘,来用标准键盘吧!_阿虚的电子小屋

http://hi.baidu.com/aokikyon/blog/item/e46dc2368d9f76350a55a99a.html

---------------------------------------------------------------------------------------------------

在键盘消抖实验中用到的方法,但是在网上没搜到,具体就是建立2个寄存器,形成二级寄存器,在时钟触发中,首先把数据送入第一个寄存器中,然后在下一个时钟上沿到来时,将第一个寄存器中的数据存入第二个寄存器,也就是说第二个寄存器中的数据始终比第一个寄存器晚一个周期,即晚一个数据,然后再将第一个寄存器中的数据取反与第二个寄存器的数据相与,产生的数存入一个新的寄存器里,这样产生的结果是当第一个寄存器中的数据由1变为0时,就会在新的寄存器里产生一个高电平,并维持一个周期

例子:

reg[2:0] key_rst;

always @(posedge clk or negedge rst_n)

if (!rst_n) key_rst <= 3'b111;

else key_rst <= {sw3_n,sw2_n,sw1_n};

reg[2:0] key_rst_r; //每个时钟周期的上升沿将low_sw信号锁存到low_sw_r中

always @ ( posedge clk or negedge rst_n )

if (!rst_n) key_rst_r <= 3'b111;

else key_rst_r <= key_rst;

//当寄存器key_rst由1变为0时,led_an的值变为高,维持一个时钟周期

wire[2:0] key_an = key_rst_r & ( ~key_rst);

279

279

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?