项目需求

硬件设计时没有使用CPU的TripZone功能实现过压保护/过流保护。希望通过DSP的配置来实现。

设计思路

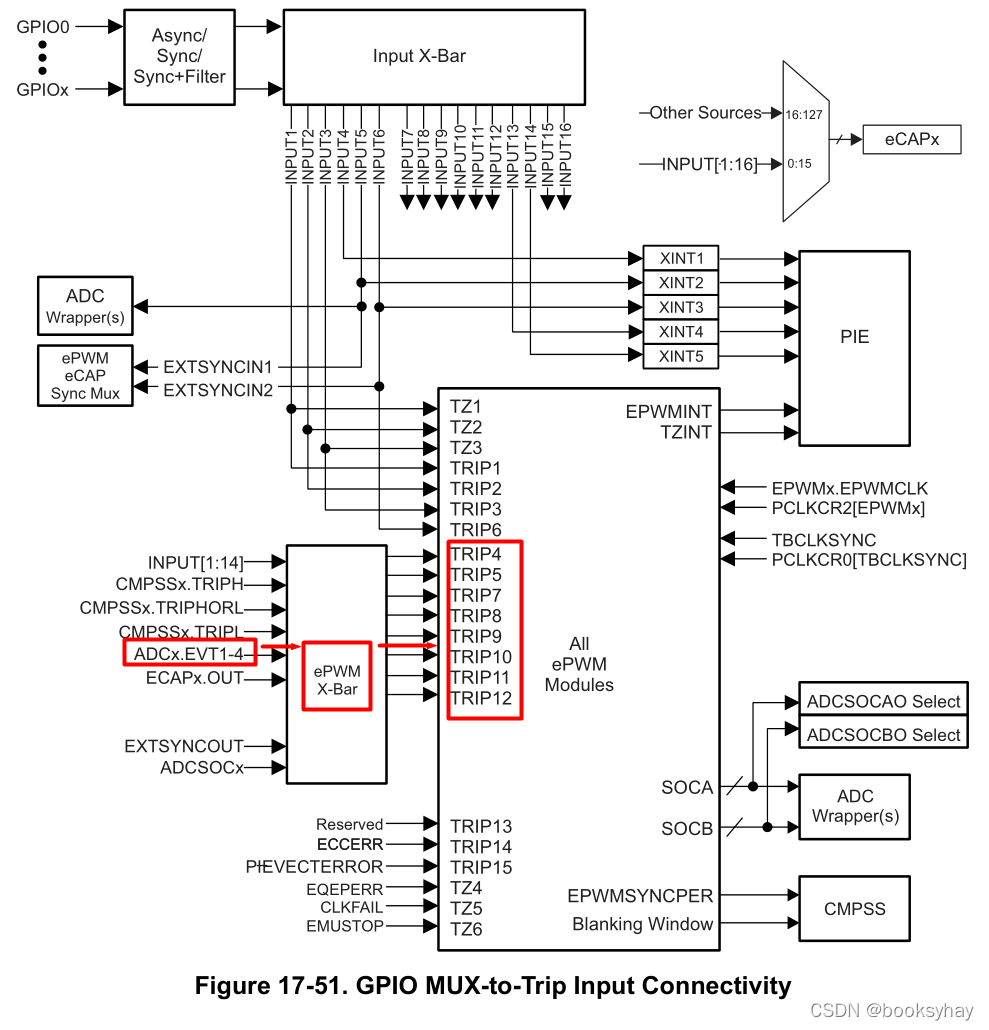

就是将ADCx.EVTy通过ePWM X-Bar送到ePWMx的TripZone。

具体配置

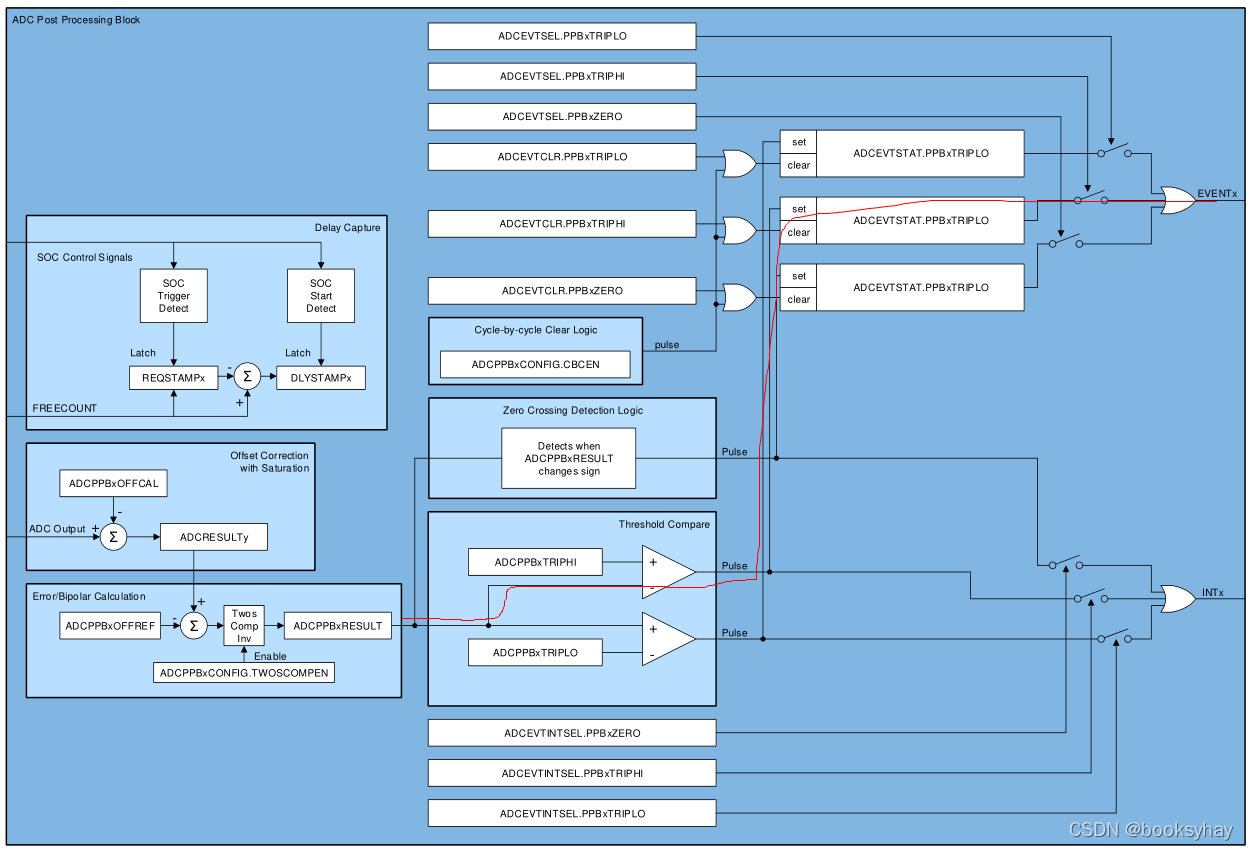

ADC的后处理模块(PPB)

本款DSP有2路ADC,每路ADC有4个Post-Processing Block。每个PPB模块可以输出一路事件和一路中断信号。这里就利用ADC后处理模块的“超过上限”事件来实现。

需要配置的有:

- PPB模块使能;

- ADCPPBxTRIPHI的值。即:当ADC的码值超过多少时,触发Trip

- ADCEVTSEL事件选择PPBxTRIPHI

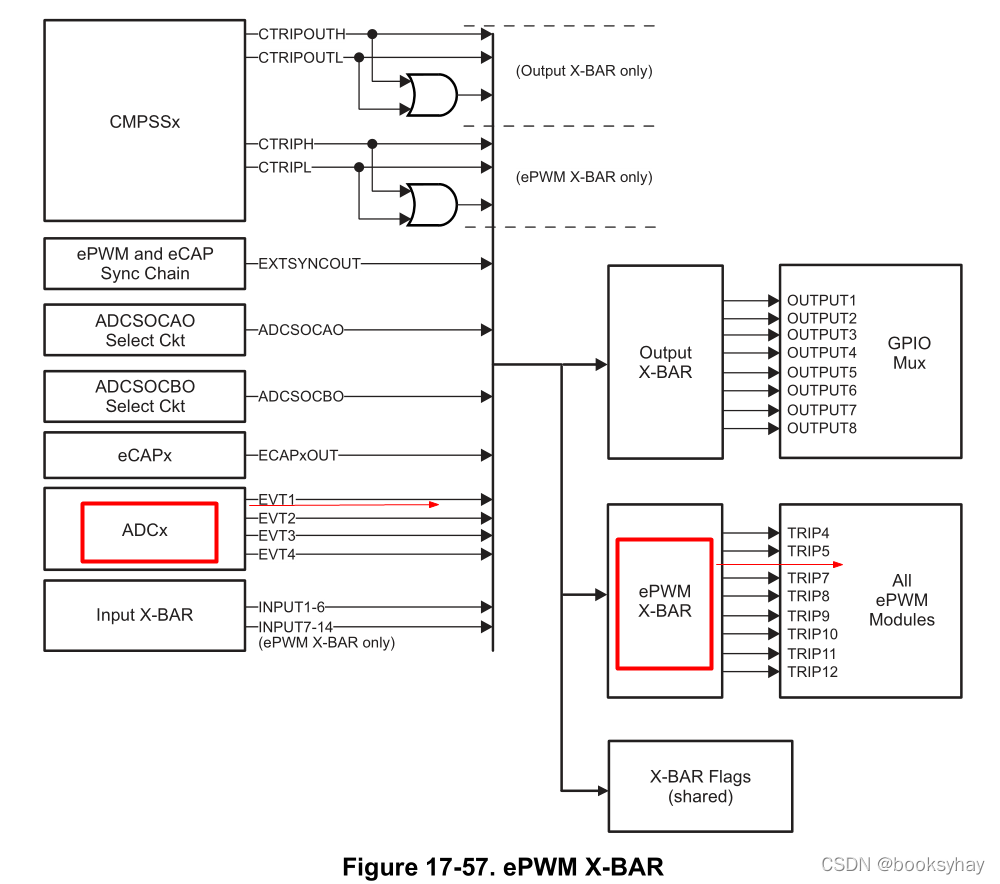

ePWM CrossBar

在ePWM的xBar中把ADC的事件选进来。

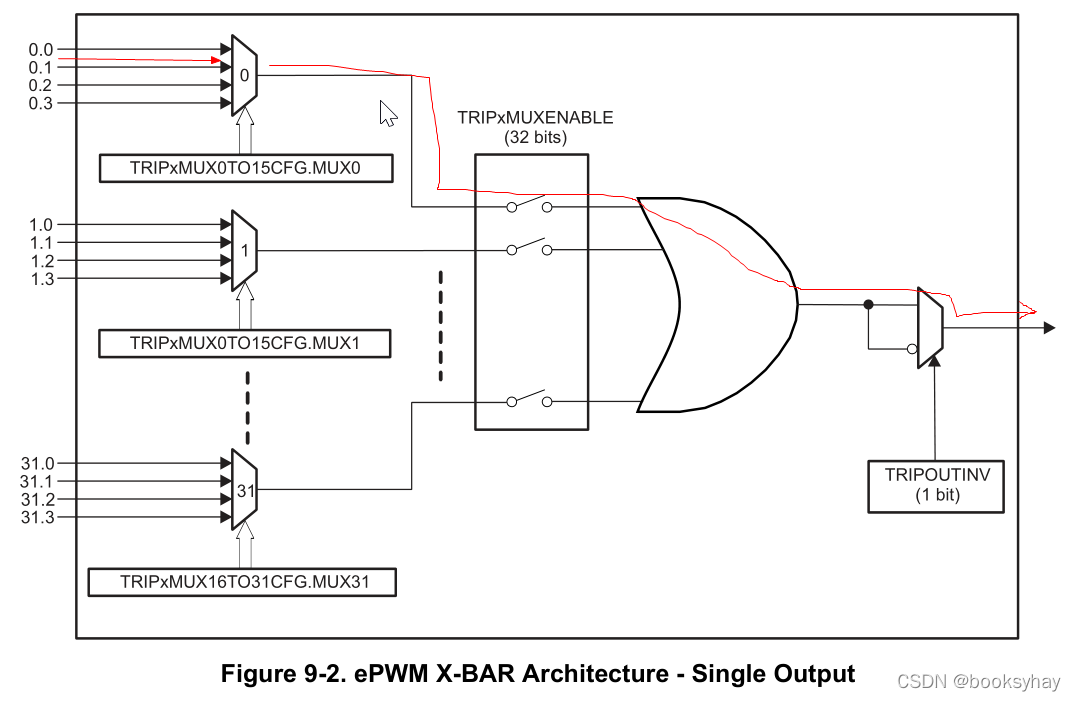

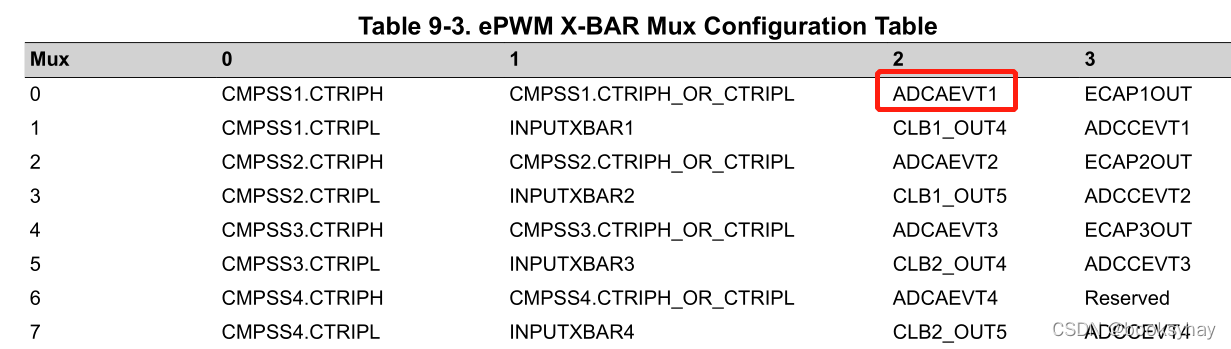

具体的选入方式为:

其中的输入信号有很多个,这里选择Mux0.2,即ADCAEVT1

说明:ePWM的X-BAR有8组,即TRIP4~TRIP12(没有TRIP6)。最多可以给EPWM模块输送8个信号。这个EPWM X-BAR是属于芯片组的,不属于具体某一路EPWM模块。

这里可以选择其中的任意一个来用(比如TRIP4)。

需要配置的项目有:

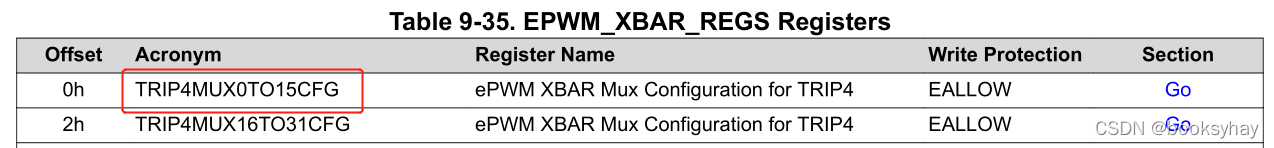

- TRIPxMUX0TO15CFG.MUX0选择信号

- TRIPxMUXENABLE使能信号

![]()

经过上述配置,已经把ADC的信号送到EPWM的TRIP4了。下一步就到了EPWM的数字比较子模块(Digital Compare Subsystem)。

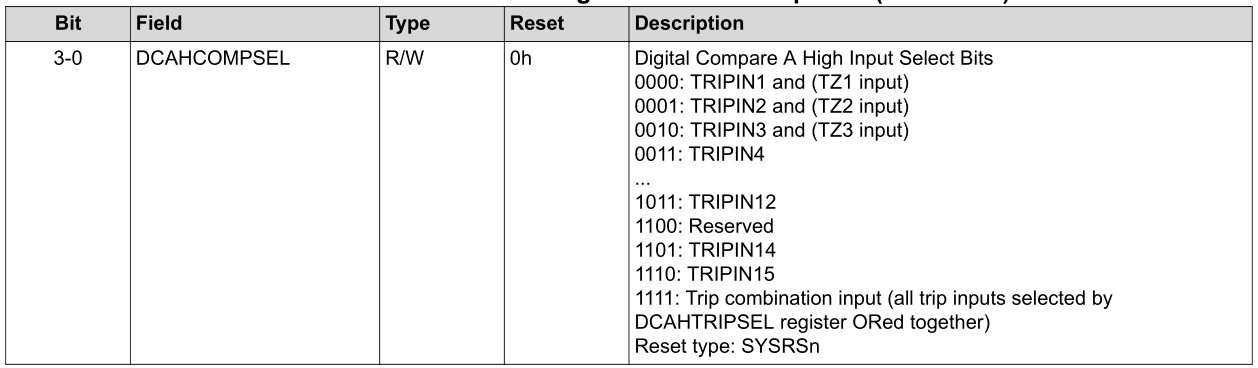

数字比较子模块(Digital Compare Subsystem)

选择了TRIP4之后,配置DC子模块的事件,就可以触发TripZone了。

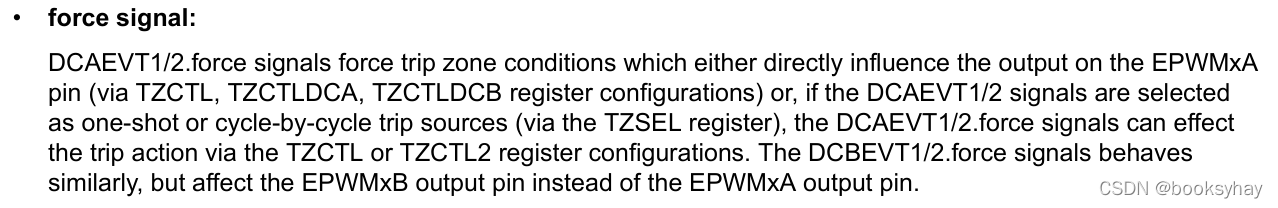

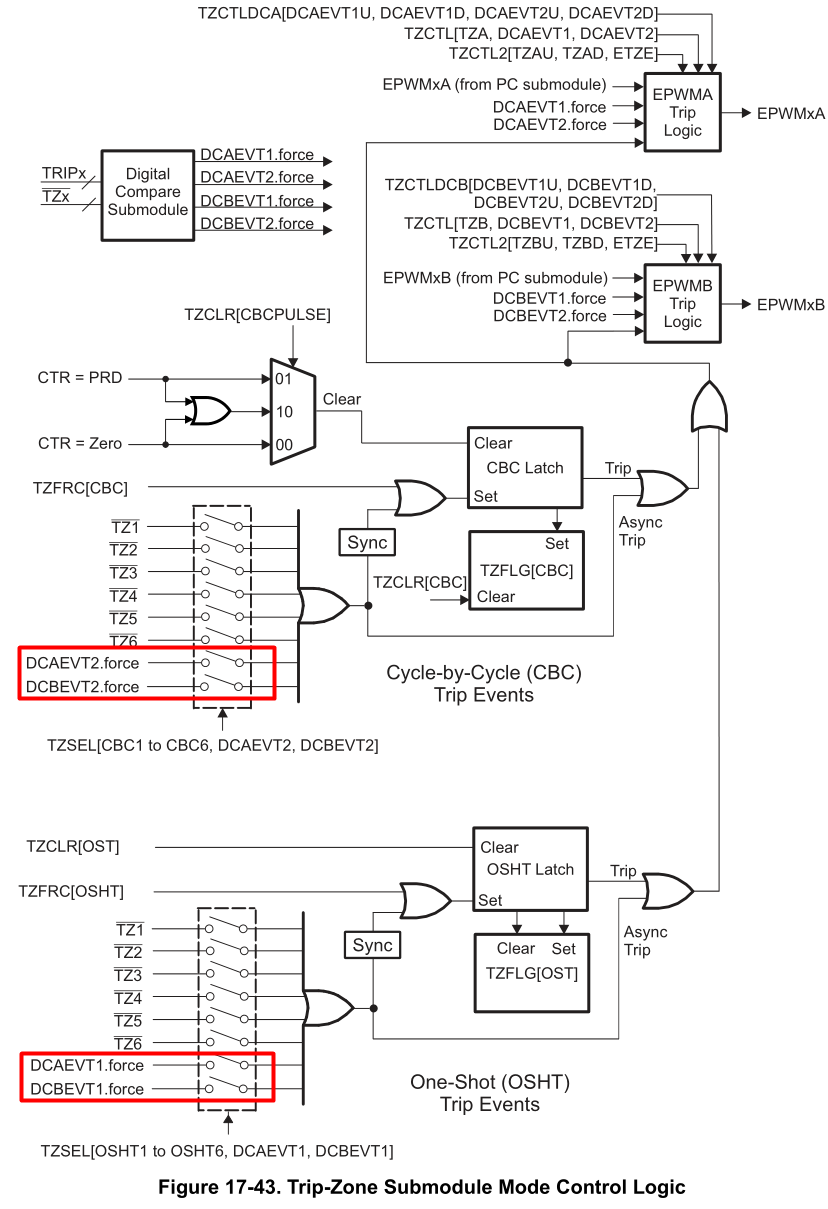

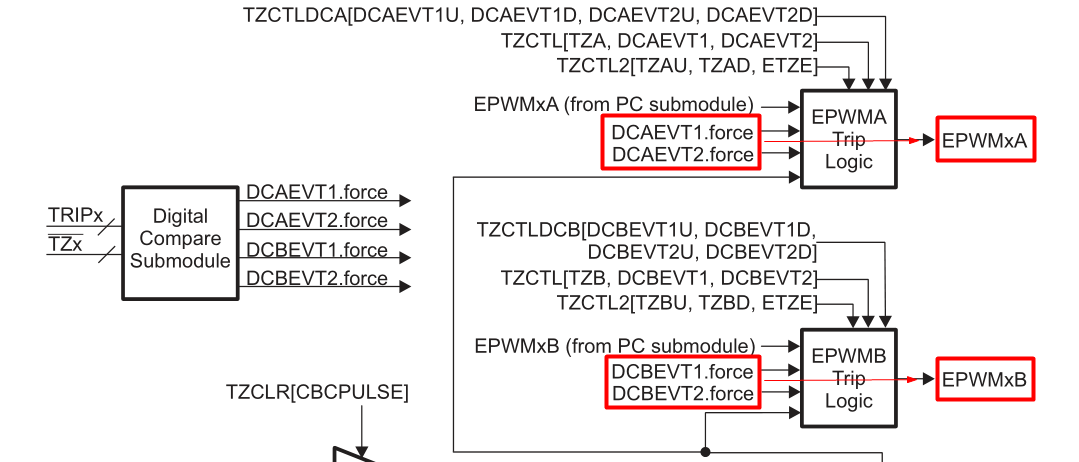

DCAEVT1/2.force 信号强制触发区域条件,这些条件要么直接影响 EPWMxA 引脚上的输出(通过 TZCTL、TZCTLDCA、TZCTLDCB 寄存器配置),要么如果 DCAEVT1/2 信号被选择为一次性或逐周期 跳闸源(通过 TZSEL 寄存器),DCAEVT1/2.force 信号可以通过 TZCTL 或 TZCTL2 寄存器配置影响跳闸动作。 DCBEVT1/2.force 信号的行为类似,但影响的是 EPWMxB 输出引脚,而不是 EPWMxA 输出引脚。

说明:

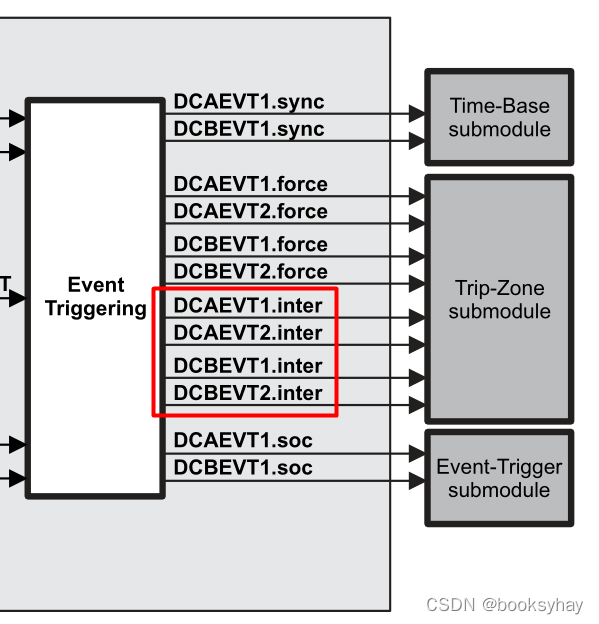

DC子模块输出的inter信号不是“内部信号”,而是“中断信号”(interrupt signal)。

选择触发源

首先,

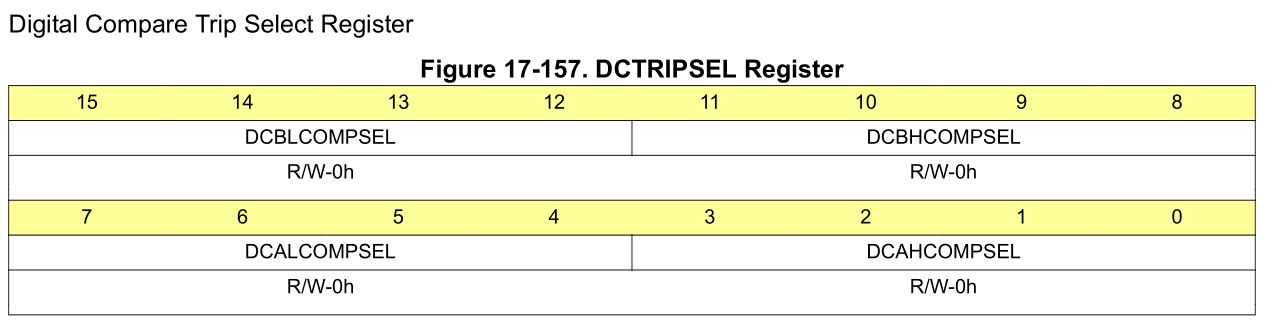

DCTRIPSEL可以从一堆TRIP中选择出4个信号:DCAH,DCAL,DCBH,DCBL。

注意:这里的“H”和“L”并不是指高低电平,只是用于区别信号的名称。实际上,DCAH也可以关联低电平(逻辑0),DCAL也可以关联高电平(逻辑1),以产生相应的事件。

选择方法为配置DCTRIPSEL寄存器。

比如,DCAH的选择配置为:

配置DC事件

然后,

可以配置出4个事件:DCAEVT1、DCAEVT2、DCBEVT1、DCBEVT2(简称为A1,A2,B1,B2事件)

比如事件A限定器Event A Qual,可以选择DCAH或DCAL信号中的任意电平作为A1事件的触发源。

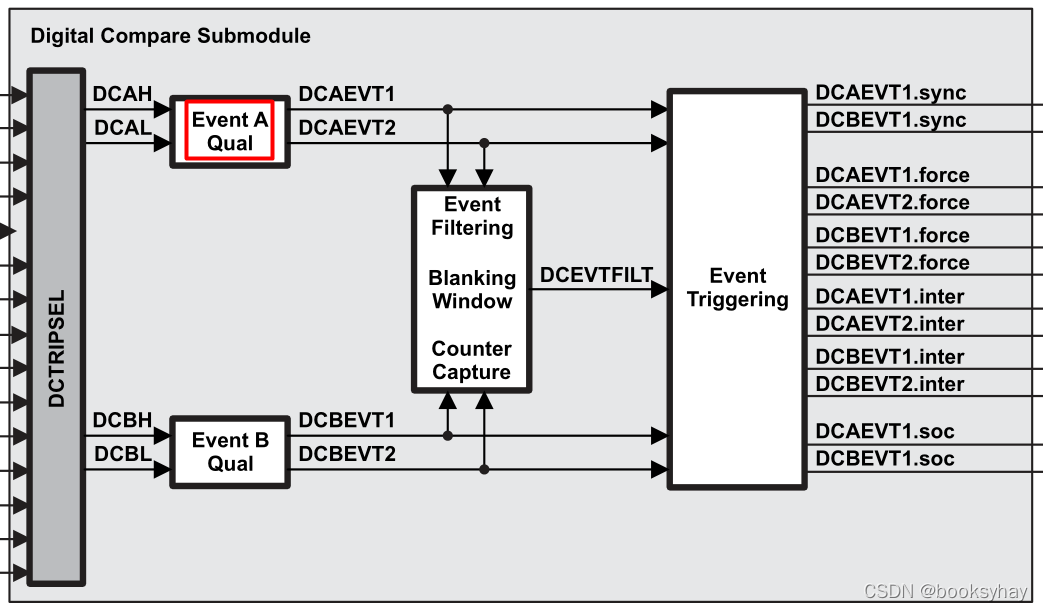

相关寄存器是TZDCSEL:共4个字节,分别对应4个事件的配置。每个字段有3个位。

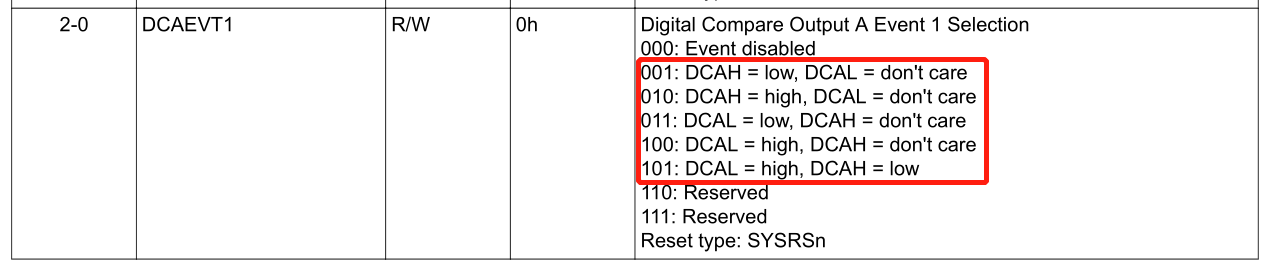

比如,DCAEVT1的配置为:

可以由以下几种情况产生A1事件:

- DCAH为低

- DCAH为高

- DCAL为低

- DCAH为高

- DCAL为高,并且DCAH为低

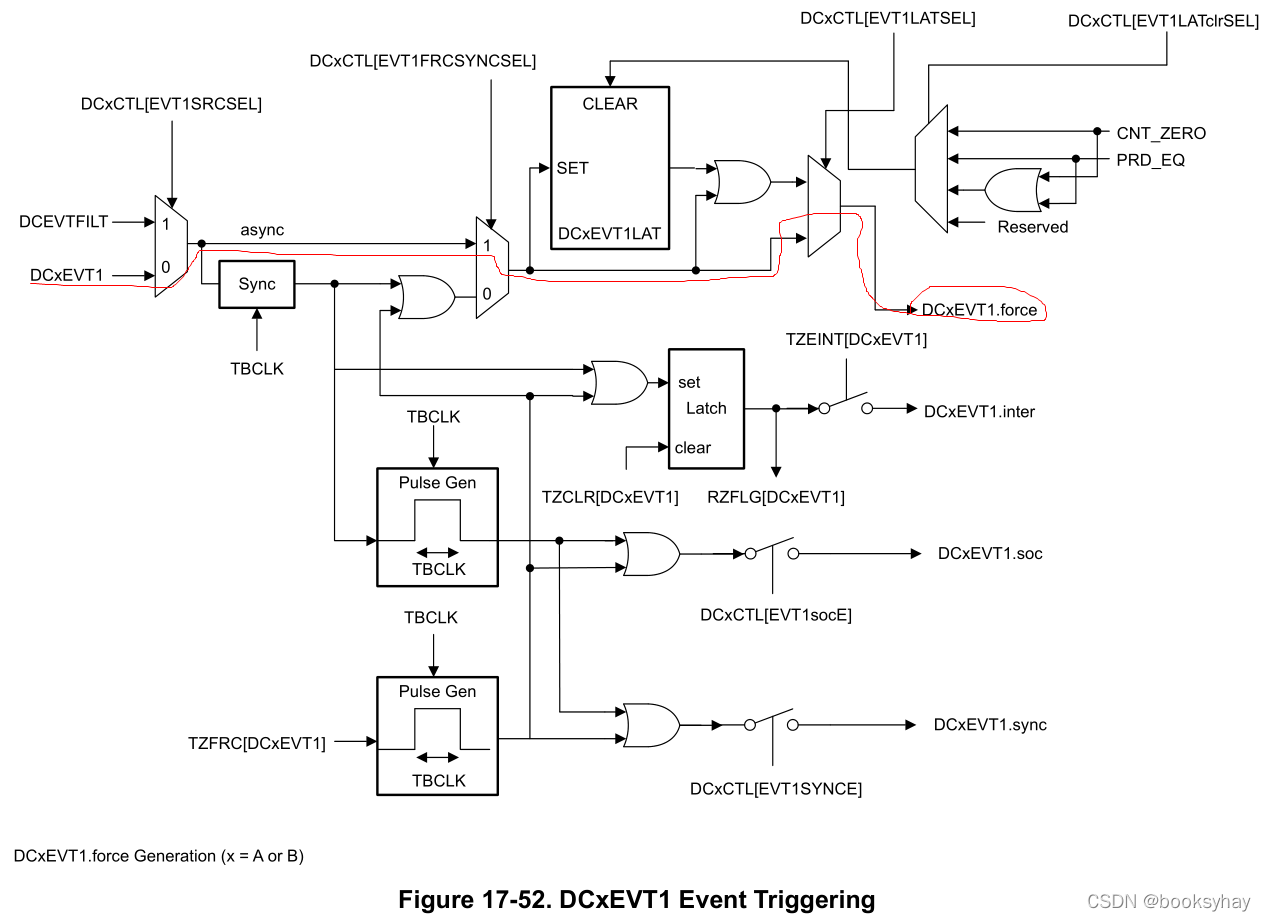

产生强制信号

从事件A1到强制信号:

事件1和事件2的区别是,事件2没有SOC和sync输出。

TripZone子模块

最后,就轮到TZ模块的配置了。配置方法与GPIO产生的TZ1/TZ2/TZ3类似。

原理框图如下:

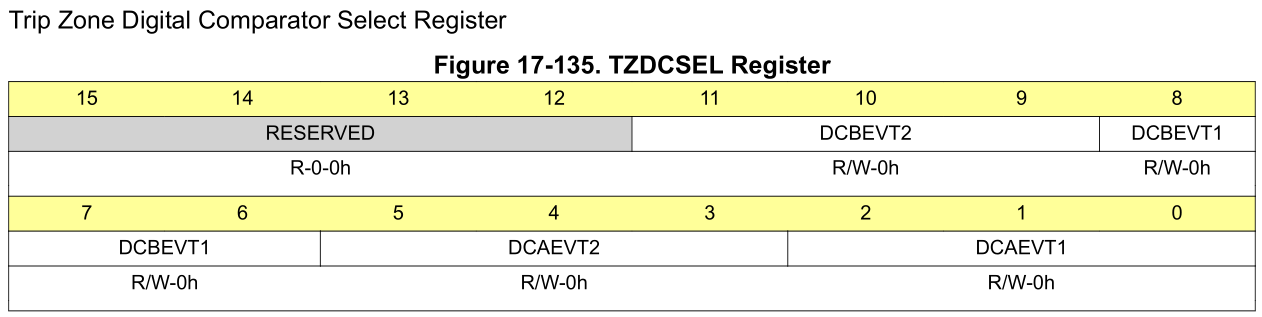

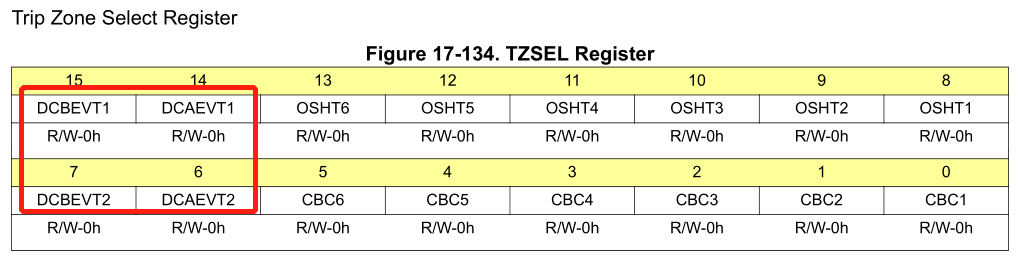

使能Trip信号

通过配置TZSEL寄存器中的DCAEVT1、DCAEVT2、DCBEVT1、DCBEVT2位来使能Trip信号。

配置TZ动作

DCAEVT1/2.force 信号强制错误联防模块条件直接影响 ePWMxA 引脚的输出(通过配置 TZCTL[DCAEVT1 or DCAEVT2]),或者当 DCAEVT1/2 信号经配置 TZSEL 寄存器被选为单次触发(one-shot)或周期性触发(CBC)源时,DCAEVT1/2.force 信号可通过配置 TZCTL[TZA] 来影响触发动作。DCBEVT1/2.force 信号相似,但是影响的是 ePWMxB 的输出。

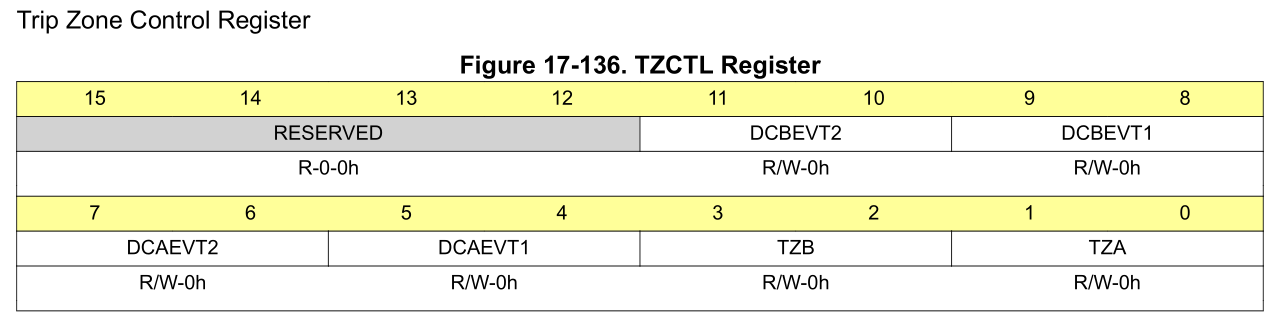

相关寄存器为TZCTL:

其中,TZA和TZB配置TZ影响的PWM-A和PWM-B的输出。其余4个为DC事件影响的PWM输出(注意:事件A1和A2只能影响PWM-A的输出,事件B1和B2只影响PWM-B的输出)。

关于数字比较事件的说明:

Digital Compare Events (DCAEVT1/2 and DCBEVT1/2):

A digital compare DCAEVT1/2 or DCBEVT1/2 event is generated based on a combination of the DCAH/DCAL and DCBH/DCBL signals as selected by the TZDCSEL register. The signals which source the DCAH/DCAL and DCBH/DCBL signals are selected via the DCTRIPSEL register and can be either trip zone input pins or analog comparator CMPSSx signals. For more information on the digital compare submodule signals, see Section 17.11.

When a digital compare event occurs, the action specified in the TZCTL[DCAEVT1/2] and TZCTL[DCBEVT1/2] bits is carried out immediately on the EPWMxA and/or EPWMxB output. Table 17-13 lists the possible actions. Independent actions can be specified based on the occurrence of the event while the counter is counting up and/or while it is counting down by appropriately configuring bits in TZCTLDCA and TZCTLDCB register. Actions specified in TZCTLDCA and TZCTLDCB registers take effect only when ETZE bit in TZCTL2 is set.

In addition, the relevant DC trip event flag (TZFLG[DCAEVT1/2] / TZFLG[DCBEVT1/2]) is set and a EPWMx_TZINT interrupt is generated if it is enabled in the TZEINT register and PIE peripheral.

The specified condition on the pins is automatically cleared when the DC trip event is no longer present. The TZFLG[DCAEVT1/2] or TZFLG[DCBEVT1/2] flag bit will remain set until it is manually cleared by writing to the TZCLR[DCAEVT1/2] or TZCLR[DCBEVT1/2] bit. If the DC trip event is still present when the TZFLG[DCAEVT1/2] or TZFLG[DCBEVT1/2] flag is cleared, then it will again be immediately set.

谷歌翻译如下:

数字比较事件(DCAEVT1/2 和 DCBEVT1/2):

根据 TZDCSEL 寄存器选择的 DCAH/DCAL 和 DCBH/DCBL 信号的组合生成数字比较 DCAEVT1/2 或 DCBEVT1/2 事件。提供 DCAH/DCAL 和 DCBH/DCBL 信号的信号通过 DCTRIPSEL 寄存器选择,可以是触发区输入引脚或模拟比较器 CMPSSx 信号。有关数字比较子模块信号的更多信息,请参见第 17.11 节。

当发生数字比较事件时,在 TZCTL[DCAEVT1/2] 和 TZCTL[DCBEVT1/2] 位中指定的操作会立即在 EPWMxA 和/或 EPWMxB 输出上执行。表 17-13 列出了可能的操作。通过适当配置 TZCTLDCA 和 TZCTLDCB 寄存器中的位,可以根据计数器向上计数和/或向下计数时事件的发生来指定独立操作。 TZCTLDCA 和 TZCTLDCB 寄存器中指定的动作只有在 TZCTL2 中的 ETZE 位置位时才会生效。

此外,如果在 TZEINT 寄存器和 PIE 外设中使能相关 DC 跳闸事件标志 (TZFLG[DCAEVT1/2] / TZFLG[DCBEVT1/2]) 并生成 EPWMx_TZINT 中断。

当直流跳闸事件不再存在时,引脚上的指定条件会自动清除。 TZFLG[DCAEVT1/2] 或 TZFLG[DCBEVT1/2] 标志位将保持设置状态,直到通过写入 TZCLR[DCAEVT1/2] 或 TZCLR[DCBEVT1/2] 位手动清除。如果在 TZFLG[DCAEVT1/2] 或 TZFLG[DCBEVT1/2] 标志清零时直流跳闸事件仍然存在,那么它将再次被立即设置。

2127

2127

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?