TMS320F280025 EPWM:时基(TB)子模块

文章目录

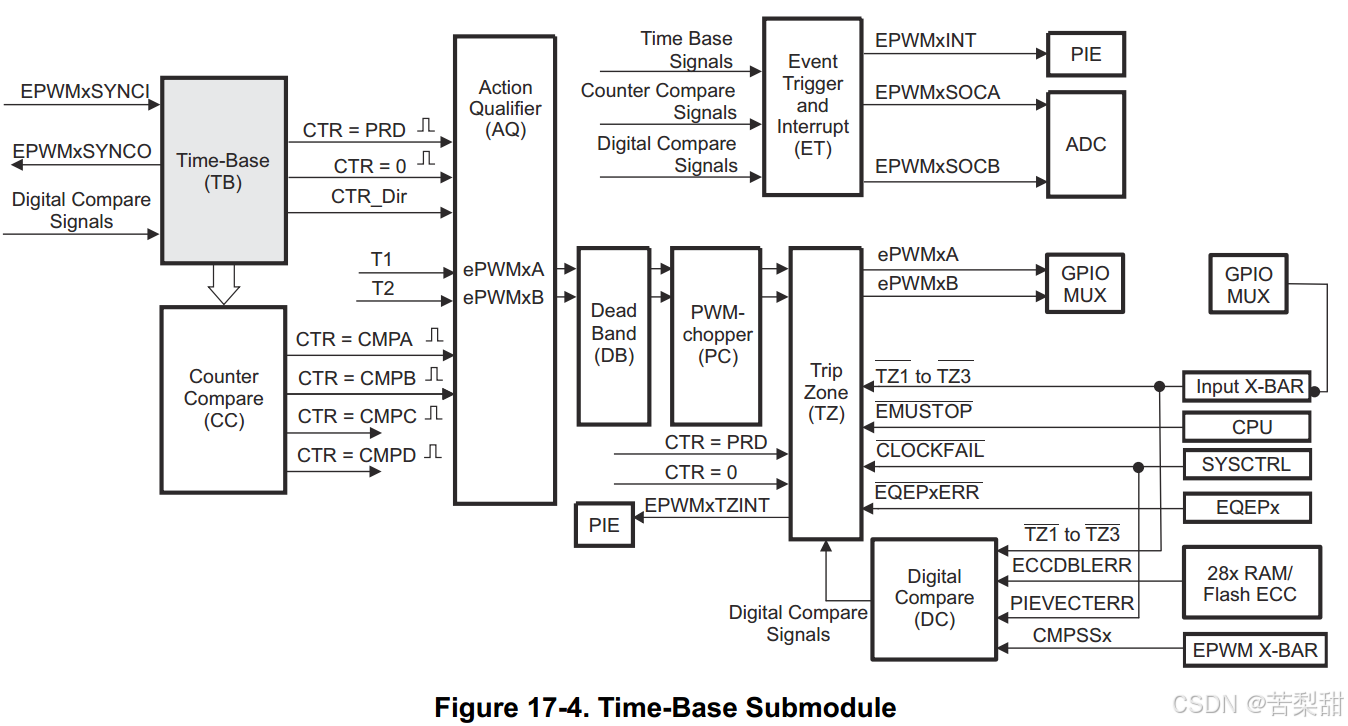

每个ePWM模块都有一个时基子模块,用于确定ePWM模块的所有事件定时。

内置同步逻辑允许多个ePWM模块的时间基础作为单个系统一起工作。

Time-Base子模块的目的

time-base子模块的配置功能如下:

•配置ePWM的TBCTR (time-base counter)频率或周期,控制事件发生的频率。

•管理与其他ePWM模块的时基同步。

•维护与其他ePWM模块的相位关系。

•设置时基计数器为倒数、倒数或倒数模式。

•生成以下事件:

—CTR = PRD:与指定时间段相等的时基计数器(TBCTR = TBPRD)。

—CTR = 0:定时器等于零(TBCTR = 0x00)。

•配置时基时钟的速率;ePWM时钟(EPWMCLK)的预缩放版本。这允许时基计数器以较慢的速率递增/递减。

如果应用程序代码要求在TBCTR计数时通过软件更新TBCTR值,请注意时基模块至少需要1

TBCLK周期才能实现与时基相关的事件。因此,TBCTR可以写为TBCTR = PRD-1而不是TBCTR =

PRD(在计数器向上计数的情况下),也可以写为TBCTR = 1而不是TBCTR = 0(在计数器向下计数的情况下),以便实现事件。

控制和监视时基子模块

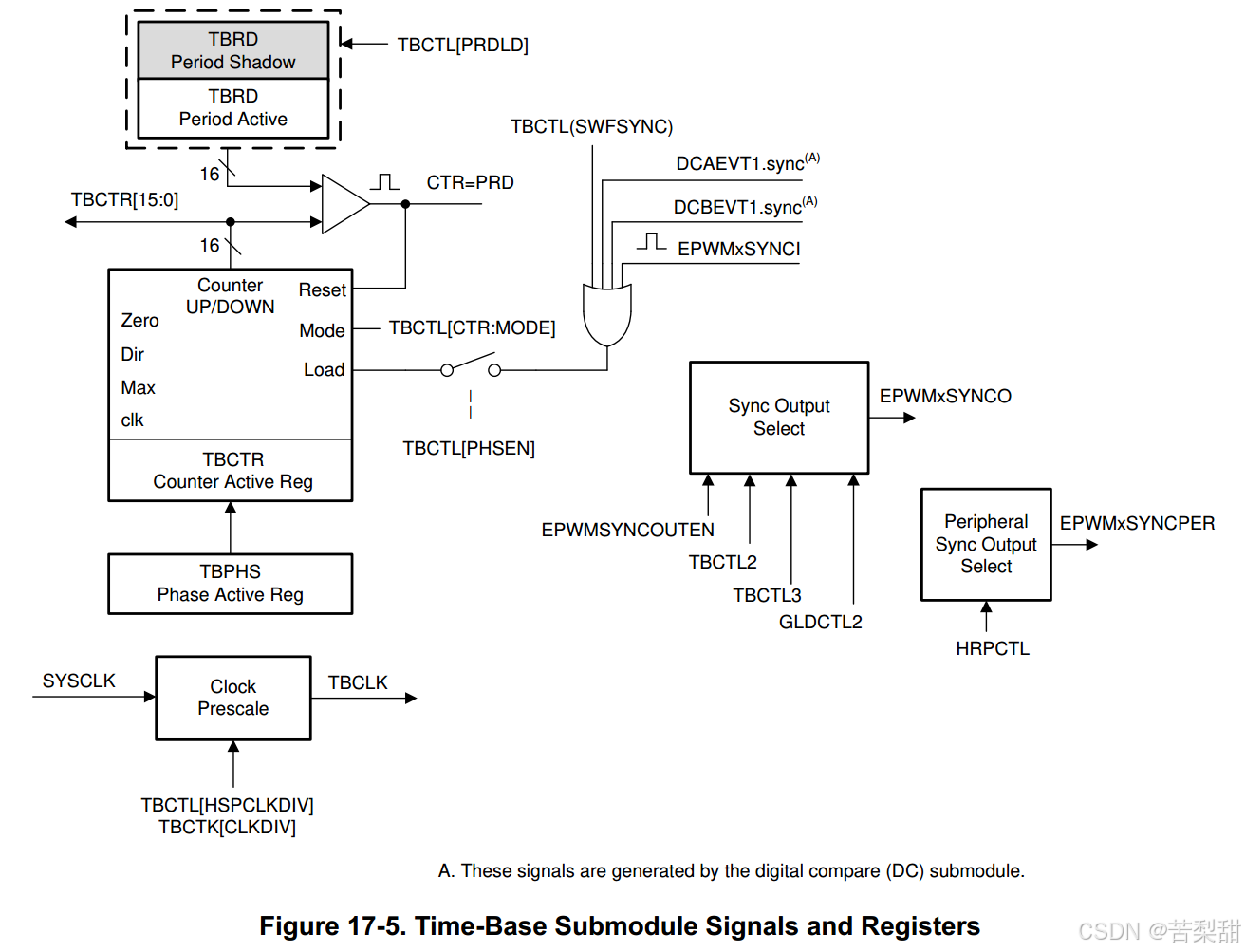

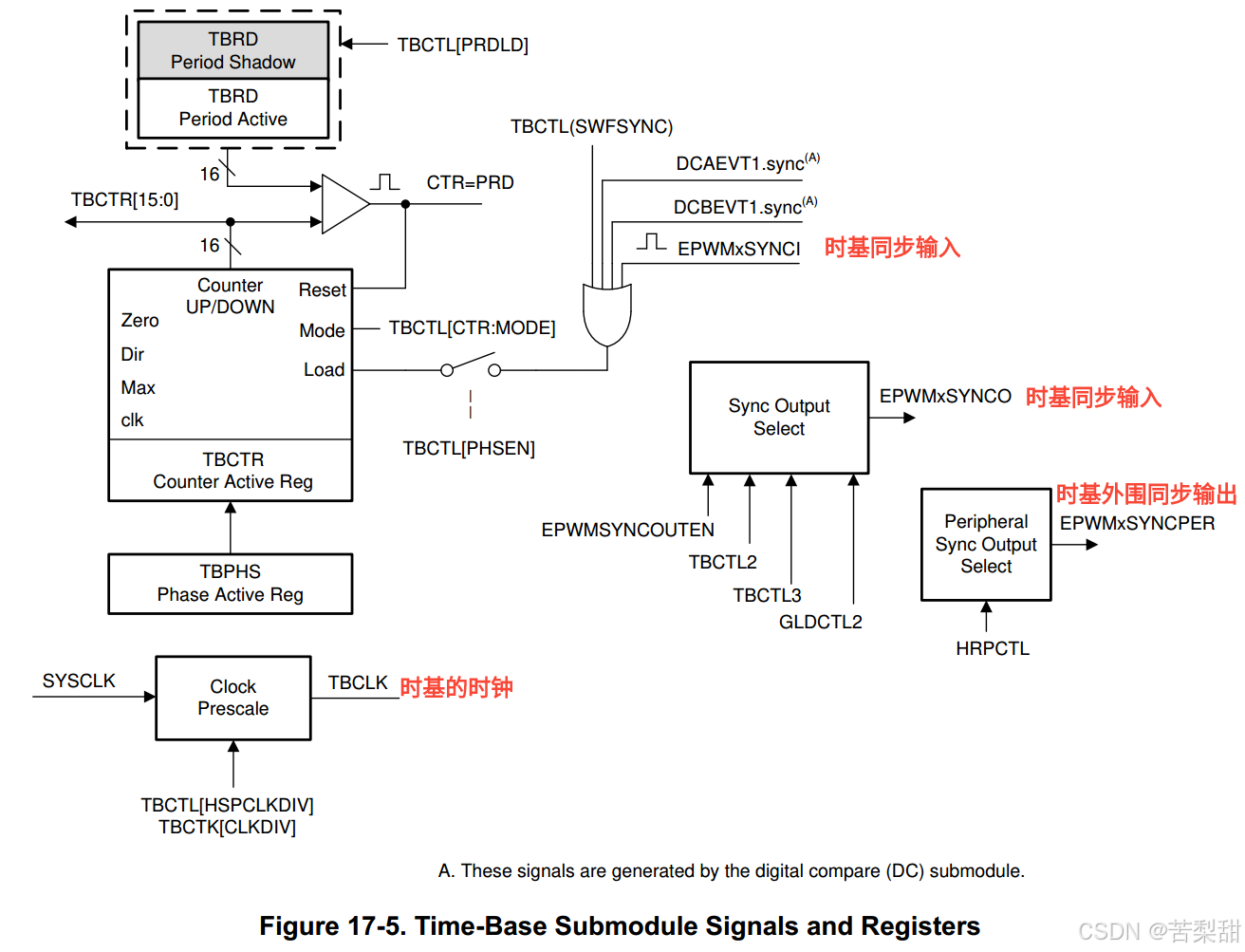

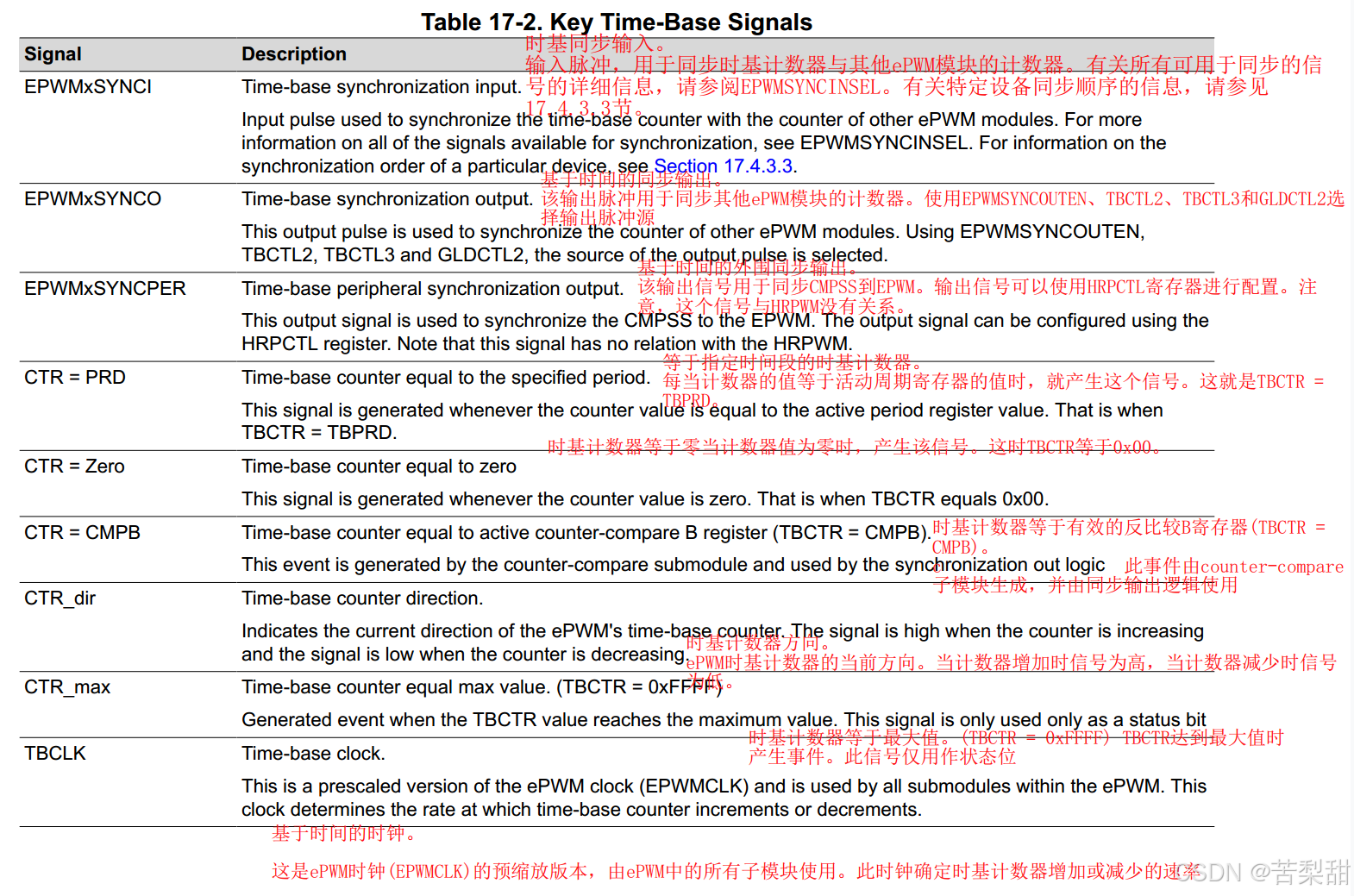

时序子模块的关键信号和寄存器框图如图所示。与时基子模块相关的关键信号说明如表所示。

计算PWM周期和频率

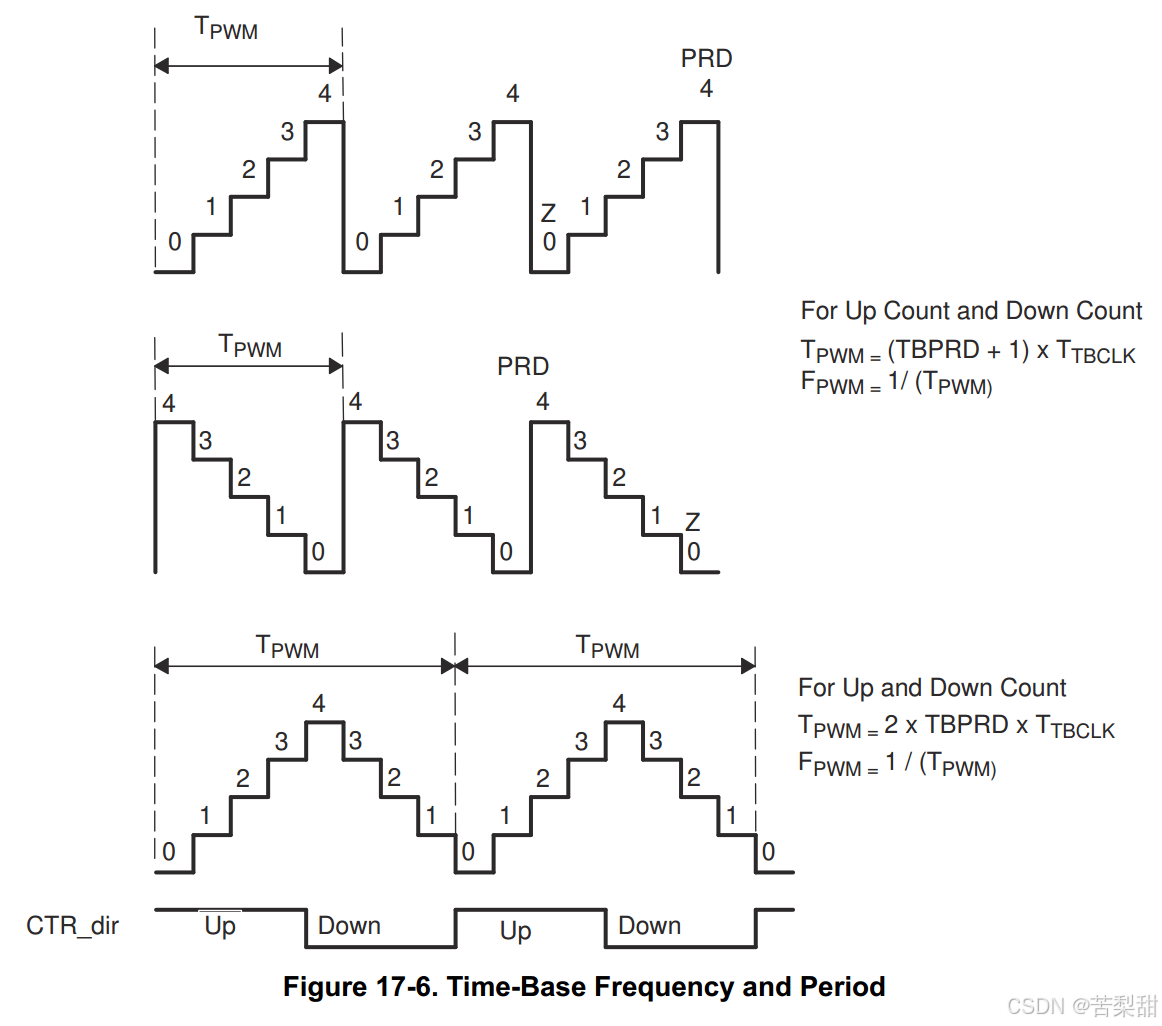

PWM事件的频率由时基周期(TBPRD)寄存器和时基计数器的模式控制。图显示了周期设置为4 (TBPRD = 4)时,up-count、down-count和up-down-count时基计数器模式的周期(Tpwm)和频率(Fpwm)关系。每一步的时间增量由时基时钟(TBCLK)定义,它是ePWM时钟(EPWMCLK)的预缩放版本。

时基计数器有三种由时基控制寄存器(TBCTL)选择的工作模式:

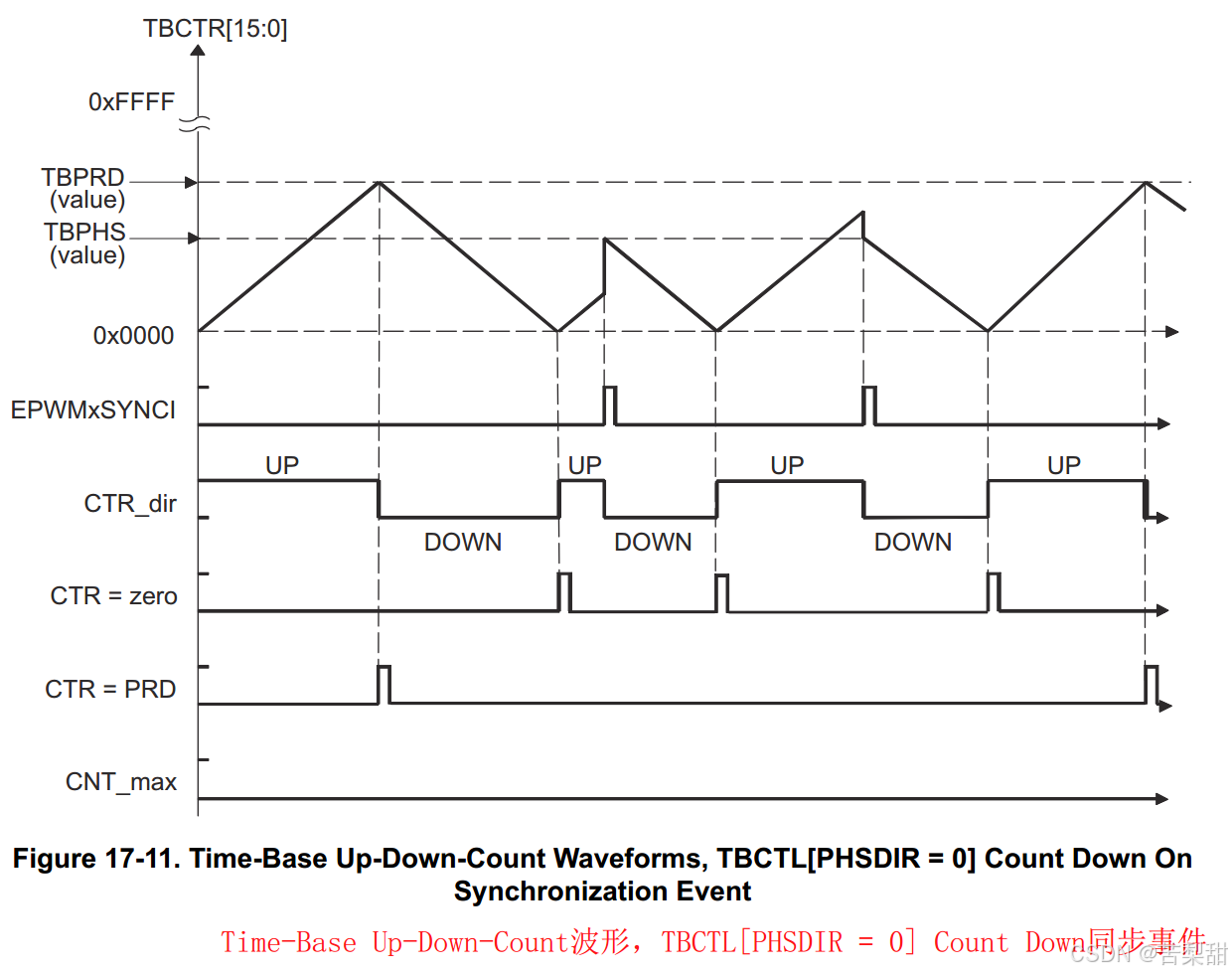

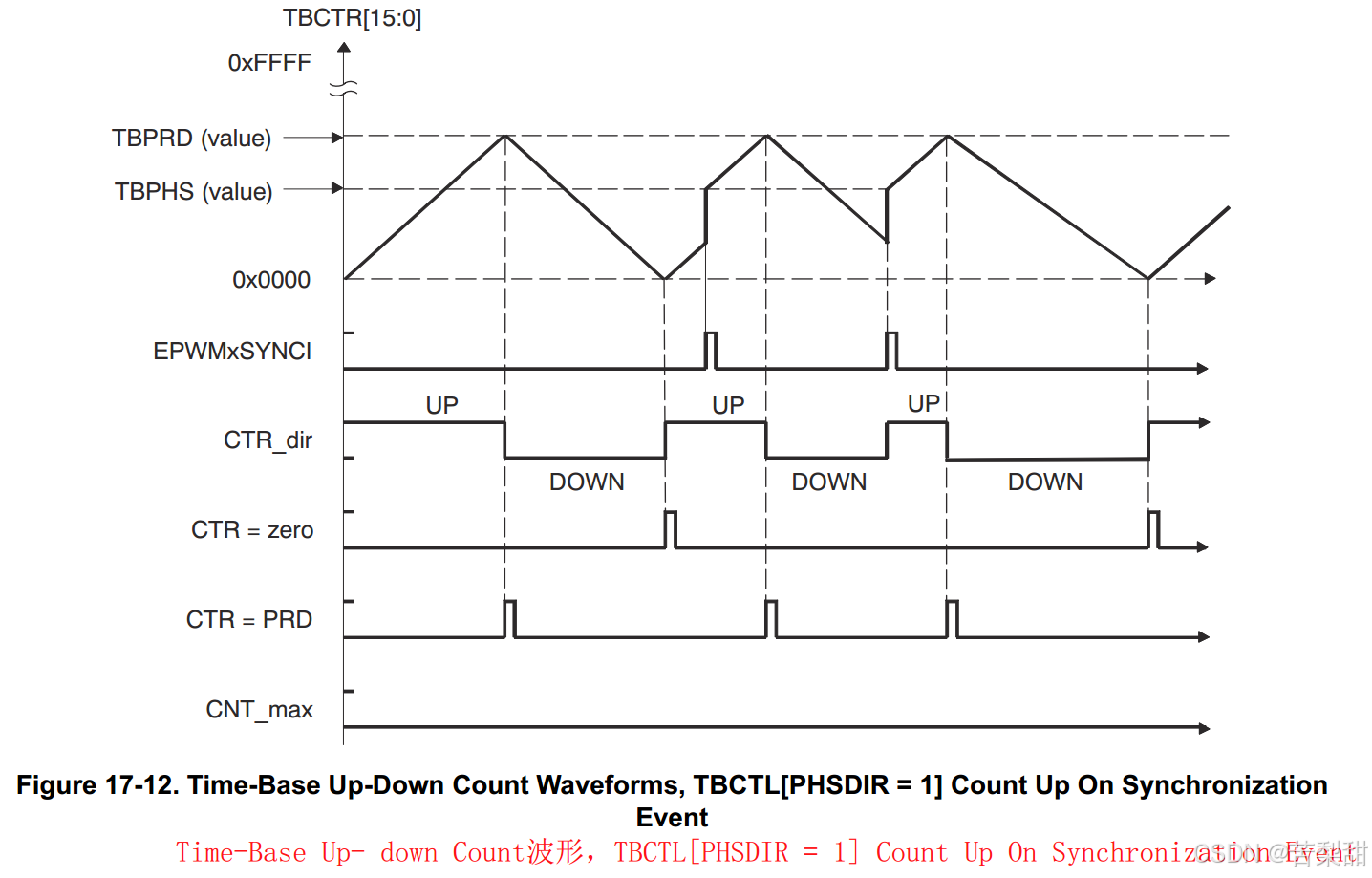

•上下计数模式:在上下计数模式下,时基计数器从零开始递增,直到达到周期(TBPRD)值。当达到周期值时,时基计数器然后递减,直到计数器达到零。此时,计数器重复该模式并开始递增。

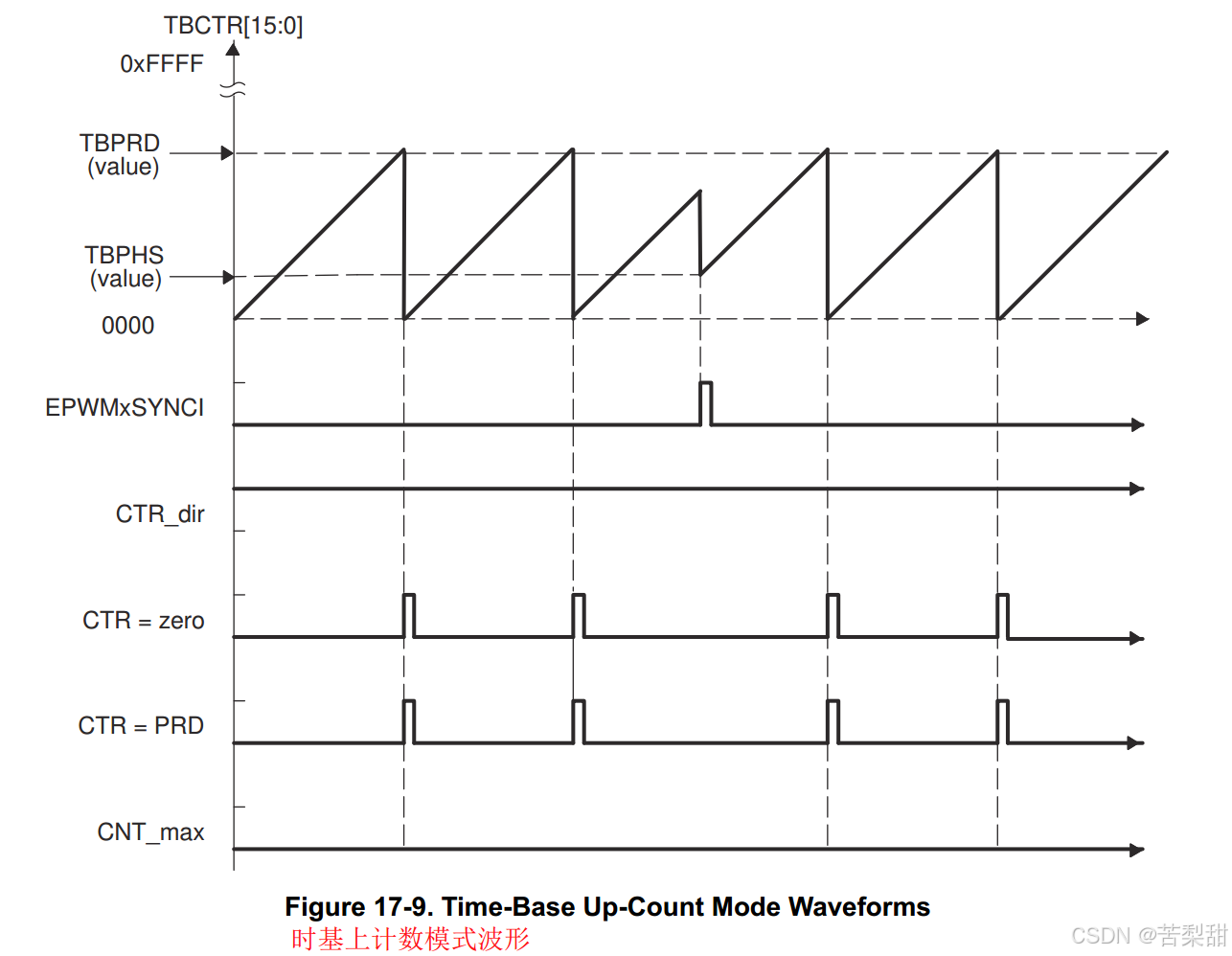

•Up-Count模式:在Up-Count模式下,时基计数器从零开始递增,直到计数器达到周期寄存器(TBPRD)中的值。当达到周期值时,时基计数器重置为零并再次开始增加。

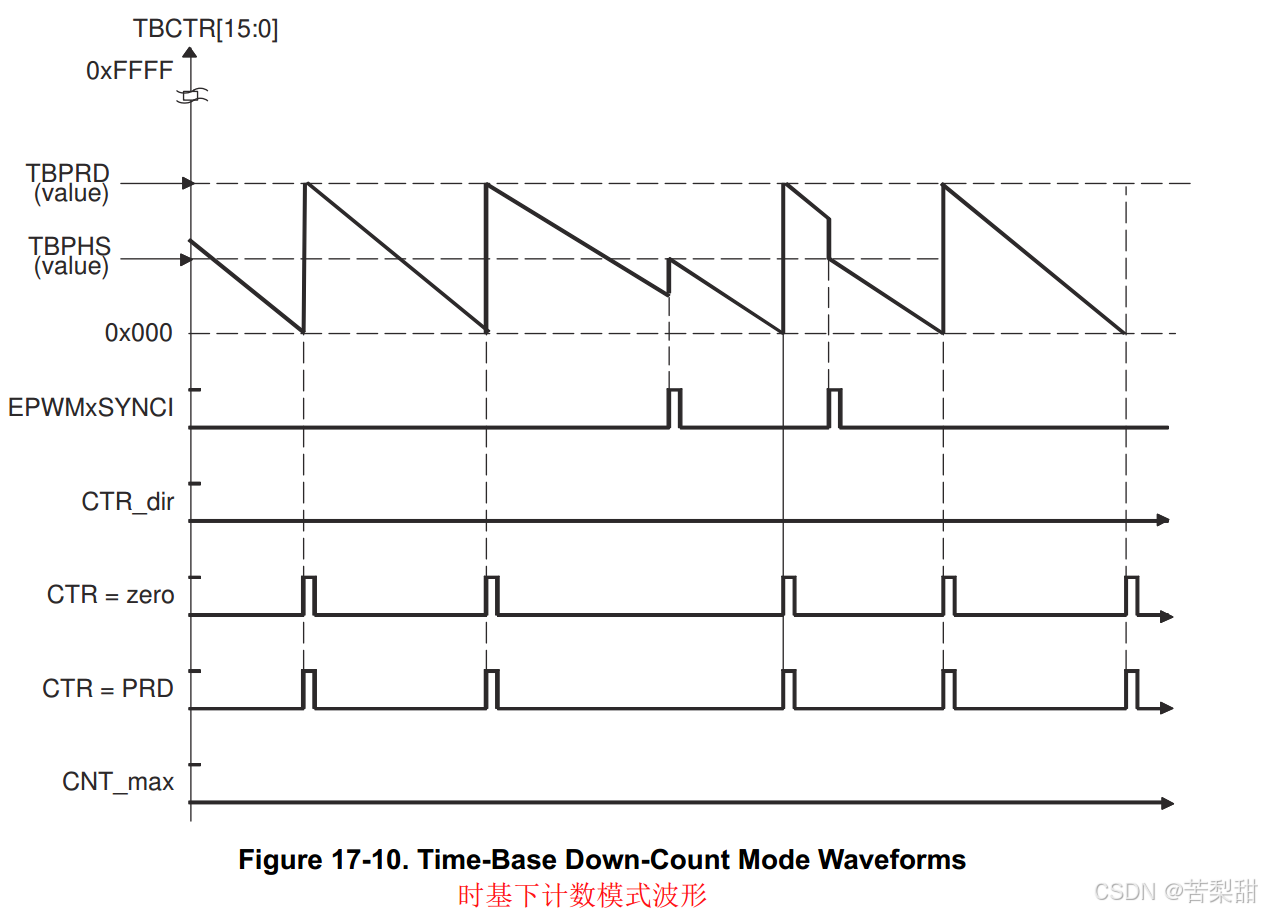

•Down-Count模式:在Down-Count模式下,时基计数器从周期(TBPRD)值开始递减,直到计数为零。当计数器达到零时,时基计数器被重置为周期值并再次开始递减。

时基期影子寄存器

时基周期寄存器(TBPRD)有一个影子寄存器。影子允许寄存器更新与硬件同步。以下定义用于描述ePWM模块中的所有影子寄存器:

•活动寄存器:活动寄存器控制硬件并负责硬件引起或调用的操作。

•影子寄存器:影子寄存器缓冲区为活动寄存器提供一个临时保存位置,对任何控制硬件没有直接影响。在一个策略时间点上,影子寄存器的内容被转移到活动寄存器。这可以防止由于软件异步修改寄存器而导致的损坏或虚假操作。

影子周期寄存器的内存地址与活动寄存器相同。向哪个寄存器写入或从哪个寄存器读取由TBCTL[PRDLD]位决定。

•时基期阴影模式:TBPRD阴影寄存器在TBCTL[PRDLD] = 0时启用。

从TBPRD内存地址读取和写入到影子寄存器。当时基计数器等于零(TBCTR = 0x00)和/或由TBCTL2[PRDLDSYNC]位确定的同步事件时,影子寄存器的内容被转移到活动寄存器(TBPRD (active)←TBPRD (shadow))。

只有TBCTL[PRDLD] = 0时,PRDLDSYNC位才有效。默认情况下,TBPRD影子寄存器是启用的。

SYNC输入的来源将在后面节中解释。

通过在全局负载配置寄存器(GLDCFG)中配置适当的位,全局负载控制机制也可以与时基周期寄存器一起使用。当选择全局加载模式时,将内容从影子寄存器传输到活动寄存器,对于启用此模式的所有寄存器,发生在与全局阴影到活动负载控制寄存器(GLDCTL)中的配置位定义的相同事件中。

•Time-Base Period Immediate Load Mode:如果选择了Immediate Load Mode (TBCTL[PRDLD] = 1),那么对TBPRD内存地址的读或写将直接进入活动寄存器。

时基的时钟同步

外围时钟使能寄存器中的TBCLKSYNC位允许所有用户全局同步所有使能的ePWM模块到时基时钟(TBCLK)。当设置时,所有启用的ePWM模块时钟都以TBCLK的第一个上升沿对齐开始。对于同步tbclk,每个ePWM模块的预分频器必须设置相同。

使能ePWM时钟的正确步骤如下:

1.启用ePWM时钟,使能PCLKCRx寄存器中的ePWM模块时钟。

2. 设置TBCLKSYNC= 0

3. 配置ePWM模块

4. 设置TBCLKSYNC= 1

时基计数器同步

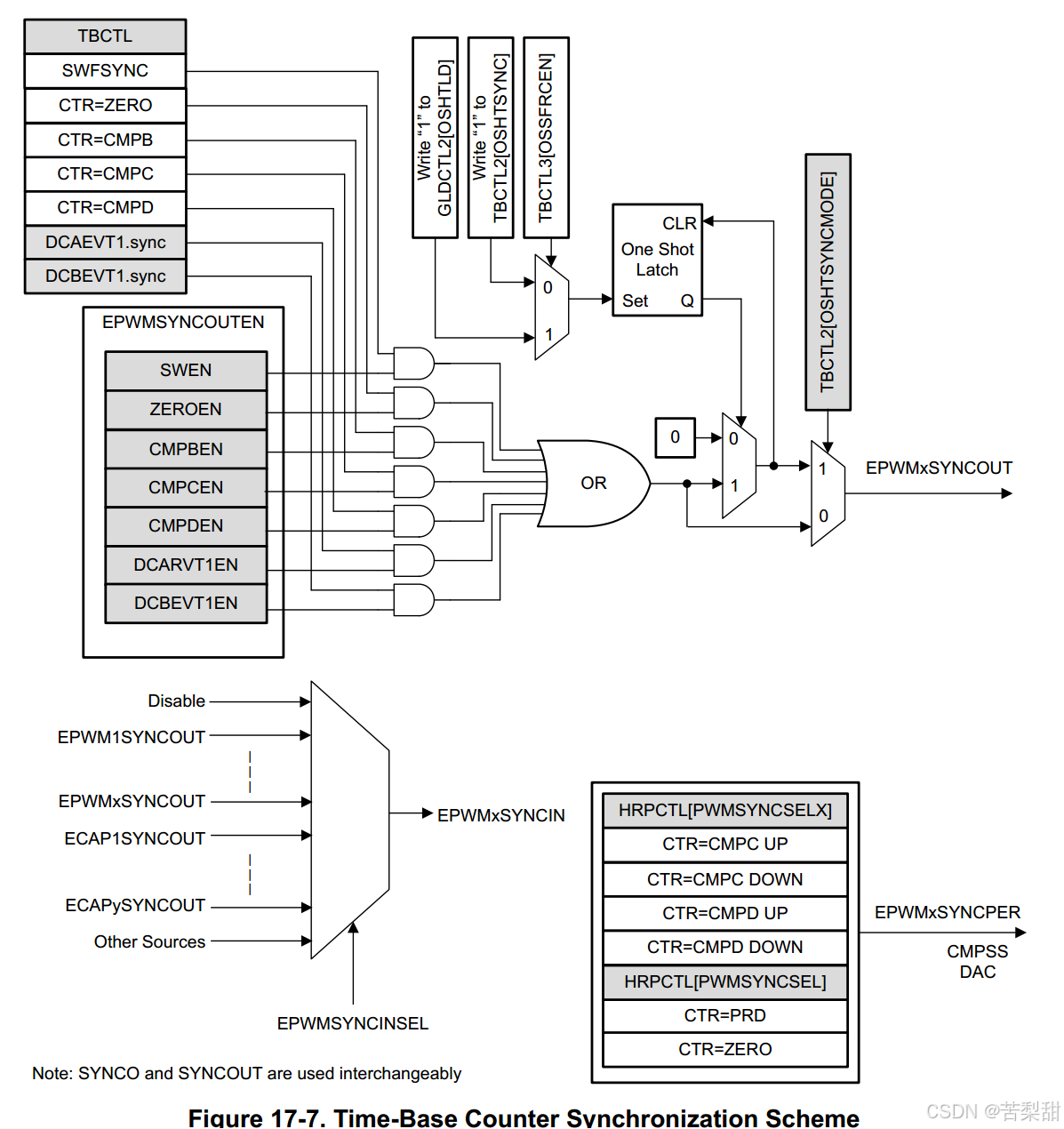

ePWM同步方案增加了ePWM模块同步的灵活性。

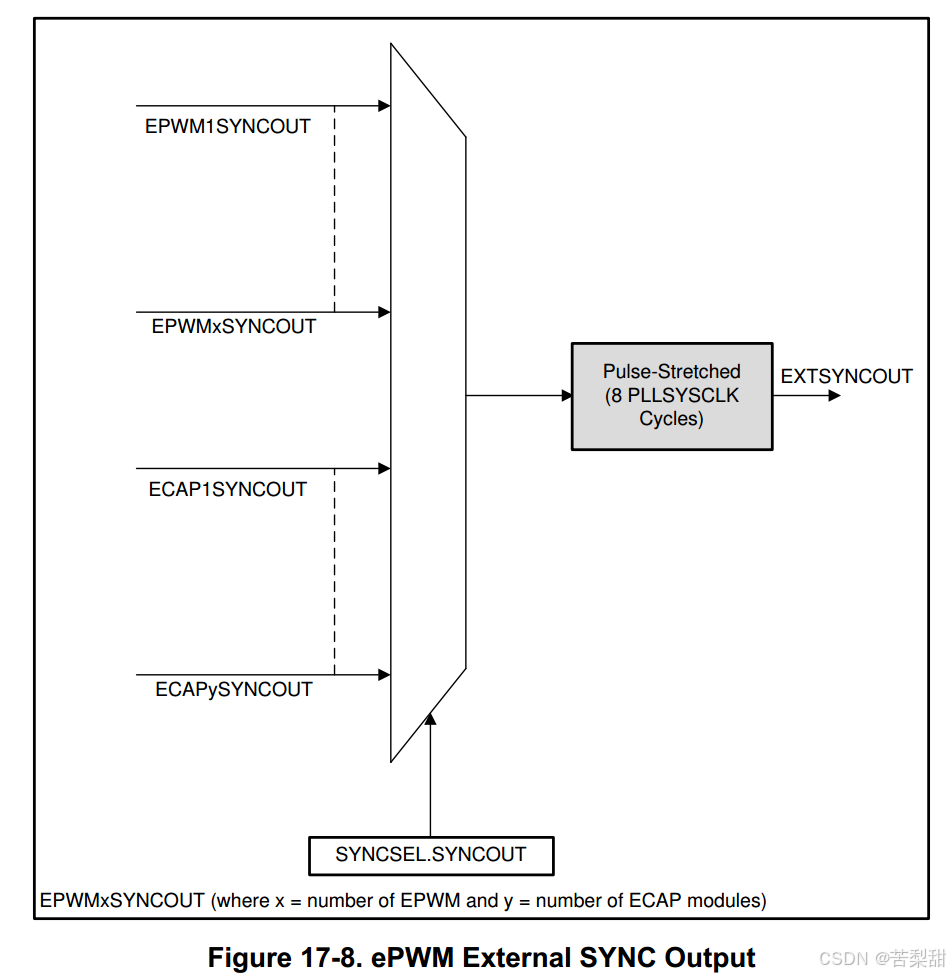

每个ePWM模块有同步输入(SYNCI)、同步输出(SYNCO)和外设同步输出(SYNCPER)。图中,EXTSYNCIN1来源于INPUTXBAR5, EXTSYNCIN2来源于INPUTXBAR6,可以配置为选择任意GPIO作为同步输入。参考17.4.3.4节获取所有同步输入的列表,包括INPUTXBAR5和INPUTXBAR6。EXTSYNCOUT可以使用的源如图所示。

每个ePWM模块都可以配置使用或忽略同步输入。如果设置了TBCTL[PHSEN]位,则ePWM模块的时基计数器(TBCTR)在发生以下情况之一时自动加载相寄存器(TBPHS)内容:

•EPWMxSYNCI:同步输入脉冲:当检测到输入同步脉冲(TBPHS→TBCTR)时,相位寄存器的值被加载到计数器寄存器中。该操作发生在下一个有效的基准时钟(TBCLK)边缘。

从内部控制模块到目标模块的延迟由以下公式给出:

—if (TBCLK = EPWMCLK): 2 × EPWMCLK

—if (TBCLK < EPWMCLK): 1 × TBCLK

•软件强制同步脉冲:将1写入TBCTL[SWFSYNC]控制位会调用软件强制同步。该脉冲与同步输入信号相匹配,因此与EPWMxSYNCI上的脉冲具有相同的效果。

•数字比较事件同步脉冲:DCAEVT1和DCBEVT1数字比较事件可以配置为产生与EPWMxSYNCI具有相同影响的同步脉冲。

如果EPWMxSYNCI信号保持高位,则不会持续进行同步。EPWMxSYNCI上升沿激活

该特性使ePWM模块能够自动同步到其他ePWM模块的时基。前置或滞后相位控制可以添加到由不同ePWM模块产生的波形中以同步它们。在up-down-count模式下,TBCTL[PHSDIR]位在同步事件发生后立即配置时基计数器的方向。新方向独立于同步事件之前的方向。PHSDIR位在倒数模式下被忽略。

清除TBCTL[PHSEN]位配置ePWM忽略同步输入脉冲。

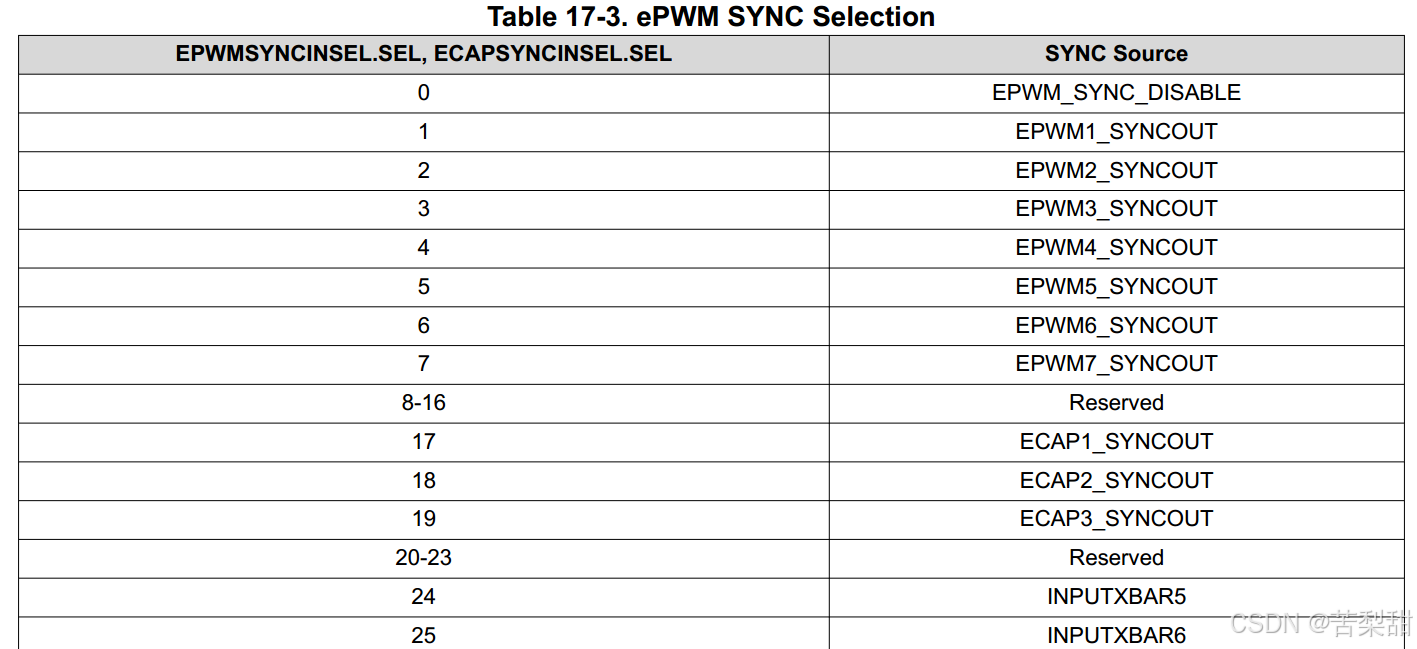

ePWM同步选择

ePWM SYNC的输入输出源如表所示

锁相多个ePWM模块的基准时钟

TBCLKSYNC位可用于全局同步设备上所有使能ePWM模块的时基时钟。该位是设备时钟使能寄存器的一部分,在官方手册的系统控制和中断部分进行了描述。TBCLKSYNC = 0时,所有ePWM模块的基准时钟默认停止。当TBCLKSYNC = 1时,所有ePWM时基时钟都以TBCLK的上升沿对齐开始。

对于完全同步的TBCLK,每个ePWM模块的TBCTL寄存器中的预量器位必须设置相同。使能ePWM时钟的正确步骤如下:

- 启用ePWM时钟。启用各个ePWM模块时钟。这在系统控制和中断一章中有描述。

- 设置TBCLKSYNC= 0。这将停止任何已启用的ePWM模块中的基准时钟。

- 配置预分频器值和所需的ePWM模式。

- 设置TBCLKSYNC = 1。

在ePWM模块之间同时写TBPRD和CMPx寄存器

对于变频应用,需要在ePWM模块之间同时写TBPRD和CMPx寄存器。这可以防止CTR = 0或CTR = PRD脉冲在ePWM模块之间更新所有寄存器之前强制这些寄存器的影子主动加载的情况(导致一些寄存器从新的阴影值加载,而其他寄存器从旧的阴影值加载)。为了支持这一点,在PWM模块之间添加了TBPRD:TBPRDHR, CMPA: CMPAHR, CMPB:CMPBHR, CMPC和CMPD寄存器的ePWM寄存器链接方案。

参考EPWMXLINK的寄存器描述,查看相应ePWM的链接寄存器位域值。使用EPWMXLINK的一个例子是通过ePWM2的EPWMXLINK[CMPALINK]寄存器位域将ePWM2的CMPA与ePWM1的CMPA连接起来。在这种情况下,写入ePWM1的CMPA也会改变ePWM2的CMPA值。

时基计数器模式和定时波形

时基计数器有四种工作模式:

•不对称的Up-count模式

•不对称的Down-count模式

•对称的Up-down-count模式

•冻结时,基时计数器保持在当前值不变。

为了说明前三种模式的操作,下面的时序图显示了事件产生的时间以及基时如何响应EPWMxSYNCI信号。

全局加载

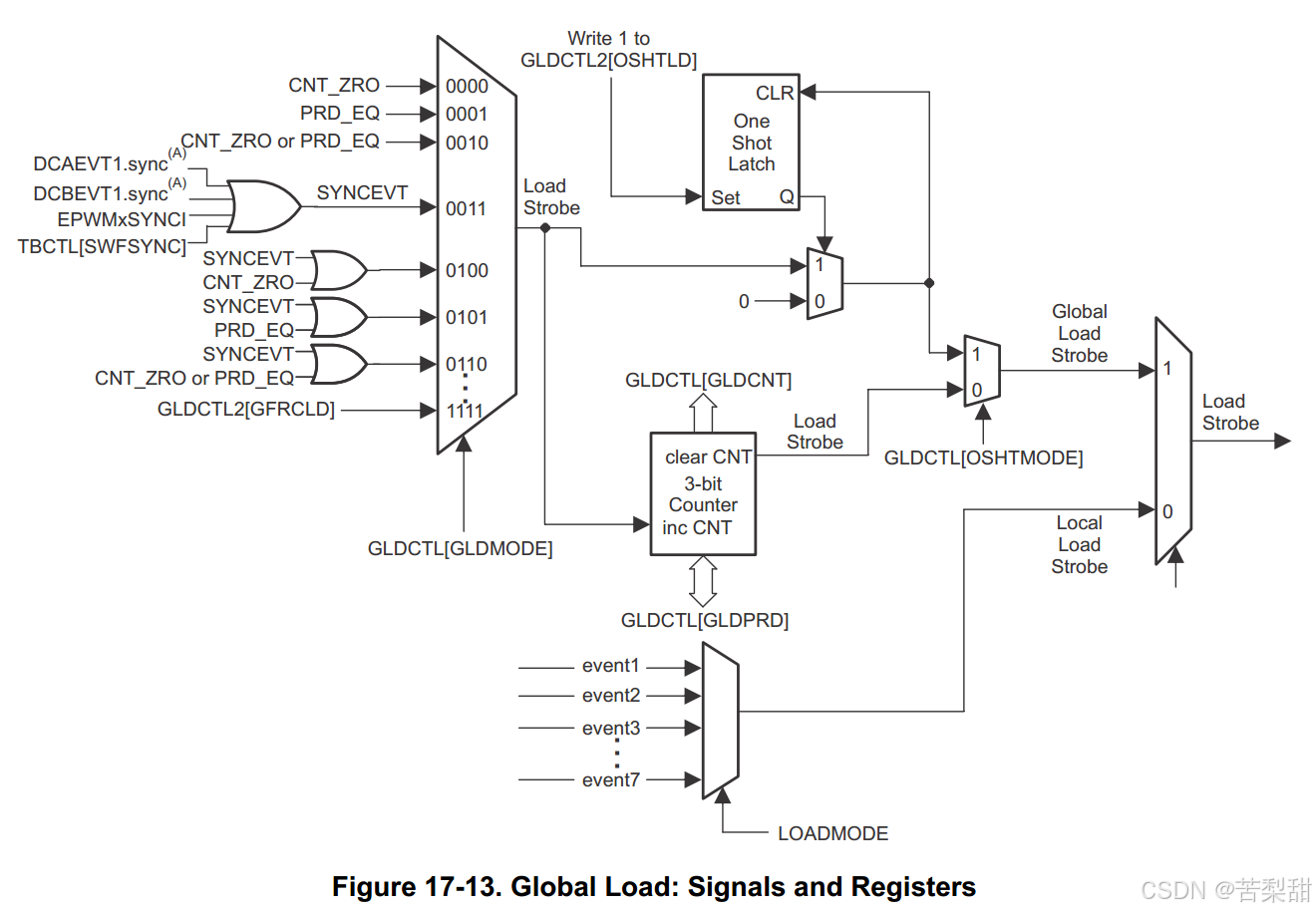

与全局加载特性相关的信号和寄存器如图所示。

SYNCEVT信号仅在PHSEN设置时传播。

当启用此功能时,对于启用此模式的所有寄存器,将内容从影子寄存器转移到活动寄存器,发生在与全局阴影到活动负载控制寄存器(GLDCTL[GLDMODE])中的配置位定义的相同事件中。当GLDCTL[GLD] = 1时,单个阴影寄存器的阴影到活动加载事件选择位被忽略,全局加载模式对GLDCFG[REGx]启用的相应寄存器生效。

当GLDCTL[GLD] = 1和GLDCFG[REGx] = 0时,全局加载模式不影响对应的寄存器(REGx)。单个阴影寄存器的阴影到活动负载事件选择位决定如何将内容从阴影寄存器转移到活动寄存器。

全局负载脉冲预标量

该特性提供了选择阴影的能力,以在选中的全局负载脉冲(GLDCTL[GLDMODE])出现的“N”次中发生一次活动传输。对于不能或未配置为使用全局加载机制的寄存器(即GLDCTL[GLD] = 0或GLDCFG[REGx] = 0),此预伸缩功能不可用。

一次加载模式

此功能允许用户使影子寄存器到活动寄存器的传输只发生一次。当GLDCTL2[OSHTLD] = 1时,对于配置为使用全局加载机制的寄存器,影子到活动寄存器的传输发生在GLDCTL[GLDMODE]选择的事件上。

通过使用GLDCTL2[GFRCLD],可以将内容从影子寄存器强制加载到活动寄存器。GLDCTL2寄存器也可以通过使用EPWMXLINK[GLDCTL2LINK]跨多个PWM模块链接。这与上面讨论的单次负载模式特性一起提供了一种方法,可以在某些PWM事件或(如果需要的话)在同一时钟周期内正确更新一个或多个PWM模块中的多个PWM寄存器。这在变频应用和/或多相交错应用中非常有用。

当启用高分辨率模式时,不能使用一次性加载模式。

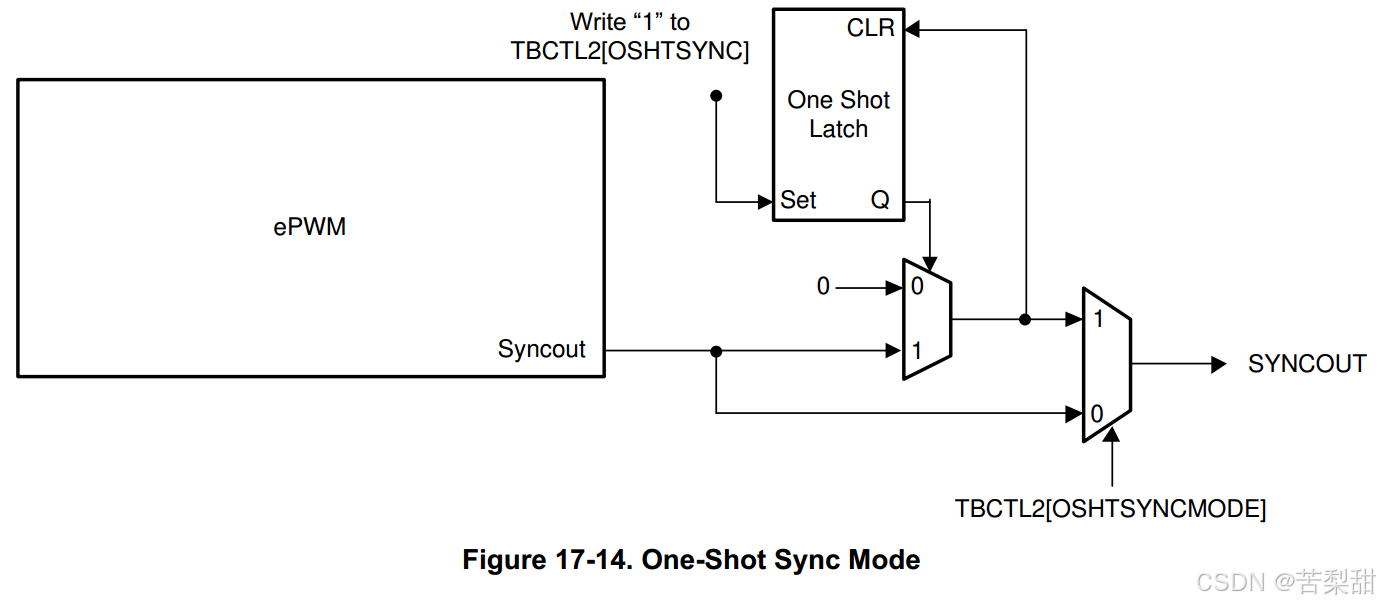

一次同步模式

配置TBCTL2[OSHTSYNCMODE]位,并设置TBCTL2[OSHTSYNC]位,如图所示

2237

2237

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?