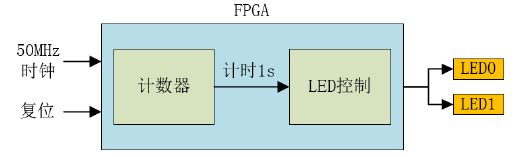

上图为控制led灯闪烁的原理图,其中时钟信号、复位信号为输入信号,led为输出信号,led包括led0和led1,所以输出信号应该是两位的,时钟的频率为50MHz,所以计时一秒需要50M次。本次实验以两个灯分别亮0.5秒。 核心板和底板的led灯都是共阴极的,需要给高电平。

module led_twinkle(

input clk, //定义时钟信号

input rst_n, //定义复位信号,低电平有效

output [1:0] led //定义两位led信号

);

reg [25:0] cnt; //设置26位二进制寄存器,用于计数

assign led=(cnt<=2500_0000) ? 2'b01 : 2'b10; //组合逻辑,0.5秒前亮led0,0.5秒后亮led1

always @ (posedge clk or negedge rst_n) begin //时序逻辑,敏感信号为时钟上升沿和复位下降沿

if(!rst_n)

cnt<=26'd0;

else if(cnt<26'd5000_0000)

cnt<=cnt+1'b1;

else

cnt<=26'd0; //两种复位条件,一种是复位信号为低电平一种

end //是计数值达到要求

endmodule存在问题: cnt<=cnt+1'b1; 可以进行

7718

7718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?