首先,关于为何要学习亚稳态我认为有以下几点:

1.亚稳态中涉及建立/保持时间的概念,涉及跨时钟域传输的概念,在面试的过程中,肯定会被问及亚稳态相关的知识。(带有极强的功利性)

2.亚稳态是FPGA系统中的一个常见问题,亚稳态的出现,轻则导致输出错误,重则会影响系统崩溃。

3.在异步信号的采集中,由于传输的数据足够多,则容易发生亚稳态,若不对亚稳态进行处理,则采集到的信号是不稳定的,然后发生连锁反应导致后面所有的数据出错。

在学习亚稳态之前需要了解两个概念

1.建立时间Tsu(T setup)

2.保持时间Th(T hold)

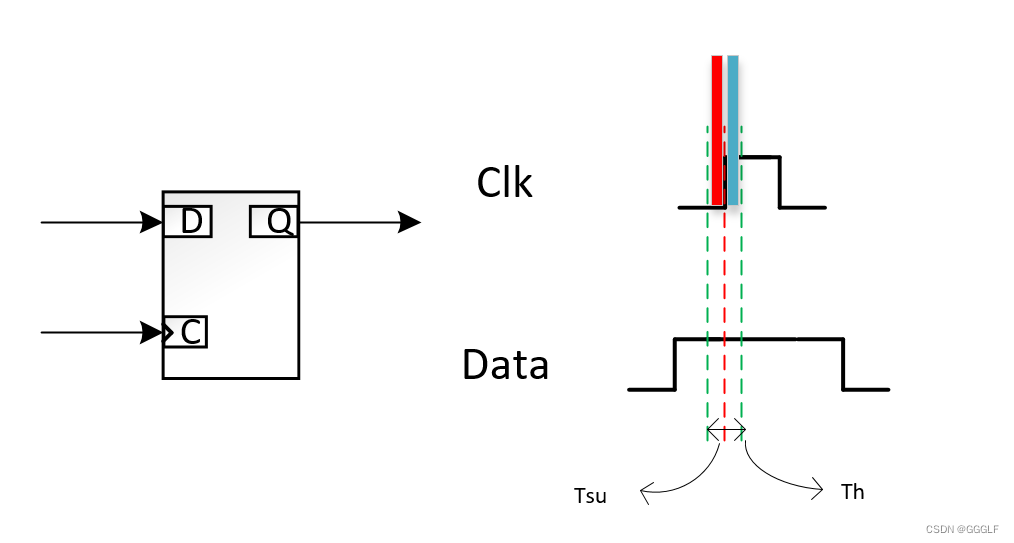

以下图的D触发器为例,在时钟clk上升沿到来的时候,数据data会被锁存到触发器中。但是,这个锁存是有条件限制的。首先,需要锁存进触发器的数据需要到时钟的上升沿到来之前稳定一段时间,也就是说在红色区域的时间之前数据data必须稳定,不然则不满足建立时间,即时序违例了(红色区域内稳定)。

同样地,在上升沿到来之后,数据data还需要稳定一段时间,这个时间我们称之为保持时间Th,数据data必须在Th(绿色)时间外面才能发生变化;若在Th内数据发生变化,则不满足保持时间,也是时序违例。

简单来说,建立时间规定了数据data在时间上升沿到来之前必须保持一段时间,保持时间规定了数据data在上升沿结束之后数据必须稳定一段时间,只有同时满足建立时间和保持时间,才认为时序没有违例,数据才不会发生亚稳态。

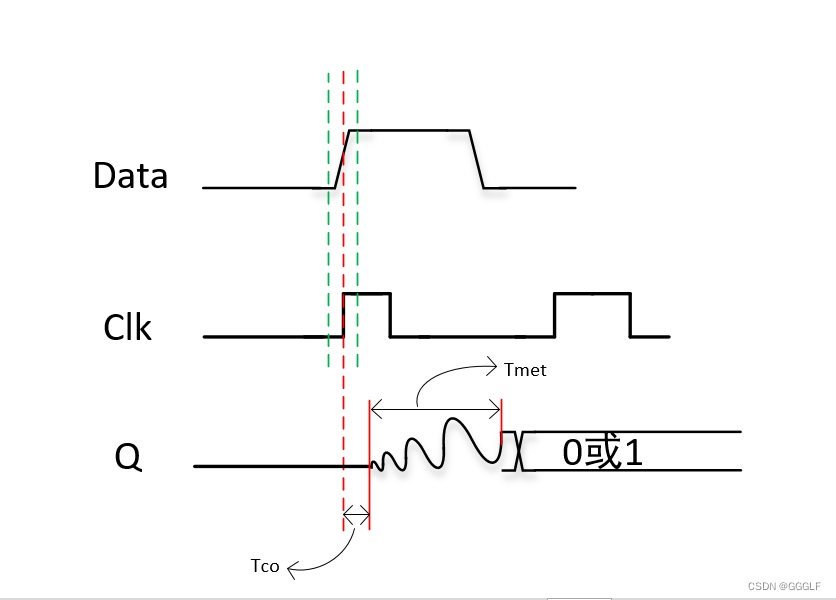

亚稳态的发生:即建立时间和保持时间不满足(在建立时间和保持时间内,数据发生了变化)如下图所示,则在此时会发生什么呢??会发生亚稳态!

首先解释一下,Tco为寄存器的延迟,经过Tco的反应时间后,输出端才会发生变化;Tmet为决断时间,在决断时间Tmet内,输出信号的值会发生振荡。

经过Tmet的振荡时间后,寄存器的值会稳定,但稳定在0或者1是不确定的。

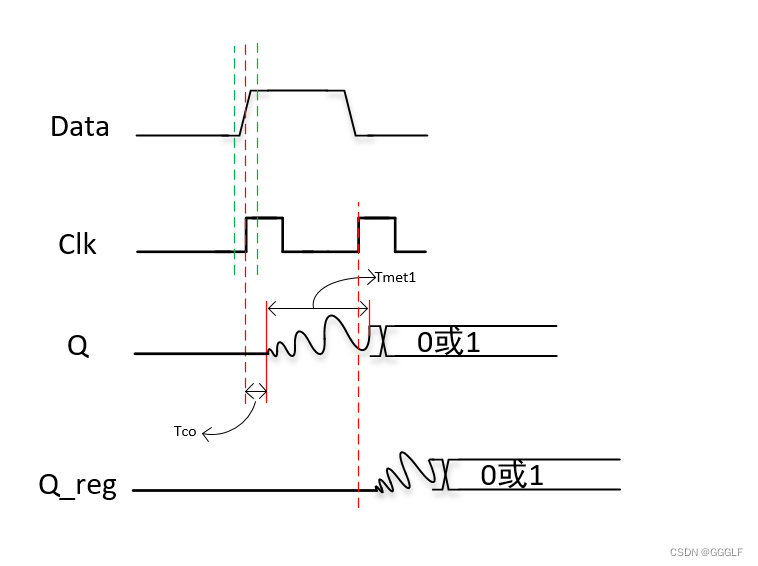

若第一级寄存器Q的Tmet1大于一个采样周期时,第二级寄存器就会采集到一个亚稳态。

那么如何消除这种亚稳态的产生呢?

由于寄存器本身有减小Tmet让数据快速稳定的作用,所以第二级寄存器所采集到的信号就是相对稳定的信号了。

Q_reg为第二级寄存器,经过“打两拍”之后已经是一个相对来说比较稳定的信号了,就可以使用了。

注意:延迟两拍后虽然能让信号稳定到0或者1中某一个确定的值,但到底时0还是1却是随机的,其与延迟之前的输入信号没有必然的联系。

上述我们是将单比特信号,从慢速时钟域同步到快速时钟域,使用消除亚稳态的方法是“打两拍”。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?