一、FPGA板卡的介绍

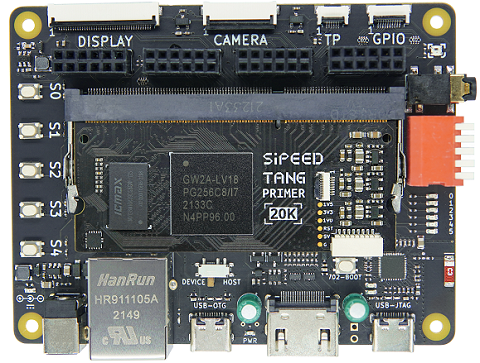

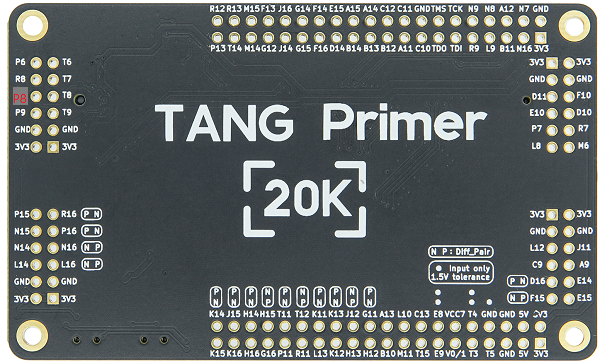

核心板:GW2A-LV18PG256C8IC8I7

底板:Dock底板

有关核心板和底板相关资料的参考网址:Tang Primer 20K - Sipeed Wiki

FPGA硬件设计软件:高云云源软件;下载地址:广东高云半导体科技股份有限公司

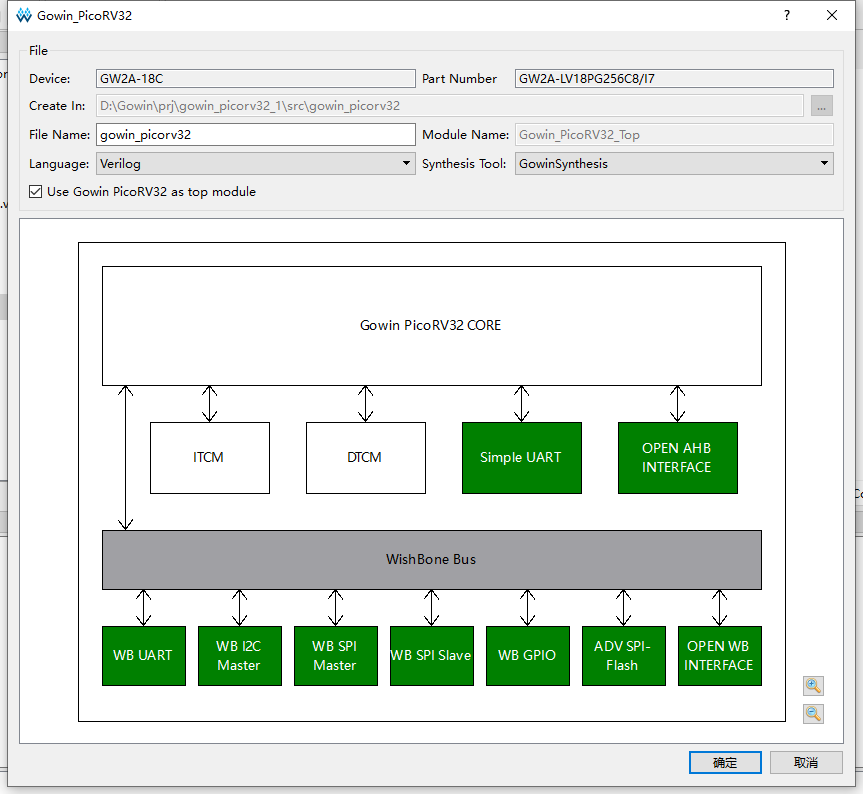

二、PicoRV32

PicoRV32描述,以及文档介绍详情见网址PicoRV32 - 高云 - 广东高云半导体科技股份有限公司

我们使用的PicoRV32的系统架构如下图所示

三、移植到FPGA

1、时序约束

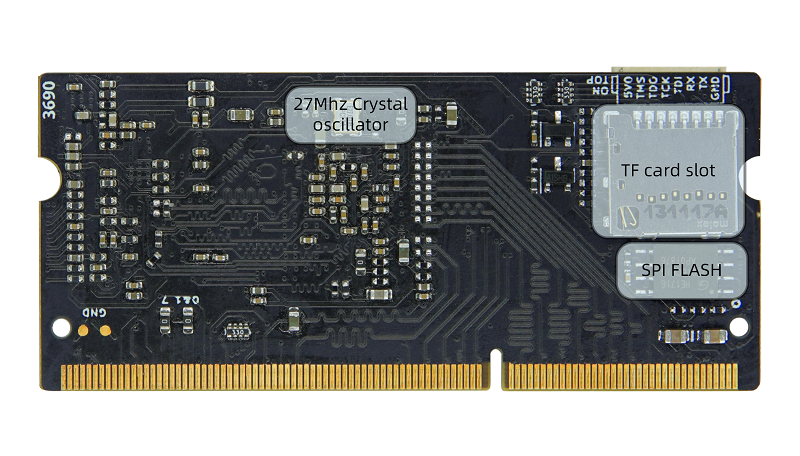

由于官方给的例程是基于DK_START_GW2A-LV18PG256C8I7_V2.0 开发板,该开发板板载的晶振为50MHz。开发板如下图

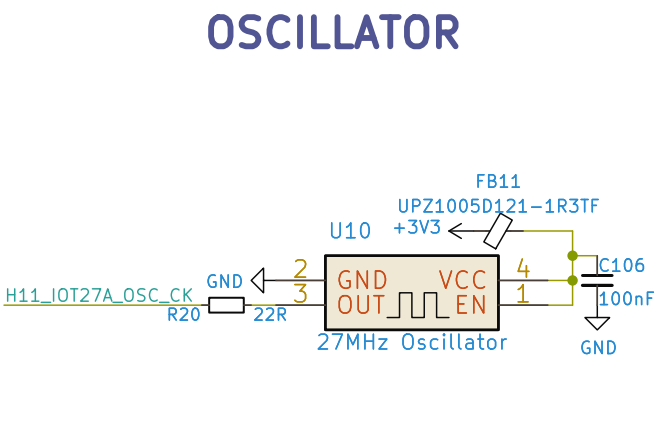

而对于我们手中的Tang prime 20k,板载的晶振为27MHz,时许的约束需要改。具体如下

2、管脚约束

如果仅仅测试该软核是否移植成功,仅需要修改时钟、复位及中断按键、led灯以及UART串口的对应管脚。

①时钟管脚

//System clock

IO_LOC "clk_in" H11;

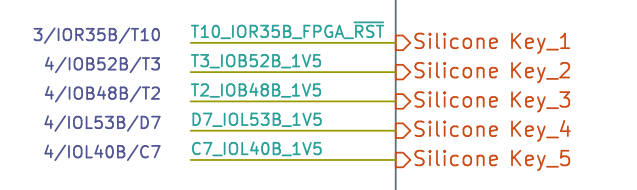

IO_PORT "clk_in" IO_TYPE=LVCMOS33;②复位及中断按键

//System reset

IO_LOC "resetn_in" T3;//KEY_4

IO_PORT "resetn_in" IO_TYPE=LVCMOS15;

//External Interrupt

IO_LOC "irq_in[0]" T2;//KEY_1

IO_LOC "irq_in[1]" D7;//KYE_2

IO_PORT "irq_in[0]" IO_TYPE=LVCMOS15;

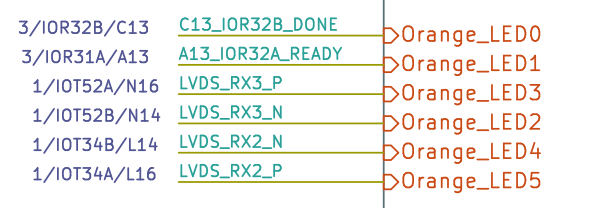

IO_PORT "irq_in[1]" IO_TYPE=LVCMOS15;③LED灯

//LED

IO_LOC "gpio_io[0]" L16;//LED1

IO_LOC "gpio_io[1]" L14;//LED2

IO_LOC "gpio_io[2]" N14;//LED3

IO_LOC "gpio_io[3]" N16;//LED4

IO_PORT "gpio_io[0]" IO_TYPE=LVCMOS33;

IO_PORT "gpio_io[1]" IO_TYPE=LVCMOS33;

IO_PORT "gpio_io[2]" IO_TYPE=LVCMOS33;

IO_PORT "gpio_io[3]" IO_TYPE=LVCMOS33;④UART串口

//WB UART

IO_LOC "wbuart_tx" M11;//J4_5

IO_LOC "wbuart_rx" T13;//J4_6

IO_PORT "wbuart_tx" IO_TYPE=LVCMOS33;

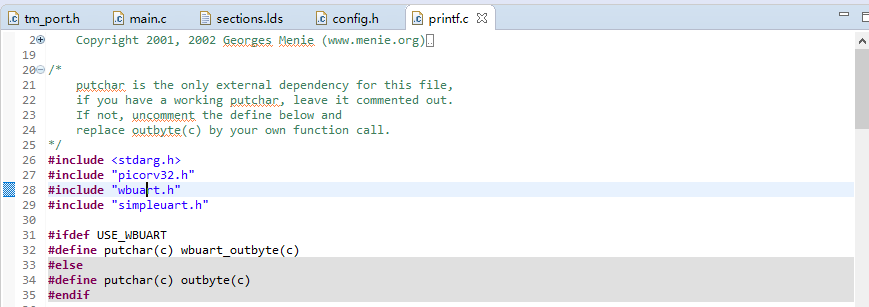

IO_PORT "wbuart_rx" IO_TYPE=LVCMOS33;PS:关于为何使用WB UART而不使用simple UART可以参考软核的程序

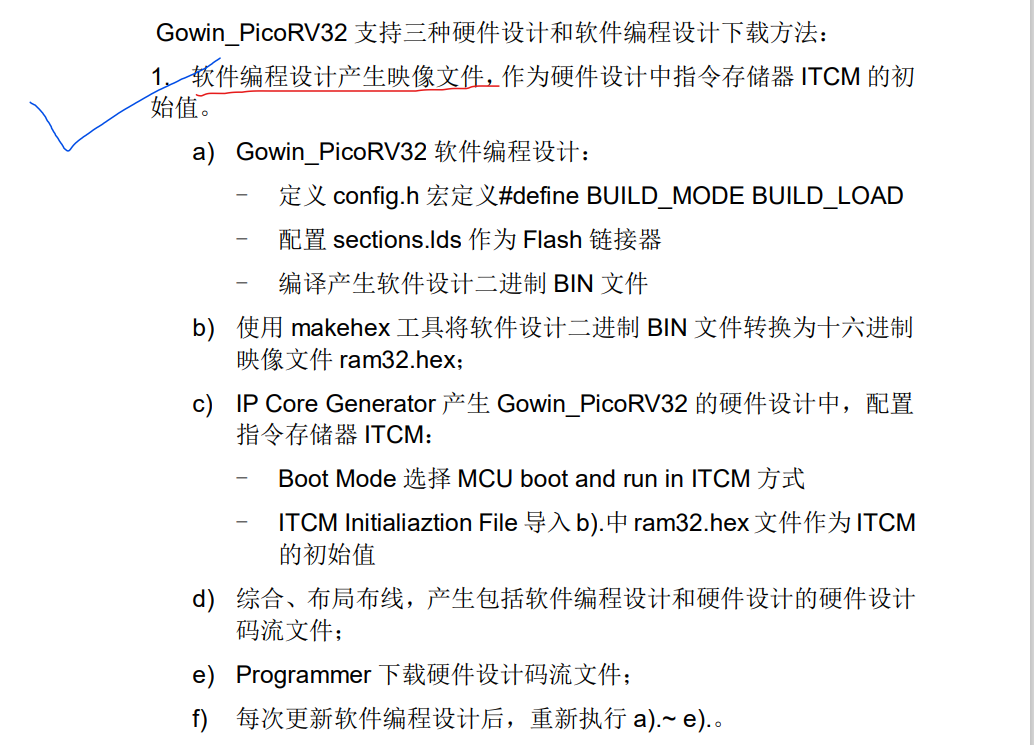

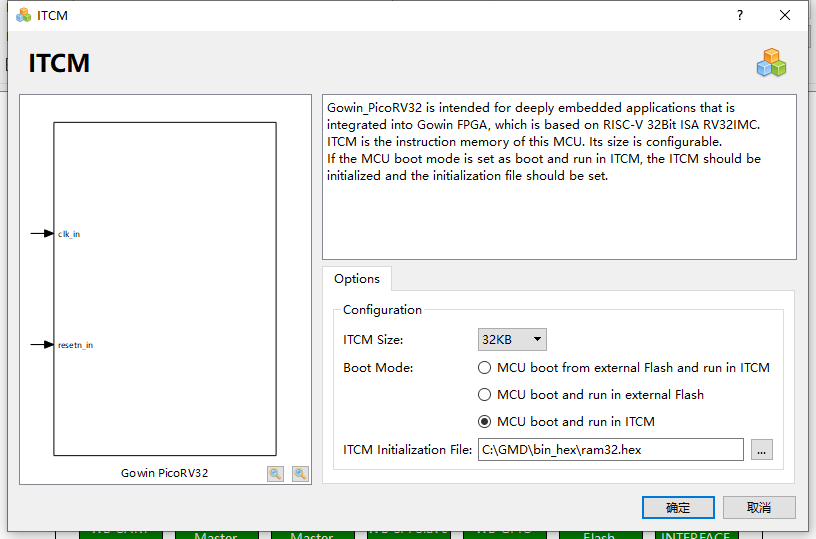

3、下载到板卡

由于我们采用的下载方式为“软件编程设计产生映像文件,作为硬件设计中指令存储器 ITCM 的初 始值”。下载流程如下图所示:

所以我们需要将生产的十六进制的hex映像文件加入到IP核中。

四、软件相关

编程软件:GOWIN MCU Designer V1.1.01教育版

下载地址:广东高云半导体科技股份有限公司

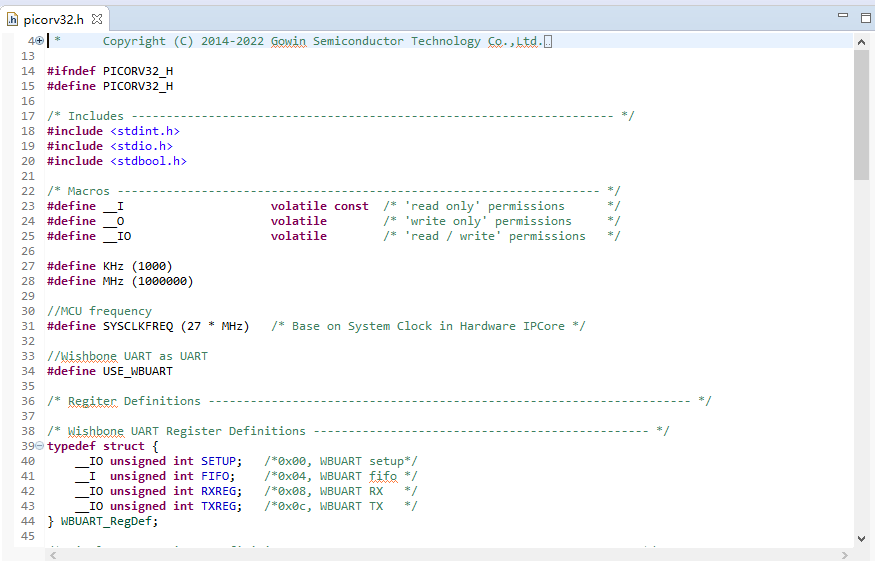

只需要修改picorv32.h中的时钟频率即可,将原本的50MHz改为27MHz

五、现象

连接好串口,波特率设置为115200。

板卡上的现象是四个LED灯轮流闪烁,并且串口打印数值符合main.c中的程序

串口打印的结果如代码块所示

------------- Gowin RiscV MCU <PicoRV32> Demo ----------------

MCU boot from and run in ITCM.

Open Wishbone interface demo beginning...

Wishbone extension demo, write and read back the three registers on the open Wishbone interface

Before write Wishbone demo register:

Reg0: 22222222

Reg1: 2222

Reg2: 22

After write Wishbone demo register:

Reg0: 33333333

Reg1: 3333

Reg2: 33

Open Wishbone interface demo finished. // main.c(wbreg_demo)

Open AHB bus interface demo beginning...

ahbreg0 is 01234567

ahbreg1 is 89abcdef

Open AHB bus interface demo finished. //main.c(ahbreg_demo)

Wishbone SPI-Flash demo beginning...

Read data by memory map mode from flash...

ffffffff ffffffff ffffffff ffffffff ffffffff c3a5ffff 00000006 1b080000 00000010 00000000 ffff0051 ffffffff 0000000b ffff00d2 00000000 00000012 3e08803b 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 08000000 00000010 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 10080000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00001400 00000000 00000000 00000000 00000000 00000000 00103000 00000000 00000000 00000008 00001030 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 03000000 00000001

Read initialized data from flash...

00 01 02 03 04 05 06 07 08 09 0a 0b 0c 0d 0e 0f 10 11 12 13 14 15 16 17 18 19 1a 1b 1c 1d 1e 1f 20 21 22 23 24 25 26 27 28 29 2a 2b 2c 2d 2e 2f 30 31 32 33 34 35 36 37 38 39 3a 3b 3c 3d 3e 3f 40 41 42 43 44 45 46 47 48 49 4a 4b 4c 4d 4e 4f 50 51 52 53 54 55 56 57 58 59 5a 5b 5c 5d 5e 5f 60 61 62 63

Erase flash...

Read data after erase flash...

ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff

Page program data...

Read data after page program flash...

00 01 02 03 04 05 06 07 08 09 0a 0b 0c 0d 0e 0f 10 11 12 13 14 15 16 17 18 19 1a 1b 1c 1d 1e 1f 20 21 22 23 24 25 26 27 28 29 2a 2b 2c 2d 2e 2f 30 31 32 33 34 35 36 37 38 39 3a 3b 3c 3d 3e 3f 40 41 42 43 44 45 46 47 48 49 4a 4b 4c 4d 4e 4f 50 51 52 53 54 55 56 57 58 59 5a 5b 5c 5d 5e 5f 60 61 62 63

Read data by memory map mode from flash...

03020100 07060504 0b0a0908 0f0e0d0c 13121110 17161514 1b1a1918 1f1e1d1c 23222120 27262524 2b2a2928 2f2e2d2c 33323130 37363534 3b3a3938 3f3e3d3c 43424140 47464544 4b4a4948 4f4e4d4c 53525150 57565554 5b5a5958 5f5e5d5c 63626160 ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff ffffffff

Wishbone SPI-Flash demo finished. //main.c(spi_flash_demo)

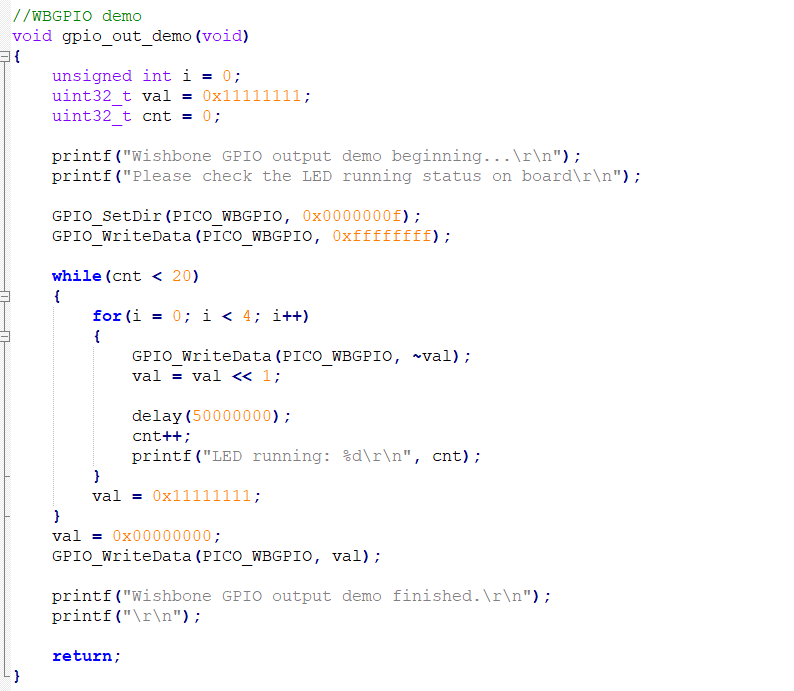

Wishbone GPIO output demo beginning...

Please check the LED running status on board

LED running: 1

LED running: 2

LED running: 3

LED running: 4

LED running: 5

LED running: 6

LED running: 7

LED running: 8

LED running: 9

LED running: 10

LED running: 11

LED running: 12

LED running: 13

LED running: 14

LED running: 15

LED running: 16

LED running: 17

LED running: 18

LED running: 19

LED running: 20

Wishbone GPIO output demo finished.

Wishbone UART rx demo beginning...

Receive a byte from uart rx port当通过串口调试助手给板卡发送任意一个字节的数据时,现象为

-------------------------------------

Running status:

Cycle counter ........: 2045557224

Instruction counter ..: 319375636

CPI: 6.08

------------------------------------- //stats(in firmware)

Enter WBUART RX interrupt...

Receive a byte in WBUART RX interrupt : a

Enter timer interrupt...

Timer interrupt counter : 0

Enter timer interrupt...

Timer interrupt counter : 1

Enter timer interrupt...

Timer interrupt counter : 2

Enter timer interrupt...

Timer interrupt counter : 3

Enter timer interrupt...

Timer interrupt counter : 4

Enter timer interrupt...

Timer interrupt counter : 5

后续不断计数,并且可以测试两个中断的按键,显示如下

Enter timer interrupt...

Timer interrupt counter : 41

Enter timer interrupt...

Timer interrupt counter : 42

Press button 1, enter an external interrupt 20...

Interrupt 20 is triggered by button 1

Enter timer interrupt...

Timer interrupt counter : 43

Enter timer interrupt...

Timer interrupt counter : 44

Enter timer interrupt...

Timer interrupt counter : 45

Enter timer interrupt...

Timer interrupt counter : 46

Enter timer interrupt...

Timer interrupt counter : 47

Enter timer interrupt...

Timer interrupt counter : 48

Enter timer interrupt...

Timer interrupt counter : 49

Enter timer interrupt...

Timer interrupt counter : 50

Press button 2, enter an external interrupt 21...

Interrupt 21 is triggered by button 2

Enter timer interrupt...

Timer interrupt counter : 51

Enter timer interrupt...

Timer interrupt counter : 52

Enter timer interrupt...

Timer interrupt counter : 53

Enter timer interrupt...

Timer interrupt counter : 54

Enter timer interrupt...

Timer interrupt counter : 55

Enter timer interrupt...

Timer interrupt counter : 56

Enter timer interrupt...

Timer interrupt counter : 57

795

795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?