1. Basic

1)Two-step Simulation Process

- compile:

vcs xx.v xx.v - run simulation:

./simv - ※create simulation executable with different name:

vcs xx.v xx.v -o diffname

2)One-step Simulation Process

- 添加指令

-R,例如:vcs xx.v xx.v -R - 存在lib目录,添加指令

+libext+.v,例如vcs xx.v xx.v -y ./lib +libext+.v -R - 文件列表指令

-f,例如vcs -f filelist.f -R

※在testbench中使用$test$plusargs("xxx"),即可在仿真运行命令时添加相应的参数指定条件。

2. VCS UCLI Debugger

vcs -f filelist.f -R -debug_all -ucli. When the UCLI debugger is invoked, you are placed at simulation time 0.- 常用指令

| command | function |

|---|---|

| scope | 查看当前层次的module/切换层次scope u1orscope -up |

| run | 继续运行 |

| get | 获取某信号的值,可添加-radix hex |

| show | 查看某信号的值,单独使用可查看当前module中的值 or show xx -value |

| alias | 赋予变量值,例如alias vars show -value -radix hex a b |

| force | 强制赋予某变量某值 |

| stop | 添加stop条件,例如stop -posedge xx;删除stop条件stop -delete x |

※如果重复使用相关的指令可以使用log文件作为脚本。

3. DVE

- 使用DVE进行debug需要添加

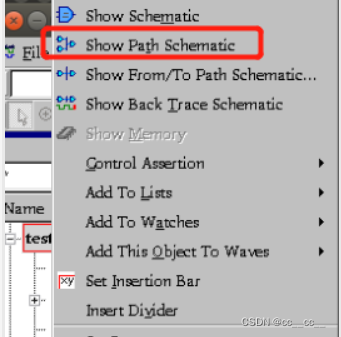

-debug指令且在testbench中需要使用$vcdpluson dve &启动DVE后Open Database,添加相应的信号到波形中。- 右击–Show Path Schematic可以查看相关信号的连接关系,帮助我们定位错误信号的出错位置。

- 可以使用

Annotate Values选项查看信号变化。 Simulator--Setup,可以使用交互模式查看波形变化。Select Signal -> Compare Signals...自动比较两个信号,不同的位置会标红。

欢迎交流,欢迎补充!

1007

1007

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?