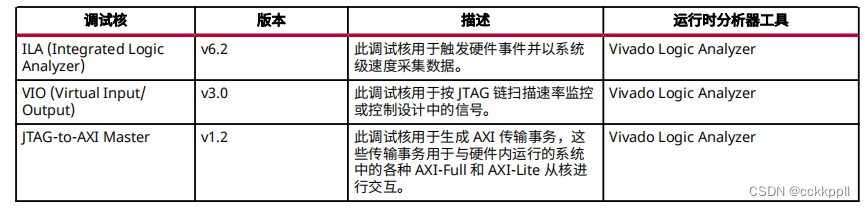

HDL

例化调试探测流程概述

HDL

例化探测流程涉及在

HDL

设计源代码中直接手动自定义、例化和连接各种调试核组件。下表中显示了

Vivado

工具中此流程所支持的新调试核。

新的

ILA

核相比于传统

ILA v1.x

核具有以下

2

大优势

:

• 可搭配集成的

Vivado Logic Analyzer

功能一起使用

(

请参阅“在硬件中调试逻辑设计”

)

。

• 无需

ICON

核实例或连接。

使用

HDL

例化调试探测流程

执行

HDL

例化流程所需的步骤如下

:

1.

自定义并生成

ILA

和

/

或

VIO

调试核

,

其中包含正确数量的探测端口

,

与要探测的信号对应。

2.

(

可选

)

自定义并生成

JTAG-to-AXI Master

调试核

,

并将其连接到设计中的

AXI

外设或互连核的

AXI

从接口。

3.

对包含调试核的设计执行综合。

4.

(

可选

)

修改

Debug Hub

核属性。

5.

对包含调试核的设计执行实现。

自定义和生成调试核

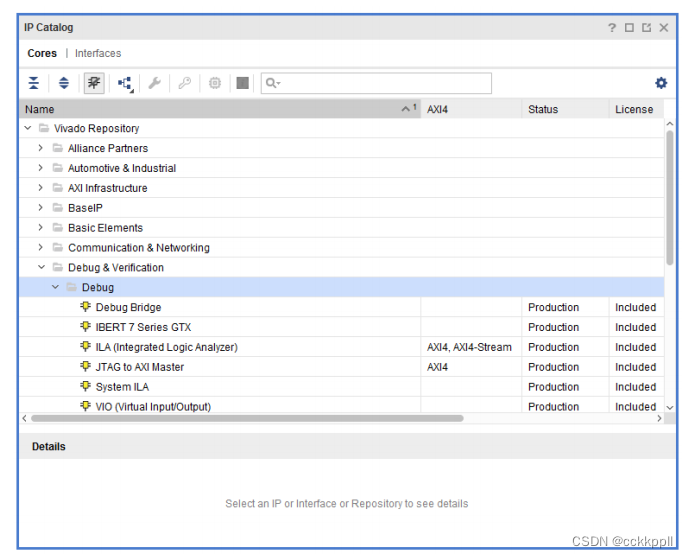

使用“工程管理器

(Project Manager)

”中的“

IP

目录

(IP Catalog)

”按钮来查找、选择和自定义所需调试核。调试核位

于

IP

目录的“调试和验证

(Debug & Verification) >

调试

(Debug)

”类别下

,

请参阅下图。您可双击

IP

核或者右键单击

并选中“自定义

IP (Customize IP)

”菜单选项来自定义调试核。

• 如需了解有关自定义

ILA

核的更多信息

,

请参阅《

Integrated Logic Analyzer LogiCORE IP

产品指南》

(

PG172

)

。

• 如需了解有关自定义

VIO

核的更多信息

,

请参阅《

Virtual Input/Output LogiCORE IP

产品指南》

(

PG159

)

。

• 如需了解有关自定义

JTAG-to-AXI Master

核的更多信息

,

请参阅《

JTAG to AXI Master LogiCORE IP

产品指南》

(

PG174

)

。

自定义核后

,

请单击“

IP

自定义

(IP customization)

”

Wizard

中的“

Generate

”按钮。这样即可生成已自定义的调试

核

,

并将其添加到工程的“源

(Sources)

”视图中。

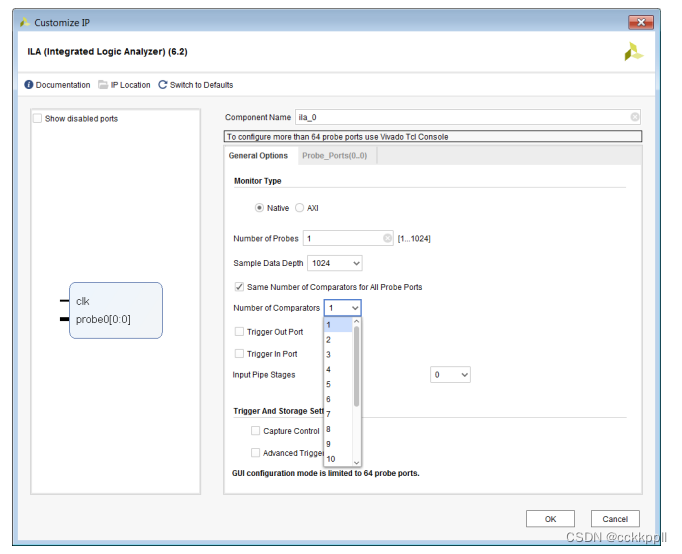

配置所用比较器的数量

在自定义

ILA IP

期间

,

您可设置所用的比较器的数量。允许的范围为

1

至

16

。可为

ILA IP

中的所有探针设置公用比较

器的数量。

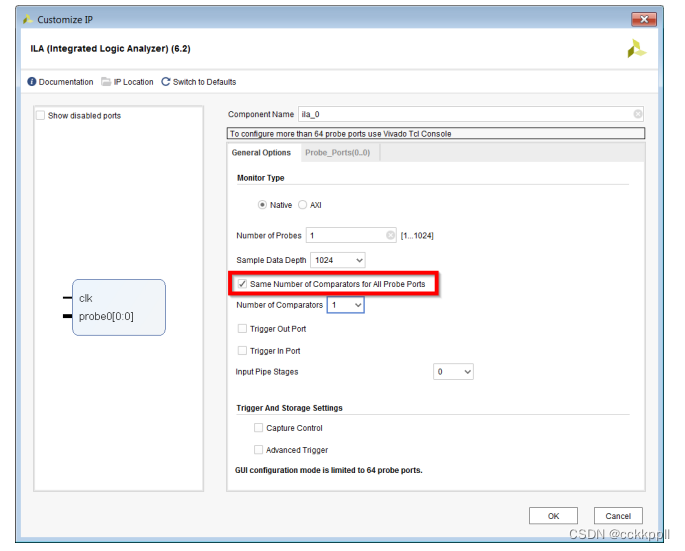

也可以为每个

IP

设置比较器

,

如下所示。任一

ILA

内均可包含多个不同宽度的探针。为此

,

您需要取消勾选“常规选

项

(General Options)

”下的“所有探针端口采用相同数量的比较器

(Same Number of Comparators for All Probe

Ports)

”字段。

随后

,

您即可通过如下方式来为每个探针设置要使用的比较器的准确数量

:

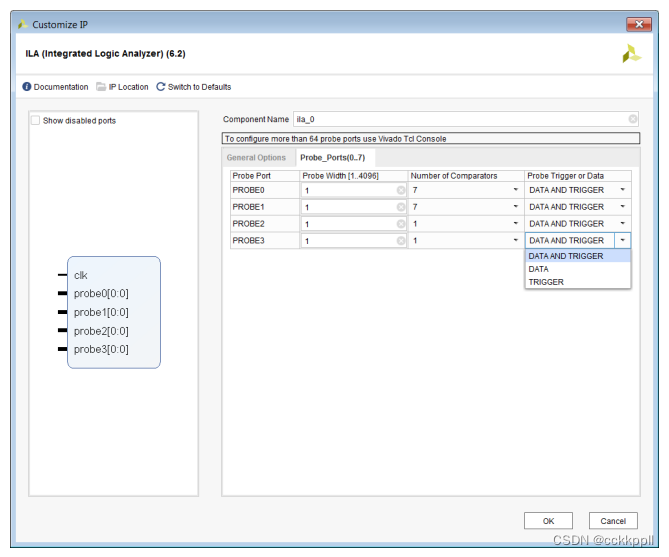

选中“

Probe_Ports

”选项卡并在“比较器

数量

(Number of Comparators)

”字段中设置所期望的比较器数量。

提示

:

如果启用“采集控制

(Capture Control)

”

,

则可选比较器数量范围是

1

到

15

个。有

1

个比较器供采集控

制数据筛选机制使用。

提示

:

根据所选比较器数量

,

该工具会自动重新计算您可在

ILA IP

中使用的探针的数量。每个

ILA

允许的比较

器最大数量为

1024

。

探针作为数据或触发器

在“

ILA IP Configuration

”

Wizard

中

,

可将探针配置为数据和

/

或触发器

,

如下图所示。

如果探针参与触发或采集比较值

,

则应将其配置为仅限“触发器”探针。这样即可最优化

ILA

核使用

BRAM

的方式。

通常

,

如需采集探针数据

,

则应将其配置为仅限“数据”探针。如果探针同时参与触发比较值并且还需采集其数据

,

则

应将其配置为“触发器和数据”。

本文介绍了在Vivado工具中如何通过HDL实例化调试探测流程,包括自定义ILA和VIO核,以及JTAG-to-AXIMaster核。详细讲述了调试核的配置步骤,如设置比较器数量和探针类型,以优化逻辑分析器性能。

本文介绍了在Vivado工具中如何通过HDL实例化调试探测流程,包括自定义ILA和VIO核,以及JTAG-to-AXIMaster核。详细讲述了调试核的配置步骤,如设置比较器数量和探针类型,以优化逻辑分析器性能。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?