问题描述

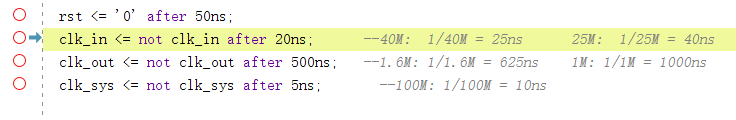

testbench运行一段时间停在箭头指示处

查看波形,有初始值

错误信息:

Failure: ERROR:add_1 must be in range [-1,DEPTH-1]

官方技术人员给出的信息:

这是测试平台的问题,其中在驱动clk信号的过程中,时钟事件在0时间发生,这导致FIR IP中的计数器add_1出现问题。

原因:

我这里是在时钟定义时初始化一个值

signal clk_in : STD_LOGIC := '1';

然后隔20ns取反

clk_in <= not clk_in after 20ns;

他说明的不是很详细,那我们也不用管他IP是怎么写的,直接照下面的改就行了

解决方法:

时钟定义不变,时钟触发改为

process

begin

clk_in = '1';

wait for 20ns;

clk_in = '0';

wait for 20ns;

end process ;

verilog代码可参考

always

begin

#(CLK_PERIOD/2) clk <= ~clk;

end

改为

always

begin

clk = 1'b1;

#(CLK_PERIOD/2) clk = 1'b0;

#(CLK_PERIOD/2);

end

解决方案参考以下网址

参考链接

4216

4216

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?