双十一下午闲来无事,干脆逛逛论坛吧,发现有不少人对于用FPGA实现小数分频不知怎么下手。下面我把自己的源码贴上,大家可以参考一下。

module div_45

(

input sys_clk,

input rst_n,

output clk_45

);

/**********************/

parameter N=9;

/************************/

reg[8:0] temp;

reg temp0,temp4,temp5;

reg[3:0] cnt;

/*********************/

//移位操作

/**********************/

always@(posedge sys_clk)

begin

if(!rst_n)

begin

temp <= 9’b0000_0000_1;

cnt <= ‘d0;

end

else if(cnt>=N-1)

begin

cnt <= ‘d0;

temp <= 9’b0000_0000_1;

end

else

begin

cnt <= cnt + 1’b1;

temp <= temp<<1’b1;

end

end

/*****************************/

//将temp中的第0、4、5位滞后原来90度

/*****************************/

always@(negedge sys_clk)

if(!rst_n)

begin

temp0 <= 1’b0;

temp4 <= 1’b0;

temp5 <= 1’b0;

end

else case(cnt)

‘d0:temp0 <= 1’b1;

‘d4:temp4 <= 1’b1;

‘d5:begin temp4 <= 1’b0;temp5 <= 1’b1 ;end

default:

begin

temp0 <= 1’b0;

temp4 <= 1’b0;

temp5 <= 1’b0;

end

endcase

/****************************/

//输出

/*****************************/

assign clk_45 = (temp[0]|temp0|temp[1])|(temp[5]|temp4|temp5);

endmodule

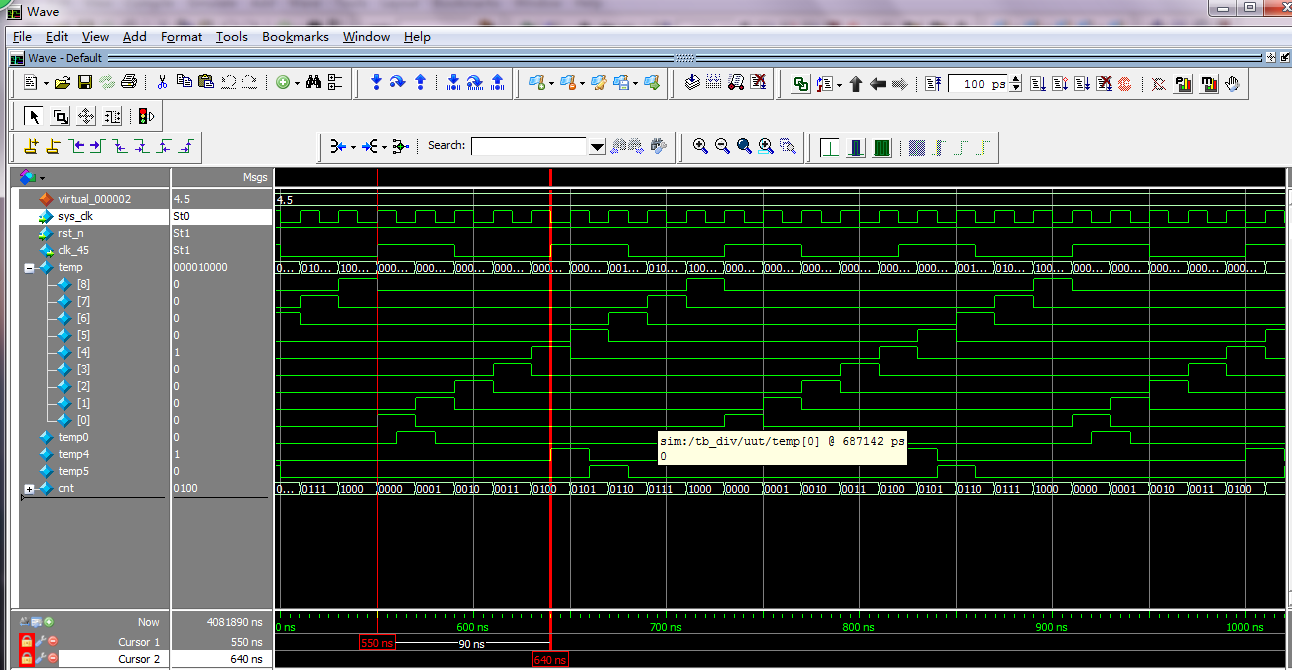

由于是4.5分频,所以此处定义一个9位宽的信号temp。通过左移,使其每一位依次输出高电平。然后将temp中的第0位,第4位,第5位相应的滞后原来temp第0、4、5位90度,即在时钟下降沿变化。最后通过将temp第0、1位和第5位以及滞后90度的temp0、temp4、temp5相或,然后将结果输出,即可实现4.5分频。仿真波形如下:

在实现小数分频时,可考虑这个思路,即将你要分频的数通过计算使其是一个整数,然后通过移位操作,通过分析移位后的波形,来逻辑组合实现相应的分频。

1882

1882

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?