前言

vivado中采用TCL脚本语言来作为其命令解释语言。这句话是很重要的,发散下,bat脚本加tcl就很有用了。

像我这种懒鬼,调试和前期验证阶段,可能需N个demo工程,老眼昏花的时候手动创建工程真是对内心的极大考验。

所以,这种繁琐的可重复的工作当然是使用脚本来完成,达到一劳永逸的效果。

流程

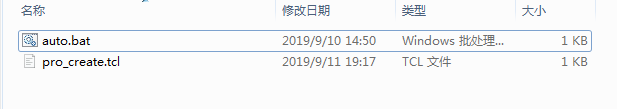

(1)添加这两个文件到任意你想创建工程的文件夹。

(2)解释下此两个文件的含义。

auto.bat的内容如下所示:本质上是去调用tcl文件。同时做了文件夹存在检测判定,避免手残在创建工程后还点击到了auto.bat。

start "C:\Windows\System32\cmd.exe"

@echo Power By Kingstacker.

@echo Produce the vivado project.

set cache_floder=project_1.cache

cd %~dp0

if exist %~dp0%cache_floder% (

echo The floder is exist.

pause

) else (

vivado -source pro_create.tcl

)

exit

tcl脚本如下所示:创建普通工程的tcl如下,注意芯片型号不同的话,需要修改device_mode后面对应的型号。

#设置器件型号

set device_model xc7z035ffg676-2

#设置工程创建位置

set dev_dir [pwd]

#确保切换到了工程位置

cd $dev_dir

puts "The home_dir is $dev_dir now!"

#创建工程

create_project project_1 $dev_dir -part $device_model

#set_property board_part milianke:dev_zynq:part0:1.2 [current_project]

set_property simulator_language Verilog [current_project]

如果是ZYNQ带PS端的工程,脚本如下:如果ddr的型号、MIO bank电压不一样则需修改对应的代码段。

#设置器件型号

set device_model xc7z035ffg676-2

#设置工程创建位置

set dev_dir [pwd]

#确保切换到了工程位置

cd $dev_dir

puts "The home_dir is $dev_dir now!"

#创建工程

create_project project_1 $dev_dir -part $device_model

set_property board_part milianke:dev_zynq:part0:1.2 [current_project]

set_property simulator_language Verilog [current_project]

#创建块设计

create_bd_design "design_1"

update_compile_order -fileset sources_1

startgroup

create_bd_cell -type ip -vlnv xilinx.com:ip:processing_system7:5.5 processing_system7_0

endgroup

startgroup

set_property -dict [list CONFIG.PCW_FPGA0_PERIPHERAL_FREQMHZ {100} CONFIG.PCW_PRESET_BANK1_VOLTAGE {LVCMOS 1.8V} CONFIG.PCW_UIPARAM_DDR_PARTNO {MT41K256M16 RE-125} CONFIG.PCW_UART1_PERIPHERAL_ENABLE {1}] [get_bd_cells processing_system7_0]

endgroup

apply_bd_automation -rule xilinx.com:bd_rule:processing_system7 -config {make_external "FIXED_IO, DDR" Master "Disable" Slave "Disable" } [get_bd_cells processing_system7_0]

connect_bd_net [get_bd_pins processing_system7_0/FCLK_CLK0] [get_bd_pins processing_system7_0/M_AXI_GP0_ACLK]

make_wrapper -files [get_files $dev_dir/project_1.srcs/sources_1/bd/design_1/design_1.bd] -top

#创建壳子

add_files -norecurse $dev_dir/project_1.srcs/sources_1/bd/design_1/hdl/design_1_wrapper.v

update_compile_order -fileset sources_1

update_compile_order -fileset sim_1

(3)双击auto.bat即可。等待脚本的力量吧。

以上。

1104

1104

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?