BGA CHIP PLACEMENT AND ROUTING RULE

BGA是PCB上常用的组件,通常CPU、NORTH BRIDGE、SOUTH BRIDGE、AGP CHIP、CARD BUS CHIP…等,大多是以bga的型式包装,简言之,80﹪的高频信号及特殊信号将会由这类型的package内拉出。因此,如何处理BGA package的走线,对重要信号会有很大的影响。

通常环绕在BGA附近的小零件,依重要性为优先级可分为几类:

1. by pass。

2. clock终端RC电路。

3. damping(以串接电阻、排组型式出现;例如memory BUS信号)

4. EMI RC电路(以dampin、C、pull height型式出现;例如USB信号)。

5. 其它特殊电路(依不同的CHIP所加的特殊电路;例如CPU的感温电路)。

6. 40mil以下小电源电路组(以C、L、R等型式出现;此种电路常出现在AGP CHIP or含AGP功能之CHIP附近,透过R、L分隔出不同的电源组)。

7. pull low R、C。

8. 一般小电路组(以R、C、Q、U等型式出现;无走线要求)。

9. pull height R、RP。

1-6项的电路通常是placement的重点,会排的尽量靠近BGA,是需要特别处理的。第7项电路的重要性次之,但也会排的比较靠近BGA。8、9项为一般性的电路,是属于接上既可的信号。

相对于上述BGA附近的小零件重要性的优先级来说,在ROUTING上的需求如下:

1. by pass => 与CHIP同一面时,直接由CHIP pin接至by pass,再由by pass拉出打via接plane;与CHIP不同面时,可与BGA的VCC、GND pin共享同一个via,线长请勿超越100mil。

2. clock终端RC电路 => 有线宽、线距、线长或包GND等需求;走线尽量短,平顺,尽量不跨越VCC分隔线。

3. damping => 有线宽、线距、线长及分组走线等需求;走线尽量短,平顺,一组一组走线,不可参杂其它信号。

4. EMI RC电路 => 有线宽、线距、并行走线、包GND等需求;依客户要求完成。

5. 其它特殊电路 => 有线宽、包GND或走线净空等需求;依客户要求完成。

6. 40mil以下小电源电路组 => 有线宽等需求;尽量以表面层完成,将内层空间完整保留给信号线使用,并尽量避免电源信号在BGA区上下穿层,造成不必要的干扰。

7. pull low R、C => 无特殊要求;走线平顺。

8. 一般小电路组 => 无特殊要求;走线平顺。

9. pull height R、RP => 无特殊要求;走线平顺。

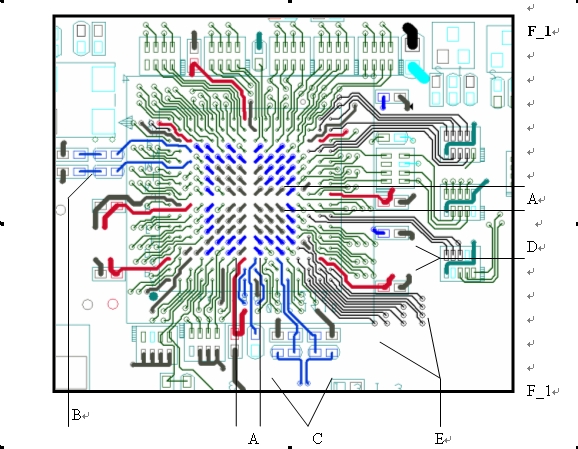

为了更清楚的说明BGA零件走线的处理,将以一系列图标说明如下:

A. 将BGA由中心以十字划分,VIA分别朝左上、左下、右上、右下方向打;十字可因走线需要做不对称调整。

B. clock信号有线宽、线距要求,当其R、C电路与CHIP同一面时请尽量以上图方式处理。

C. USB信号在R、C两端请完全并行走线。

D. by pass尽量由CHIP pin接至by pass再进入plane。无法接到的by pass请就近下plane。

E. BGA组件的信号,外三圈往外拉,并保持原设定线宽、线距;VIA可在零件实体及3MM placement禁置区间调整走线顺序,如果走线没有层面要求,则可以延长而不做限制。内圈往内拉或VIA打在PIN与PIN正中间。另外,BGA的四个角落请尽量以表面层拉出,以减少角落的VIA数。

F. BGA组件的信号,尽量以辐射型态向外拉出;避免在内部回转。

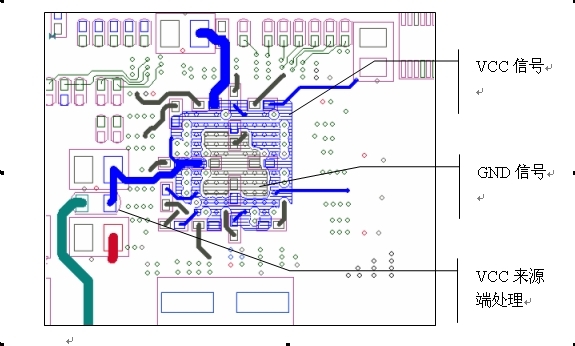

F_2 为BGA背面by pass的放置及走线处理。

By pass尽量靠近电源pin。

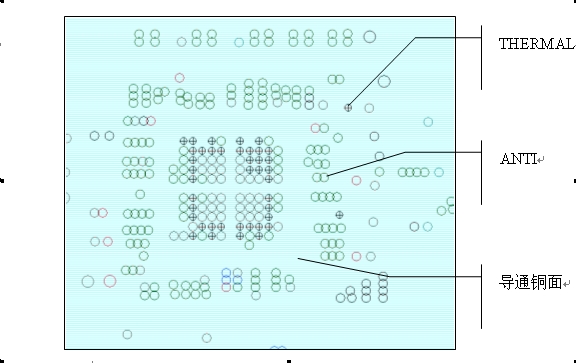

F_3 为BGA区的VIA在VCC层所造成的状况

THERMAL VCC信号在VCC层的导通状态。

ANTI GND信号在VCC层的隔开状态。

因BGA的信号有规则性的引线、打VIA,使得电源的导通较充足。

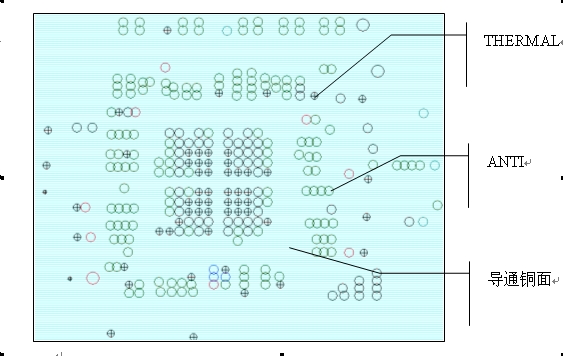

F_4 为BGA区的VIA在GND层所造成的状况

THERMAL GND信号在GND层的导通状态。

ANTI VCC信号在GND层的隔开状态。

因BGA的信号有规则性的引线、打VIA,使得接地的导通较充足。

F_5 为BGA区的Placement及走线建议图

以上所做的BGA走线建议,其作用在于:

1. 有规则的引线有益于特殊信号的处理,使得除表层外,其余走线层皆可以所要求的线宽、线距完成。

2. BGA内部的VCC、GND会因此而有较佳的导通性。

3. BGA中心的十字划分线可用于;当BGA内部电源一种以上且不易于VCC层切割时,可于走线层处理(40~80MIL),至电源供应端。或BGA本身的CLOCK、或其它有较大线宽、线距信号顺向走线。

4. 良好的BGA走线及placement,可使BGA自身信号的干扰降至最低。

5619

5619

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?