一、CD4518简介:

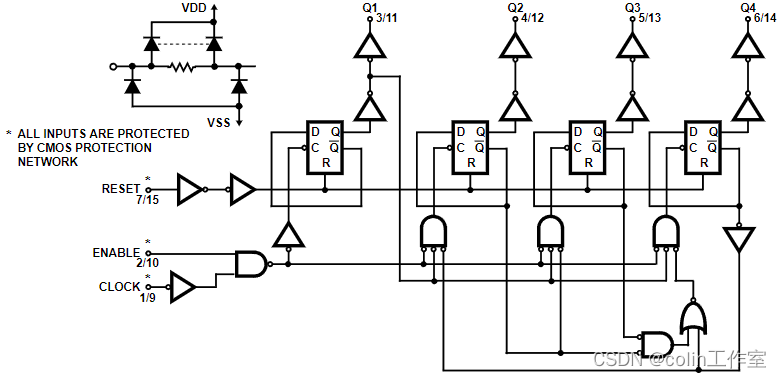

CD4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器。每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

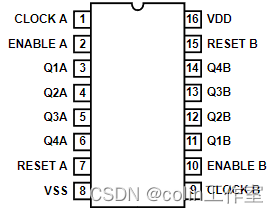

二、CD4518引脚定义:

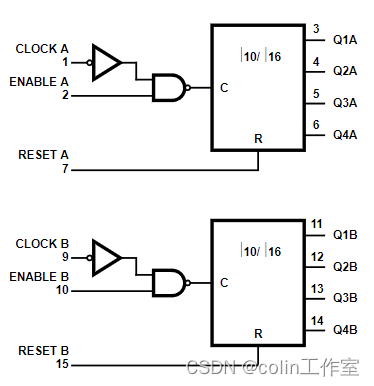

三、CD4518功能框图:

四、CD4518逻辑框图:

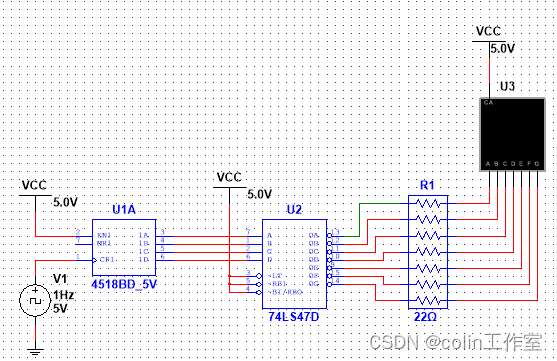

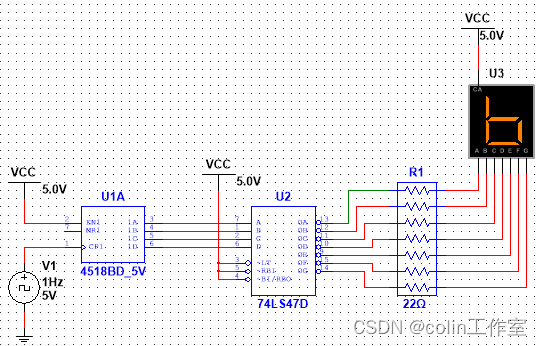

五、仿真原理图:

六、运行仿真:

该博客介绍了如何使用CD4518二、十进制同步加计数器进行电路设计,详细阐述了CD4518的特点、引脚定义、功能及逻辑框图,并提供了仿真原理图和运行仿真的步骤,为FPGA开发中的计数器设计提供参考。

该博客介绍了如何使用CD4518二、十进制同步加计数器进行电路设计,详细阐述了CD4518的特点、引脚定义、功能及逻辑框图,并提供了仿真原理图和运行仿真的步骤,为FPGA开发中的计数器设计提供参考。

1694

1694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?