系统主要操作码用于对RISC-V ISA中所有特权指令进行编码。主要被分为两类原子read-modify-write控制和状态寄存器(CSRs), 被定义在Z扩展中。

标准CSRs对于读没有副作用,但是可能对于写可能有影响。

1.CSR地址映射的约定

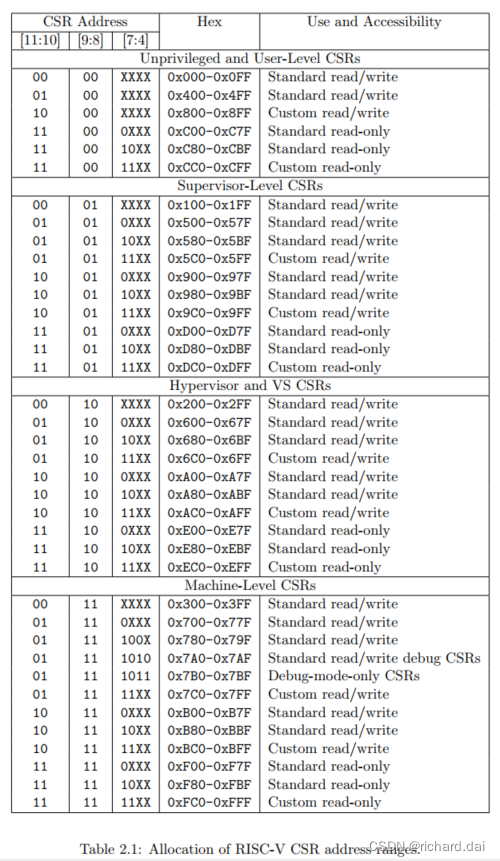

标准RISC-V ISA为多达4,096个csr留出12位编码空间(csr[11:0])。按照约定,CSR地址的前4位(CSR[11:8])根据权限级别对CSR的读写可访问性进行编码,最上面的两位(csr[11:10])表示寄存器是读/写(00、01或10)还是只读(11)。接下来的两位(csr[9:8])编码可以访问csr的最低特权级别。

2. CSR Listing

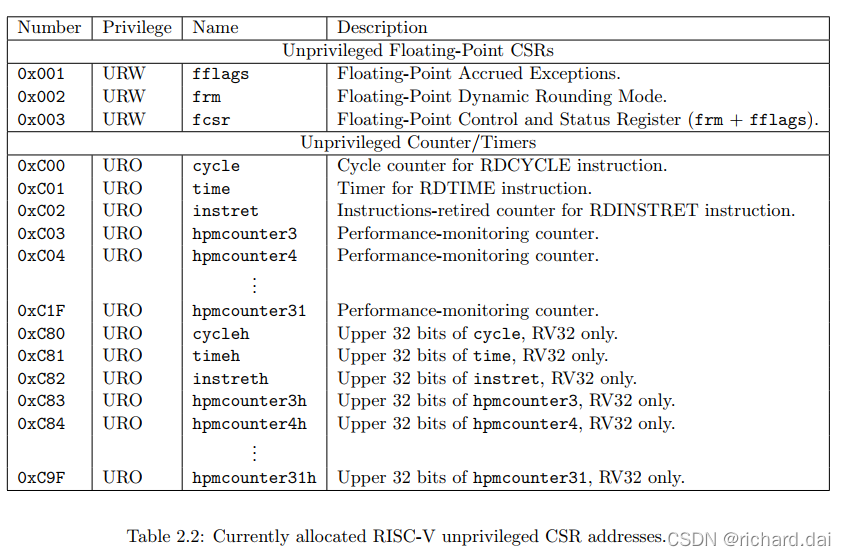

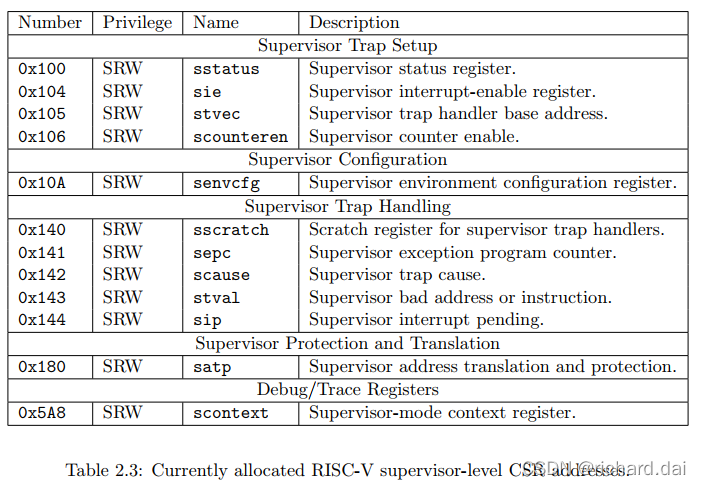

本文深入探讨RISC-V的控制和状态寄存器(CSRs),包括地址映射规则、CSR列表、域规格、隐含读取以及宽度调整。介绍了CSR在读写操作中的行为,如WPRI、WLRL和WARL字段的特性,以及CSR宽度变化时的处理方式。

本文深入探讨RISC-V的控制和状态寄存器(CSRs),包括地址映射规则、CSR列表、域规格、隐含读取以及宽度调整。介绍了CSR在读写操作中的行为,如WPRI、WLRL和WARL字段的特性,以及CSR宽度变化时的处理方式。

订阅专栏 解锁全文

订阅专栏 解锁全文

992

992

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?