介绍

系统主操作码(SYSTEM:11100 11)用于编码RISC-V ISA中的所有特权指令。它们可以分为两个主要类:原子读修改-写控制和状态寄存器(csr),它们在Zicsr扩展中定义,以及所有其他特权指令。特权体系结构需要Zicsr扩展;需要哪些其他特权指令取决于特权体系结构特性集。

除了本手册第一卷中描述的非特权状态外,实现还可能包含额外的CSR,可以使用第一卷中描述的CSR说明访问特权级别的某些子集访问。在本章中,我们绘制出CSR地址空间。下面的章节描述了每个csr根据特权级别的功能,以及通常与特定特权级别密切相关的其他特权指令。请注意,尽管csr和指令与一个特权级别相关联,但它们也可以在所有更高的特权级别上访问。

控制状态寄存器是用于控制和管理处理器或系统行为的寄存器。在读取控制状态寄存器的值时,不会对处理器或系统的状态产生任何影响或改变。读操作只是获取寄存器当前的值,并不会对其他部分产生任何影响。

然而,当对控制状态寄存器进行写入操作时,可能会引起副作用。这意味着写入操作可能会改变处理器或系统的状态,影响其后续的行为或操作。这些副作用可能包括修改寄存器的值、改变处理器的工作模式、触发中断或操作其他相关的硬件或软件组件。

因此,在使用控制状态寄存器进行编程或操作时,必须注意写入操作可能会引起的副作用,并谨慎处理寄存器的写入操作,以确保不会对系统产生意外或不受控制的影响。

1 CSR地址映射规定

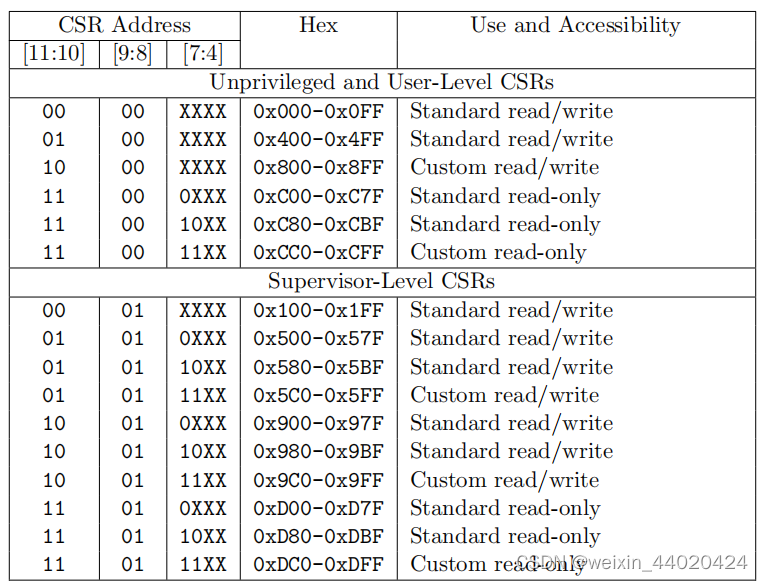

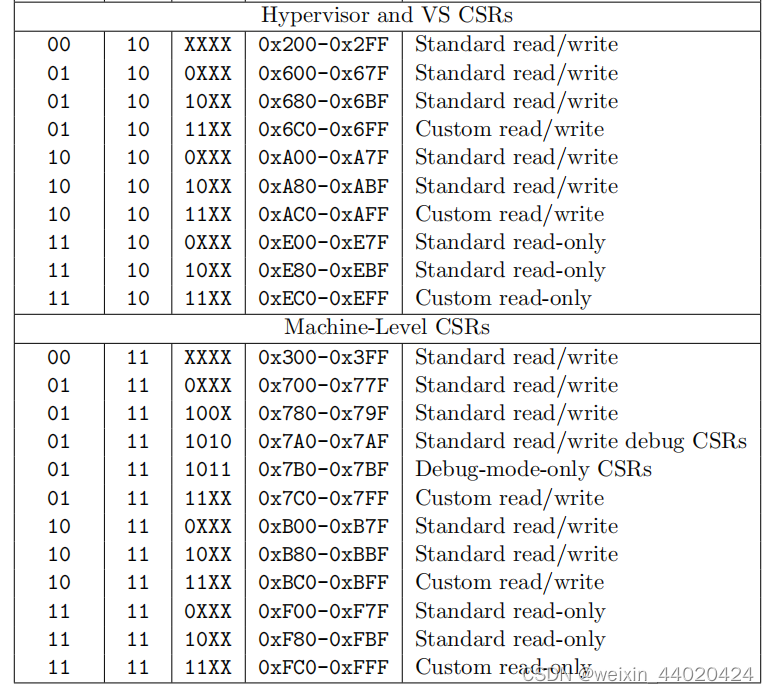

标准的RISC-V ISA为多达4096个csr留出了一个12位的编码空间(csr[11:0])。按照惯例,使用CSR地址的上4位(csr[11:8])根据特权级别对CSR的读写可访问性进行编码,如表2.1所示。前两位(csr[11:10])表示寄存器是读/写(00、01或10)还是只读(11)。接下来的两位(csr[9:8])编码可以访问CSR的最低特权级别。

CSR地址约定使用CSR地址的上限来对默认的访问权限进行编码。这简化了硬件中的错误检查,并提供了一个更大的CSR空间,但确实限制了CSR到地址空间的映射。

实现可能允许更有特权的级别捕获较低特权级别允许的CSR访问,从而允许拦截这些访问。这种变化对于特权不佳的软件应该是透明的。

试图访问不存在的CSR会引发非法指令异常( illegal instruction exception)。尝试访问没有适当权限级别的CSR或写入只读寄存器也会引发非法的指令异常(illegal instruction exception)。读/写寄存器还可能包含一些只读的位,在这种情况下,写入的只读位将被忽略。

表2.1还指出了在标准使用和自定义使用之间分配CSR地址的约定。指定为自定义使用的CSR地址将不会被未来的标准扩展重新定义。

机器模式标准读写csr 0x7A0-0x7BF预留供调试系统使用。在这些csr中,0x7A0-0x7AF可在机器模式下访问,而0x7B0-0x7BF仅在调试模式下可见。实现应该在对后一组寄存器的机器模式访问时引发非法的指令异常。

2 CSR 列表

表2.2-2.6列出了当前已分配的CSR地址的CSR。计时器、计数器和浮点csr都是标准的无特权csr。其他寄存器由特权代码使用,如下章所述。请注意,并非在所有实现上都需要所有的寄存器。

Standard是标准,在未来可能被使用。但是Custom是用户自定义,在未来不会被扩展。如何用户希望自定义使用CSR寄存器可以使用Custom自定义用途。

hex指定范围,每组寄存器有不同的用途。standard寄存器有一部分已经使用,需要查看手册中已经分配的寄存器,了解特权读写,用途,规范。

2.1 特权级别

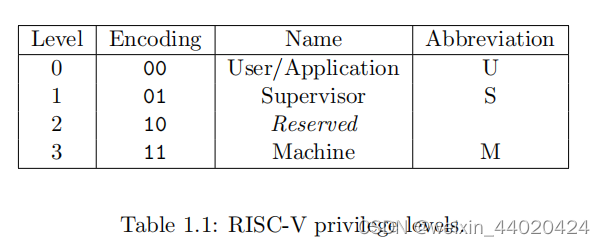

在任何时候,RISC-V硬件线程(hart)都在某种特权级别编码为一个或多个csr(控制和状态寄存器)。目前定义了三个RISC-V特权级别,如表1.1所示。

特权级别用于在软件堆栈的不同组件之间提供保护,并且尝试执行当前特权模式不允许的操作将导致一个异常。这些异常通常会导致陷阱进入底层执行环境。

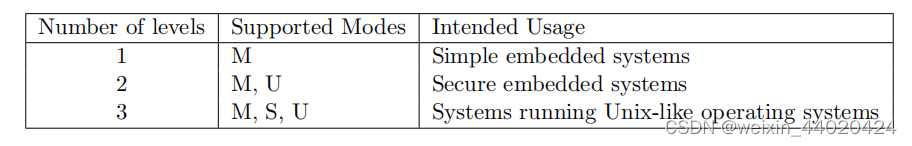

机器级别具有最高的权限,并且是RISC-V硬件平台的唯一强制性权限级别。在机器模式(m模式)中运行的代码通常天生就是受信任的,因为它有对机器实现的低级访问权限。M模式可用于管理RISC-V上的安全执行环境。用户模式(U模式)和监督模式(S模式)分别用于传统应用程序和操作系统的使用。

每个特权级别都有一组具有可选扩展和变体的核心特权ISA扩展。例如,机器模式支持一个可选的内存保护标准扩展。此外,管理程序模式也可以扩展到支持第9章中所述的第2类管理程序的执行。

在M级别上,运行普通的嵌入式系统

在M、U级别上,运行安全的嵌入式系统

在M、S、U级别上,运行类Unix操作系统

hart通常在u型模式下运行应用程序代码,直到某些陷阱(例如,主管调用或计时器中断)强制切换到陷阱处理程序,该处理程序通常在更特权的模式下运行。然后,hart将执行陷阱处理程序,最终将在u模式的原始捕获指令或之后恢复执行。增加特权级别的陷阱被称为垂直陷阱,而保持在同一特权级别上的陷阱被称为水平陷阱。RISC-V特权体系结构提供了灵活的陷阱到不同特权层的路由。

H级别是一个超级监管者。这个参考这幅图。在H层级上可以运行不同的OS,每个OS管理不同的APP。(虚拟机)

实现还可以包括支持芯片外调试和/或制造测试的调试模式。调试模式(d模式)可以被认为是一种额外的特权模式,甚至比m模式有更多的访问权限。单独的调试规范建议描述了调试模式下RISC-V哈的操作。调试模式保留了一些只有在d模式下才能访问的CSR地址,也可以保留平台上的部分物理地址空间。

2.2 已经分配的CSR地址

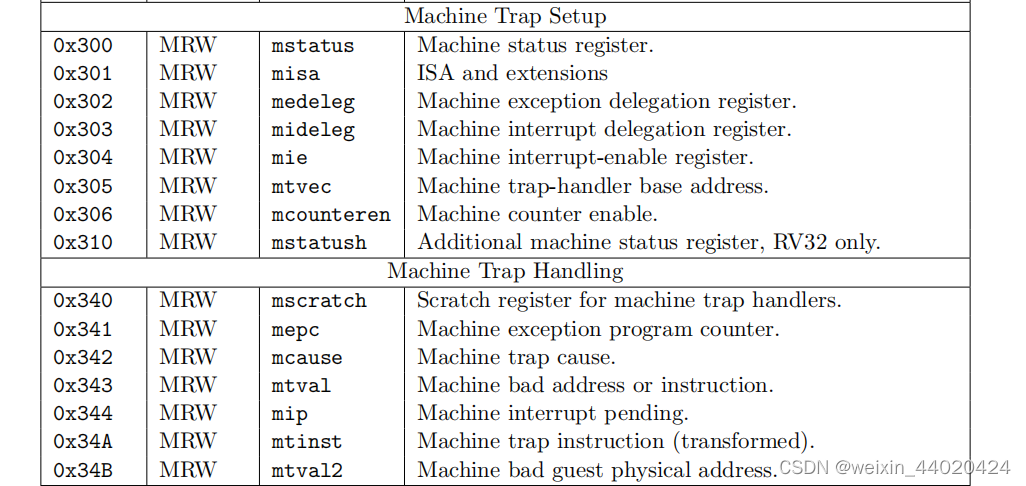

已经分配的CSR地址,很多可以根据需要有选择的支持,这里只展示关于机器级别的Trap寄存器

Number:csr地址。

Privilege:特权级别(D,M,H,S,U) 读写属性(RW,RO)

Name:寄存器的名称。

Description:寄存器的用途。

这里简单介绍了每个寄存器,详细信息需要查看手册内容。

2.3 CSR的字段规范

以下定义和缩写用于指定csr内字段的行为。

Reserved Writes Preserve Values, Reads Ignore Values (WPRI)

这个字段被保留到未来使用,软件应该忽略从这些字段读取的值,写数据时应该保留这些值,不要覆盖。

硬件:如果不提供这些字段的实现必须,只读为0

软件:读:忽略,写:保留(不覆盖)

硬件:读:只读为0,写:拒绝

一些完整的读写字段供将来使用。软件应该忽略从这些字段中读取的值,并且在将值写入同一寄存器的其他字段时,应该保留这些字段中保存的值。为了实现前向兼容性,不提供这些字段的实现必须使它们为只读零。这些字段在寄存器描述中被标记为WPRI。

Write/Read Only Legal Values (WLRL)

限定合法位编码子集,只能写入合法数据。写入不合法数据,不需要trap,但是需要能够返回最后一次的合法数据。

一些读/写CSR字段只指定了可能的位编码的一个子集的行为,并保留了其他的位编码。软件不应写入除合法值以外的任何值,也不应假设读取将返回合法值,除非最后一次写入是合法值,或者由于另一个操作(例如,重置)将寄存器设置为合法值而没有写入寄存器值。这些字段在寄存器描述中被标记为WLRL。

如果指令试图将不受支持的值写入WLRL字段,则允许但不需要实现引发非法指令异常。当最后一次写入是非法值时,实现可以在WLRL字段的读取时返回任意位模式,但是返回的值应该确定地取决于非法写入值和写入之前字段的值。

Write Any Values, Reads Legal Values (WARL)

一些读/写CSR字段仅为位编码的子集定义,但允许写入任何值,同时保证在读取时返回合法值。假设编写CSR没有其他副作用,可以通过尝试编写所需的设置,然后读取是否保留该值来确定支持的值的范围。这些字段在寄存器描述中被标记为WARL。

实现不会在写入不支持的WARL字段的值时引发异常。当最后一次写入是非法值时,实现可以对WARL字段的读取返回任何合法值,但是返回的合法值应该确定地取决于非法写入值和hart的架构状态。

其他特性请查看riscv 特权级手册。

3 Machine-Level ISA

3.1 Machine Trap-Vector Base-Address Register (mtvec)

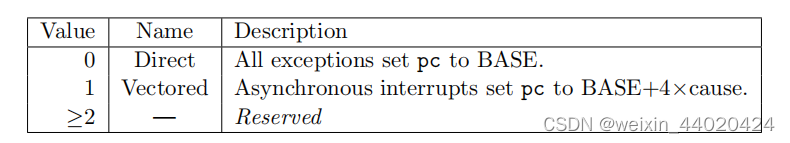

mtvec寄存器是一个MXLEN位WARL读/写寄存器,它持有陷阱向量配置,由一个向量基地址(BASE)和一个向量模式(MODE)组成。

mtvec寄存器必须始终被实现,但可以包含一个只读值。如果mtvec是可写的,则寄存器可能持有的值集可以因实现而有所不同。BASE字段中的值必须始终在4字节的边界上对齐,并且MODE设置可能会对BASE字段中的值施加额外的对齐约束。

MODE字段的编码如表3.5所示。当MODE=Direct时,所有陷阱进入机器模式会导致pc被设置为基本字段中的地址。当MODE=矢量时,所有在机器模式中的同步异常导致pc设置为BASE字段中的地址,而中断导致pc设置为BASE字段中的地址加上中断原因数的四倍。例如,一个机器模式的定时器中断(见第39页的表3.6)会导致pc被设置为BASE+0x1c

3.2 Machine Exception Program Counter (mepc)

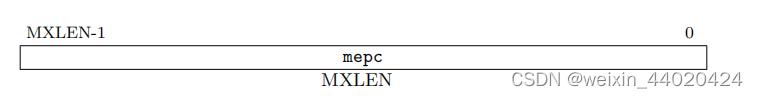

mepc是一个MXLEN位的读/写寄存器,其格式如图3.21所示。mepc(mepc[0])的低位始终为零。在仅支持IALIGN=32的实现中,两个低位(mepc[1:0])始终为零。

如果一个实现允许IALIGN是16或32(例如,通过改变CSRmisa),那么,每当IALIGN=32时,位mepc[1]在读取时被屏蔽,使它看起来是0。这种屏蔽也发生在MRET指令的隐式读取中。虽然被屏蔽了,但mepc[1]在IALIGN=32时仍然可写。

mepc是一个WARL寄存器,它必须能够保存所有有效的虚拟地址。它不需要能够保存所有可能的无效地址。在编写mepc之前,实现可能会将一个无效的地址转换为mepc能够保存的一些其他无效的地址。

当一个陷阱被带到m模式时,mepc将被写入被中断或遇到异常的指令的虚拟地址。否则,mepc永远不会由软件编写,尽管它可能由软件显式编写。

3.3 Machine Cause Register (mcause)

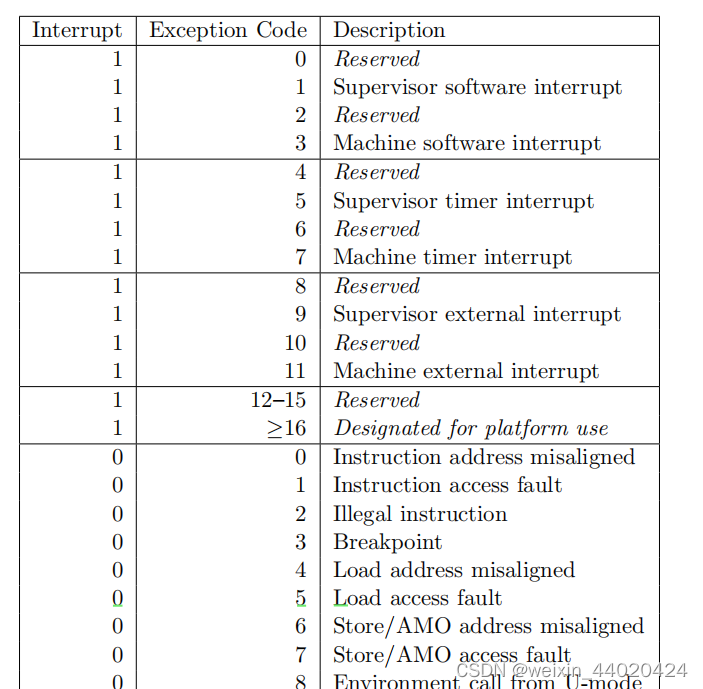

mmase寄存器是一个MXLEN位读写寄存器格式,如图3.22所示。当陷阱进入m模式时,mmase会用代码指示导致陷阱的事件。否则,mmause永远不会由实现编写,尽管它可能由软件显式编写

如果陷阱是由中断引起的,则设置原因寄存器中的中断位。异常代码字段包含一个标识最后一个异常或中断的代码。表3.6列出了可能的机器级异常代码。异常代码是一个WLRL字段,因此只保证保存受支持的异常代码。

请注意,加载和负载保留指令生成负载异常,而存储指令、存储条件指令和AMO指令生成存储/AMO异常。

如果一条指令可能引发多个同步异常,表3.7的优先级顺序降低表示在mmause中采取并报告了哪个异常。任何自定义同步异常的优先级都是由实现定义的。

4556

4556

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?