上文说了远程升级的核心点,这次说一下这个涉及的一个流程涉及和实现思路。

1.模块设计

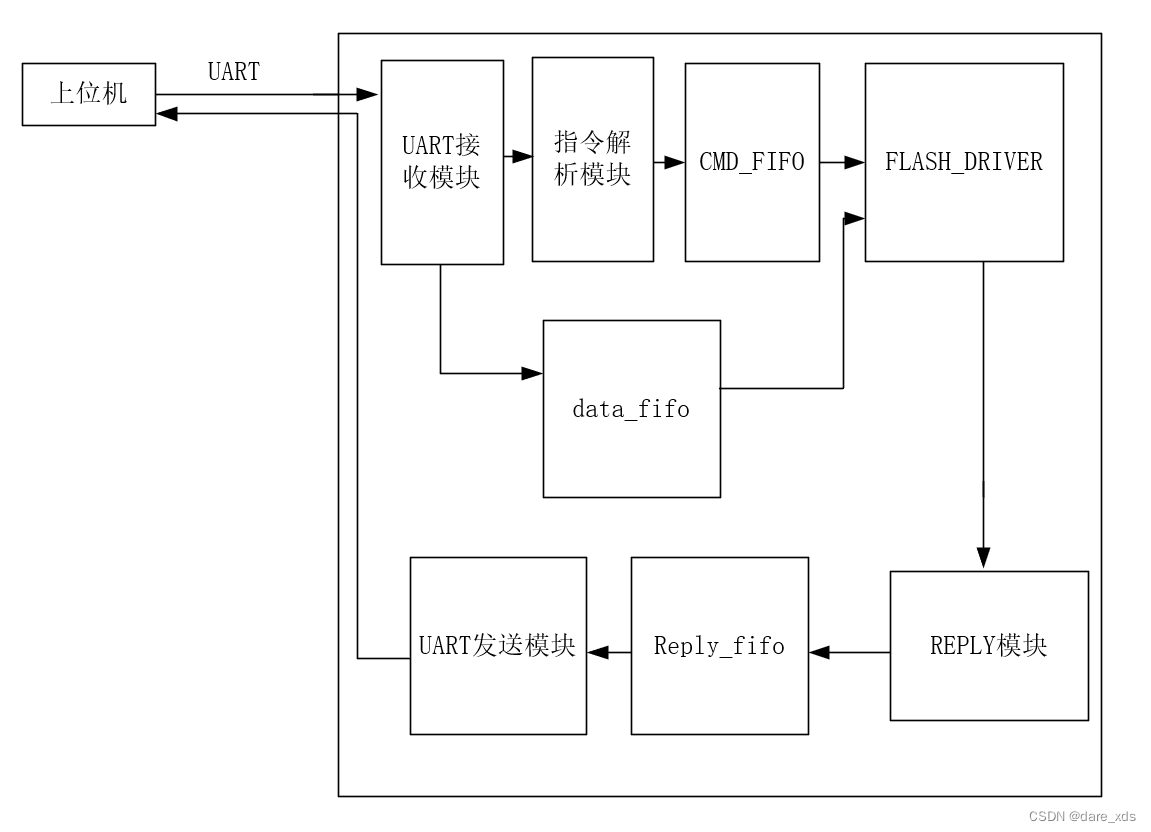

看图说话吧,一个一个介绍:

看图说话吧,一个一个介绍:

上位机:发送指令和升级数据(bin文件或者mcs文件),接收回复的指令和flash的读出的数据。

UART接收模块:接收上位机传过来的数据,分发到指令解析模块和data_fifo。

指令解析模块:解析指令,将对应的控制信号存入fifo,等待falsh_driver来取。最重要的作用是跨时钟域处理。

flash_driver:核心,控制读写flash,以及对应的指令回复。

data_fifo:缓存升级数据以及跨时钟域处理。

reply模块:对指令回复进行缓存和跨时钟域处理。

UART发送模块:发送回复指令以及从flash读出的数据。

2.踩坑推荐

系统还是比较简单的:不过还是有些地方需要特别注意。

1.就是使用的3个FIFO,都是异步FIFO。最主要的功能就是跨时钟域处理,在进行配置的时候需要注意读写时钟的配置。在CMD_FIFO 和DATA_FIFO中,写时钟都是系统时钟(我这里是50M),读时钟是SPI的时钟域(10M).。在REPLY_FIFO里,是反过来的。

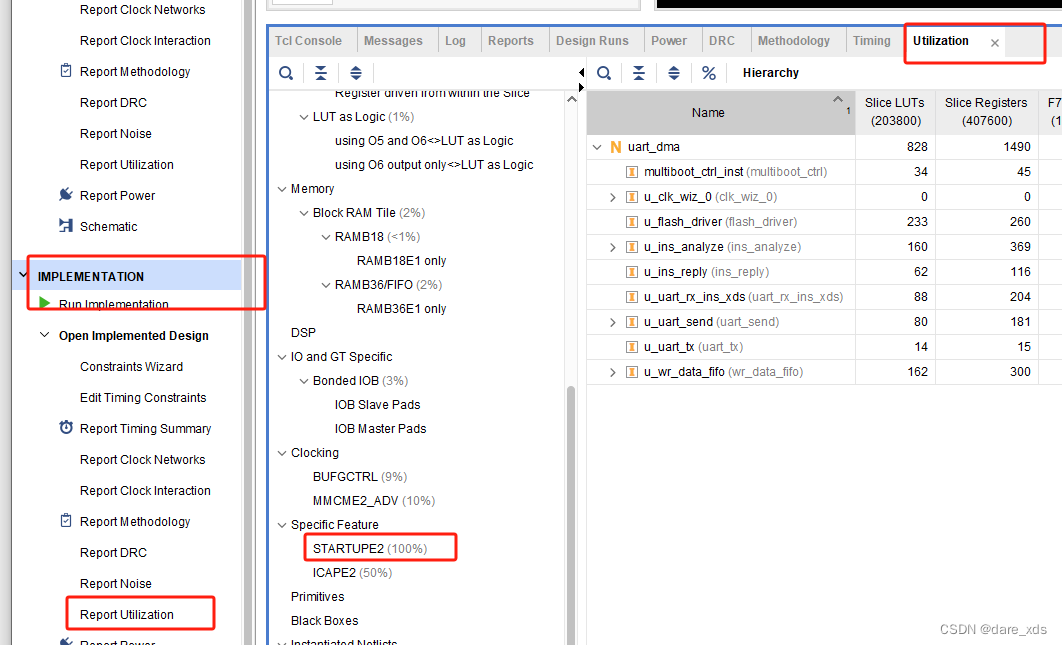

2.在使用STARTUPE2原语的时候,怎么看使用成功没?两种方法

a.在vivado中看使用率:

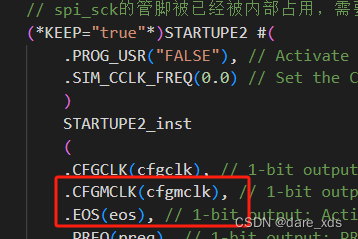

b.将原语的输出,用引脚引出去,然后使用ILA或者示波器看下信号。

CFFMCLK是一个内部的65M时钟,可以分频然后打出来看下。有没有这个输出时钟

3.时钟约束

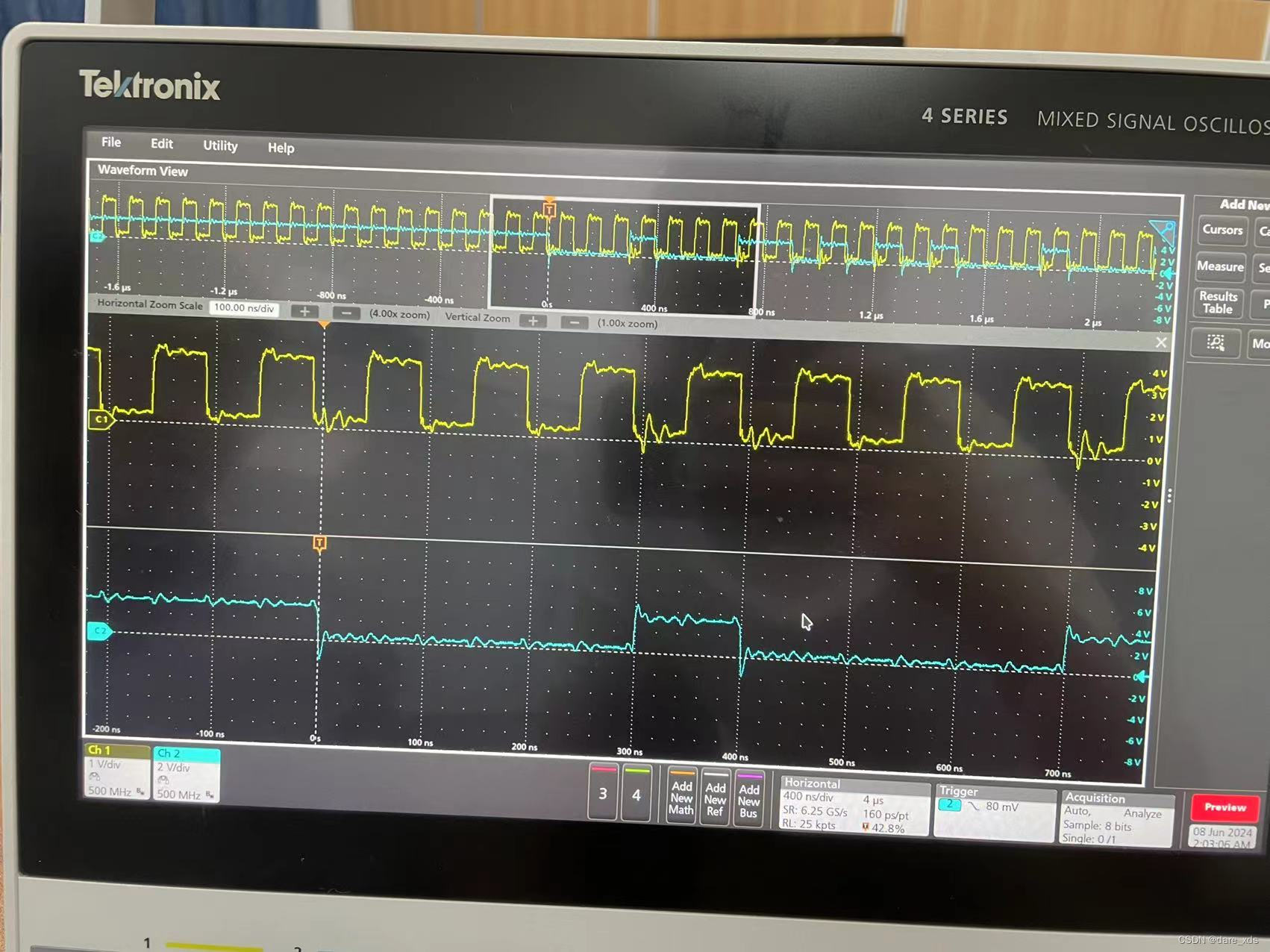

由于是操作板子上的flash,由于硬件设计的不同。可能对于sck的输出要求不一样,这个也需要根据实际情况去调试。推荐方法是示波器直接打 SPI的相关信号,看下信号是否对齐。

比如:

4.在生成bin文件的时候,有时候会面临文件过大的情况。因为指令中包含传输长度,我的设计是3个字节,如果超过可以使用压缩指令,对生成的文件进行压缩,有两种方案:

a.在xdc文件中加入下列语句

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

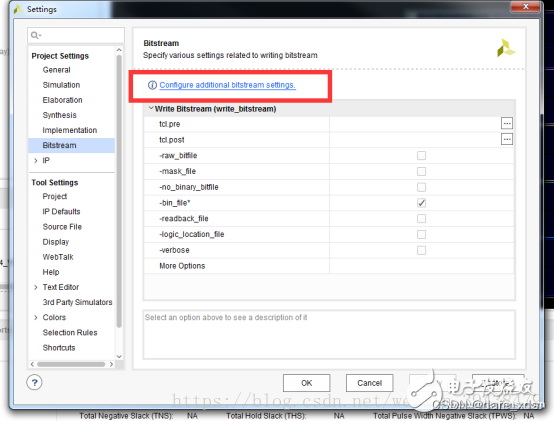

b.在setting中进行配置

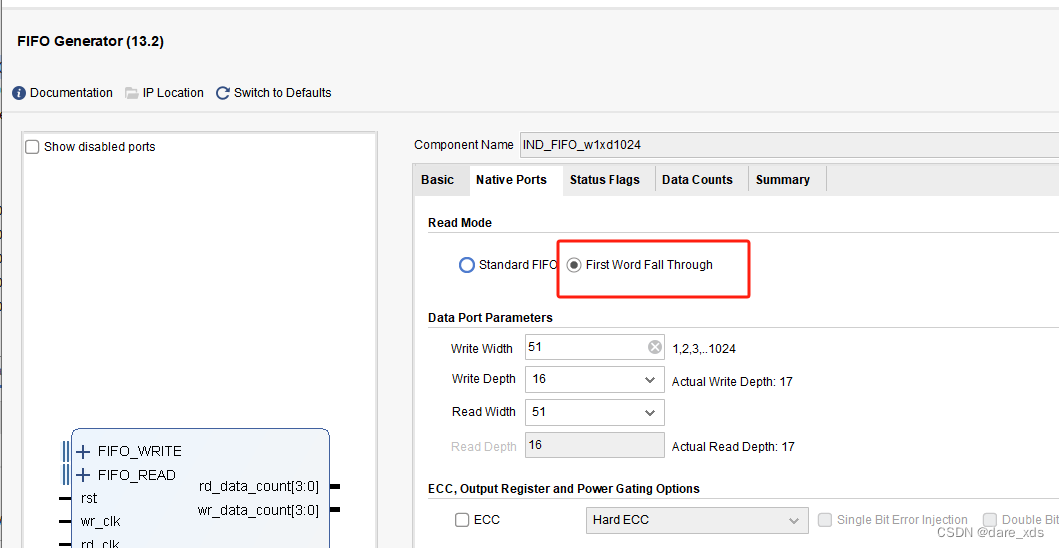

5.FIFO选择FWFT的模式,FIFO会事先准备好一个数据。并且这时候就算没有数据写入,也会返回一个00.rd_data_count为1,如果要用rd_data_count作为判断条件。那么就要选择标准FIFO,这样就是如果没有数据写入的时候,ra_data_count从0开始。

更多嵌入式,FPGA资料可参考:天津大学四川院FPGA培训中心 -- www.sxfpga.cn

3499

3499

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?