September 21, 2016

作者:dengshuai_super

出处:http://blog.csdn.net/dengshuai_super/article/details/52571372

声明:转载请注明作者及出处。

同步有限状态机的设计

1. 什么是有限状态机(FSM)

在FPGA里面做有限状态机的原因:因为FPGA都是并行处理的,想要做一些有前后顺序的事件处理的时候,我们就引入这种状态的机制。因此状态机在FPGA里面应用这么广。

在软件里面也是有状态机的思想,但是软件它是一个顺序执行的方法,所以状态机的存在显得不是那么重要了。

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路;

其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态;

究竟转向哪一状态不但取决于各个输入值,还取决于当前状态。

状态机可用于产生在时钟跳变沿时刻开关的复杂的控制逻辑,是数字逻辑的控制核心。

2. FSM的种类和不同点

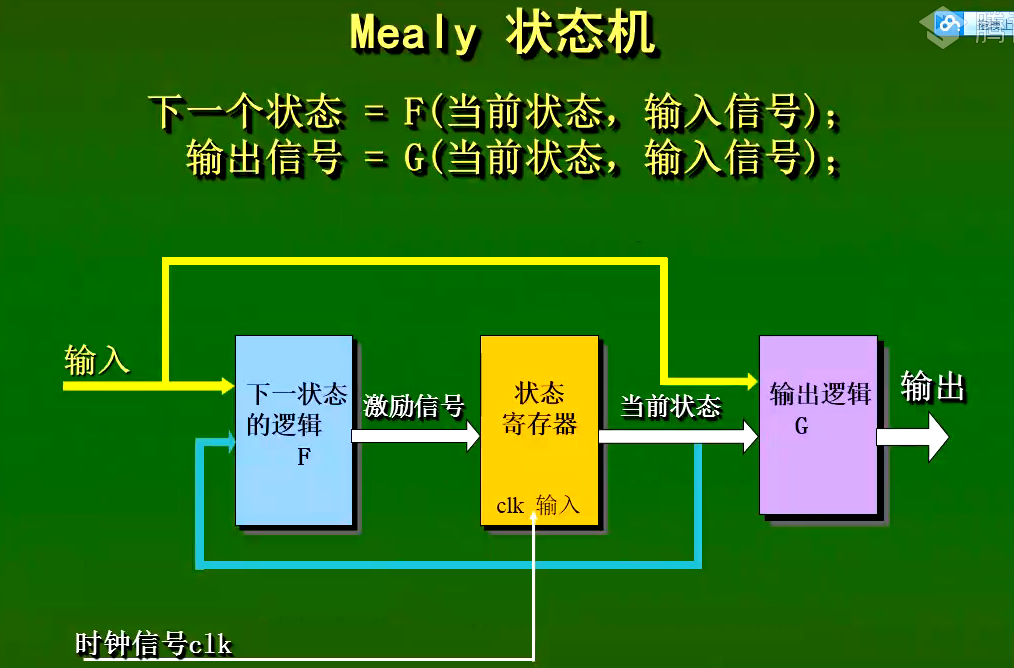

Mealy状态机:

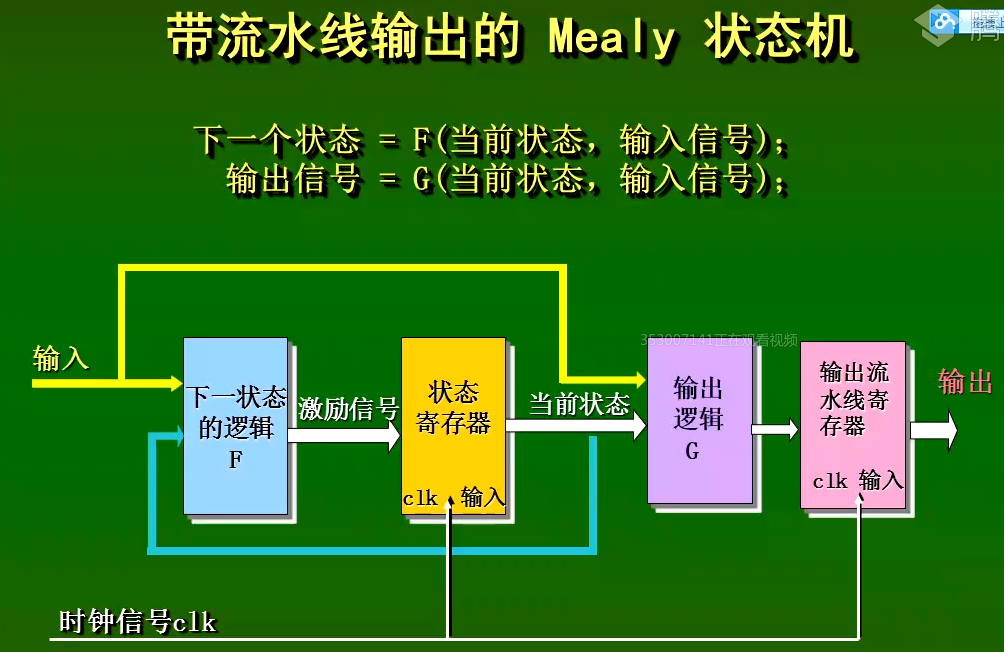

带流水线输出的Mealy状态机:

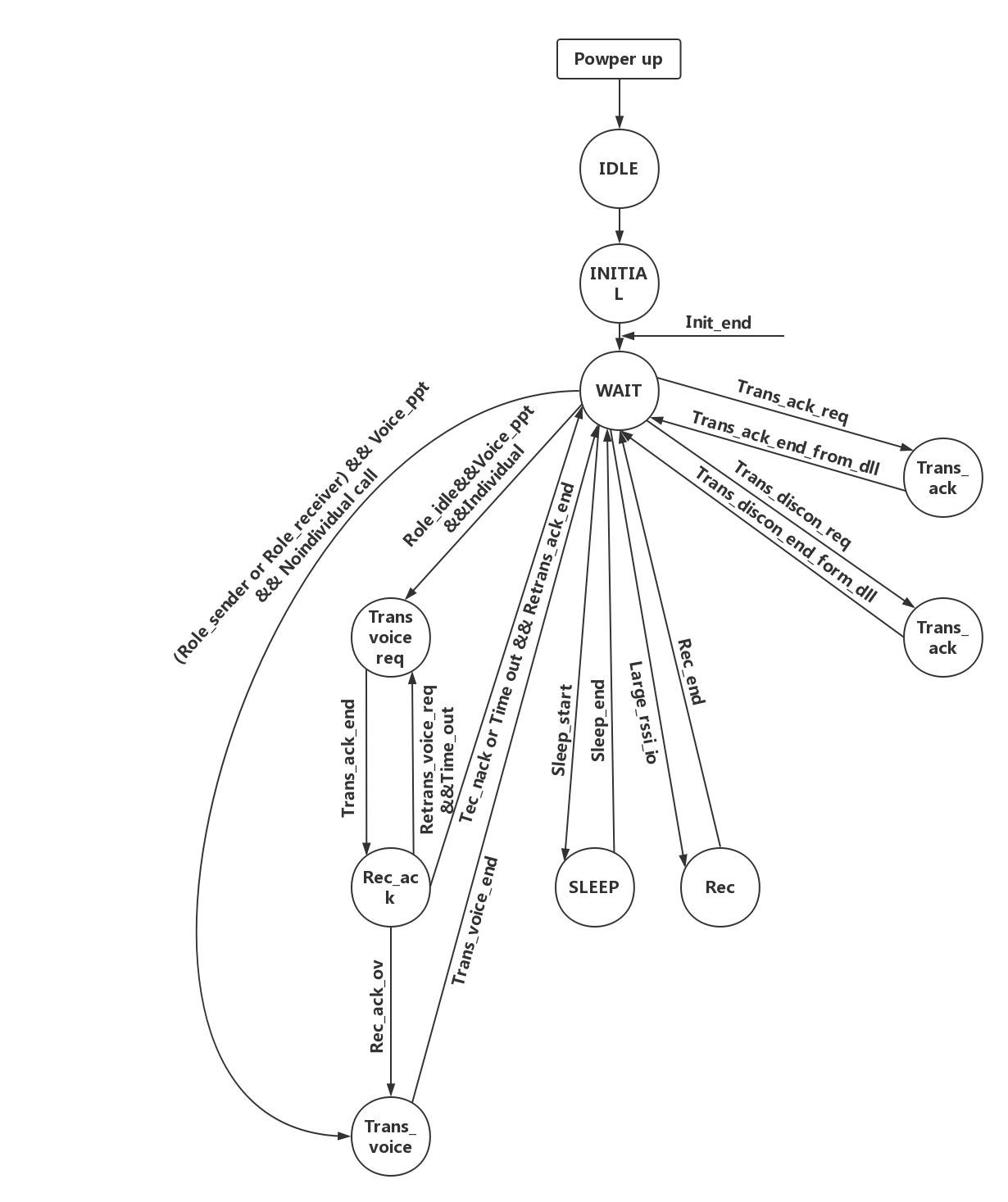

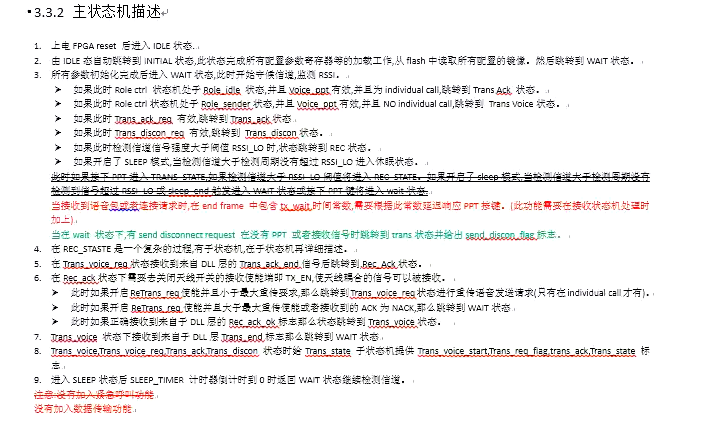

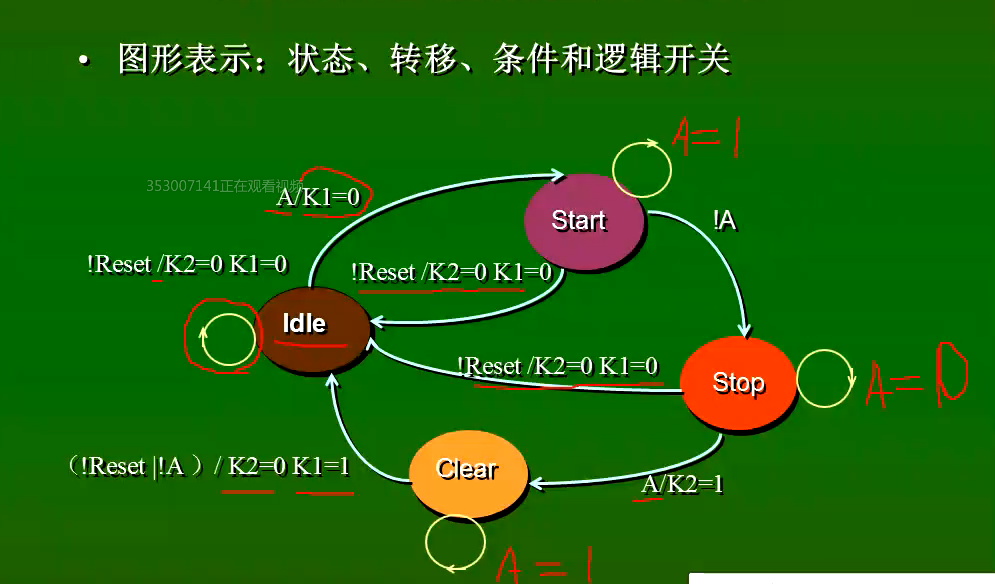

有限状态机框图如下:

3. 设计举例

根据上图代码实现:

//ex_fsm.v

module ex_fsm(

input wire sclk,

input wire rst_n,

output reg k1,//输出的时候可以作为寄存器,它相当于把输出寄存器的

output reg k2,//Q端直接连接到输出口了,就把中间那根线给省略了

input wire A//状态

);

parameter IDLE = 4'b0001;//4'h1十六进制,状态少的时候最好显示的写出状态表达式

parameter START = 4'b0010;

parameter STOP = 4'b0100;

parameter CLEAR = 4'b1000;

//reg [1:0] state;

//2'b00 2'b01 2'b10 2

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1531

1531

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?