名称:6人倒计时抢答器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

6人倒计时抢答器设计

1、具有复位、主持人主控按键,6个抢答按键

2、主持人控制开始,然后开始倒计时15秒

3、倒计时结束后报警,可以开始抢答

4、成功抢答者通过数码管显示编号

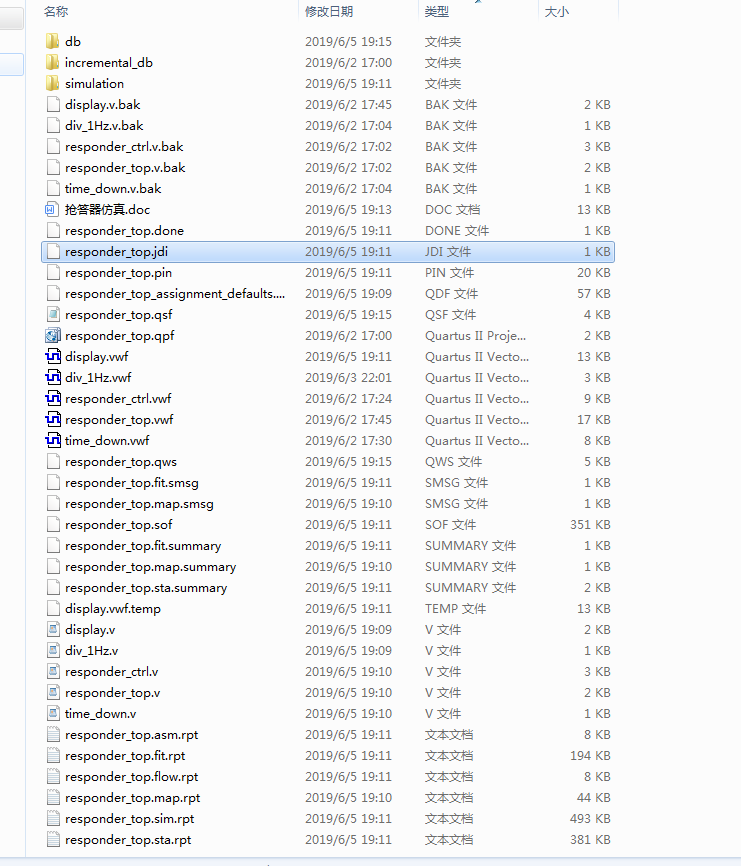

1. 工程文件

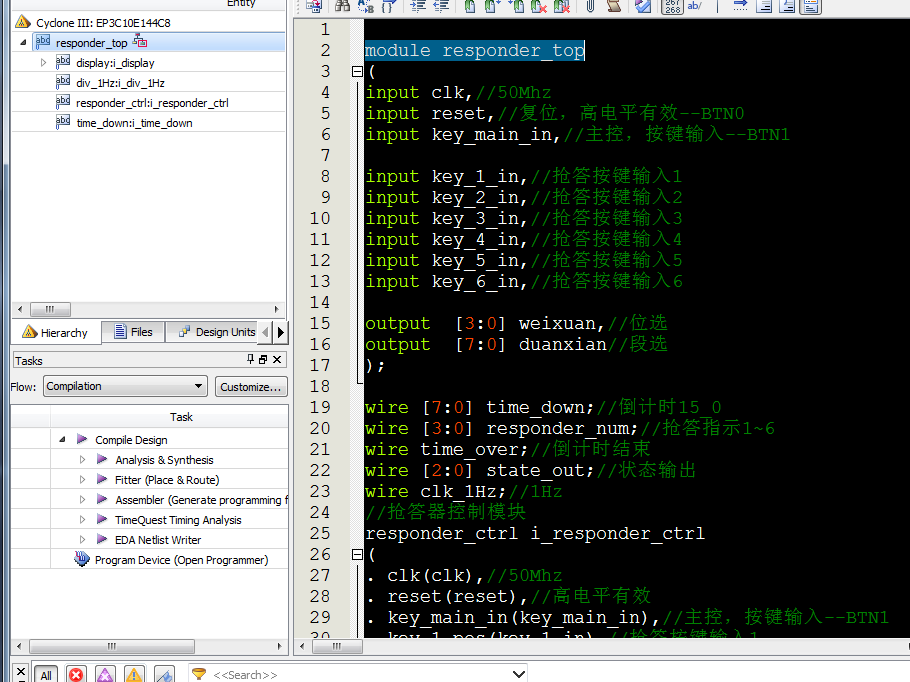

2. 程序文件

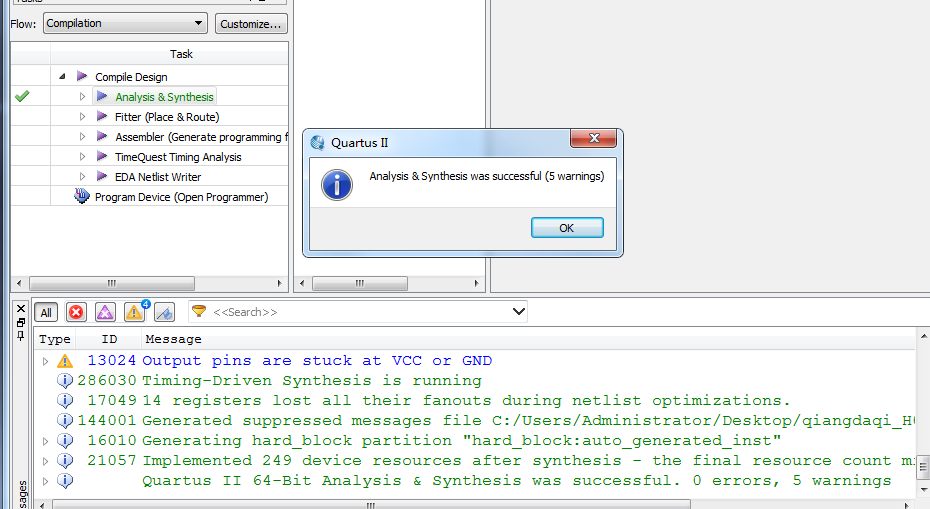

3. 程序编译

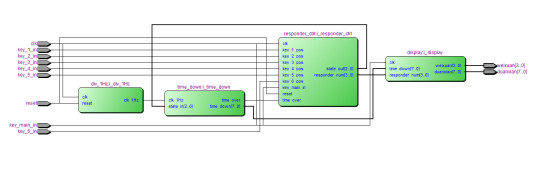

4. RTL图

5. 程序仿真

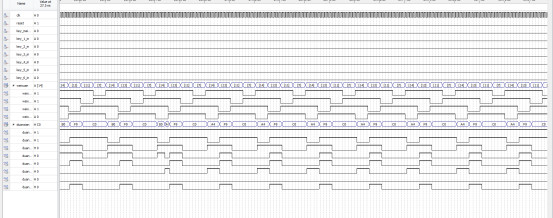

5.1 整体仿真

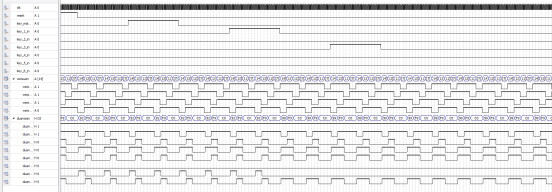

5.2 显示模块仿真

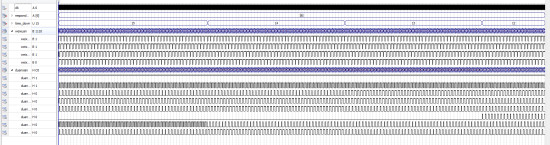

5.3 分频模块仿真

![]()

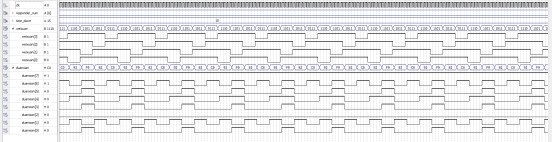

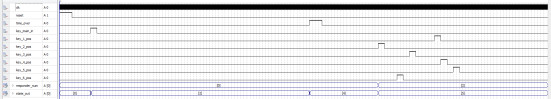

5.4 抢答控制模块仿真

5.5 倒计时模块仿真

部分代码展示:

module display ( input clk, input [7:0] time_down,//倒计时15_0 input [3:0] responder_num,//抢答指示1~6 output reg [3:0] weixuan,//位选,低亮 output reg [7:0] duanxian//段选,低亮 ); reg[15:0]jishu='d0; always@(posedge clk) begin jishu<=jishu+16'd1; end reg [3:0] display_data=4'd0; always@(posedge clk) begin case(jishu[4:3])//显示 2'd0:display_data<=time_down%10;//倒计时个位 2'd1:display_data<=time_down/10;//倒计时十位 2'd2:display_data<=responder_num;//抢答指示1~6 2'd3:display_data<=4'd0; default:; endcase end always@(posedge clk) begin case(jishu[4:3])//位选,低亮 2'd0: weixuan<=4'b1110; 2'd1: weixuan<=4'b1101; 2'd2: weixuan<=4'b1011; 2'd3: weixuan<=4'b0111; default:weixuan<=4'b1111; endcase case(display_data)//段选,低亮 0 : duanxian= (8'hc0); 1 : duanxian= (8'hf9); 2 : duanxian= (8'ha4); 3 : duanxian= (8'hb0); 4 : duanxian= (8'h99); 5 : duanxian= (8'h92); 6 : duanxian= (8'h82); 7 : duanxian= (8'hf8); 8 : duanxian= (8'h80); 9 : duanxian= (8'h90); endcase end endmodule

源代码

点击下方的公众号卡片获取

619

619

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?