AMD FPGA是电子器件中的万能芯片,在外设接口,算法指令,协议控制应用上能实现接近所有需求。AMD FPGA本身是创新引导者,同时也是工业医疗视觉,视频消费电子,通讯,测试仪器等技术创新团队强有力的后盾。

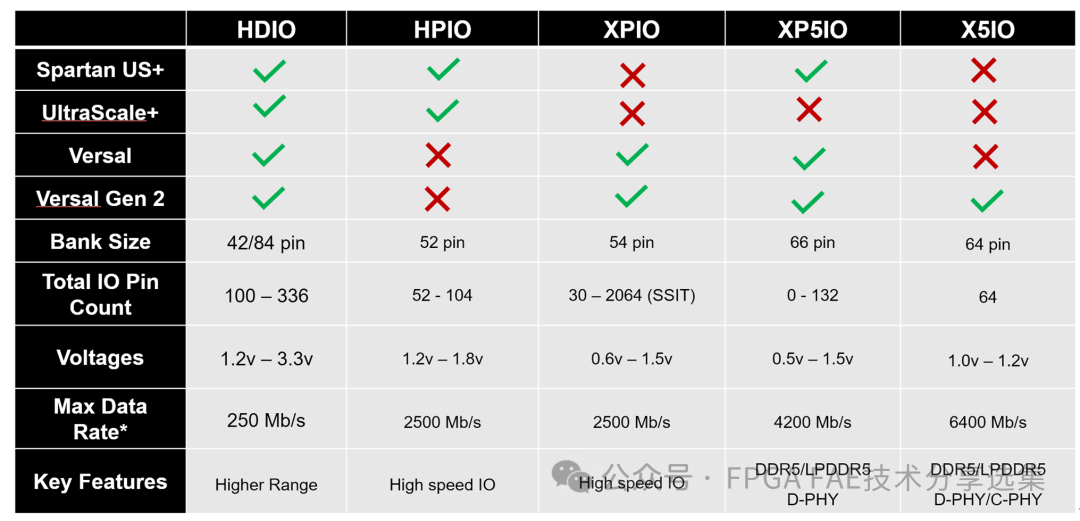

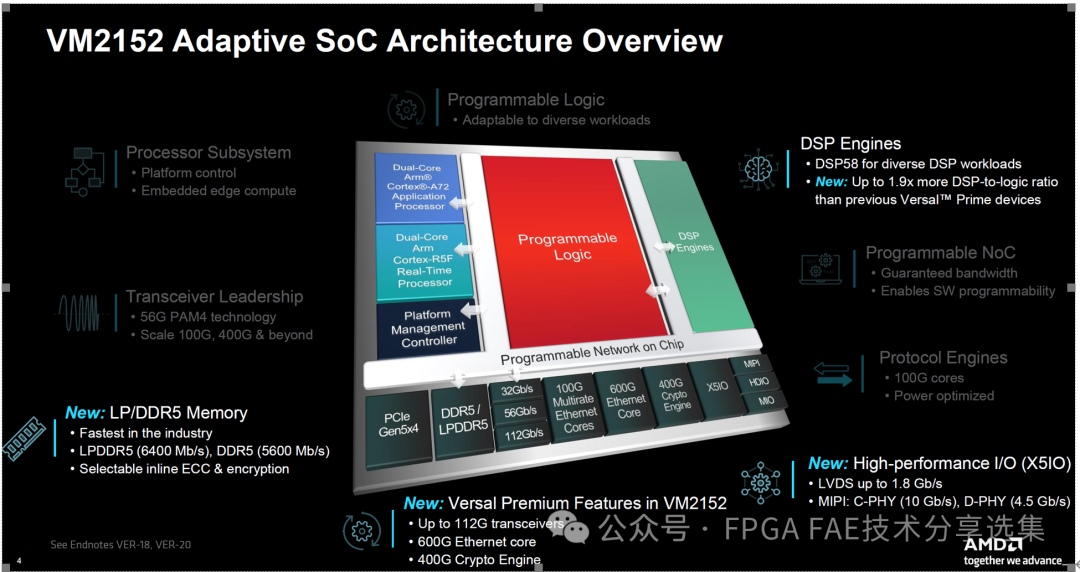

AMD FPGA接口丰富灵活,基本能跟基本所有电子外设连接通讯。新的X5IO在SelectIO 基础上增加对MIPI C-PHY\DDR5电平标准的支持,进一步提升接口性能。

AMD FPGA逻辑器件Bank分布

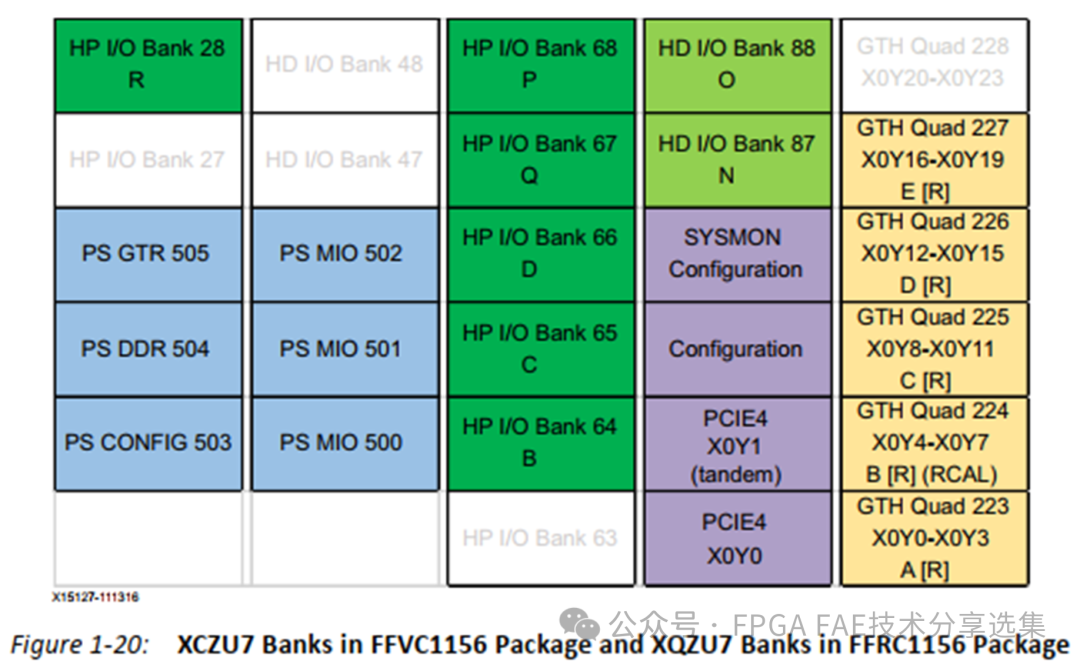

AMD 16nm&7nm FPGA器件主要包括HD IO\HP IO\XP IO\XP5IO\X5IO五类USER IO bank。如下图,ZCU106开发板16nm 器件XCZU7EV 逻辑部分包括两个HD IO bank88和bank87,六个HP IO bank是 bank28\bank64\bank65\bank66\bank67\bank68。

图一 XC7EV器件Bank分布

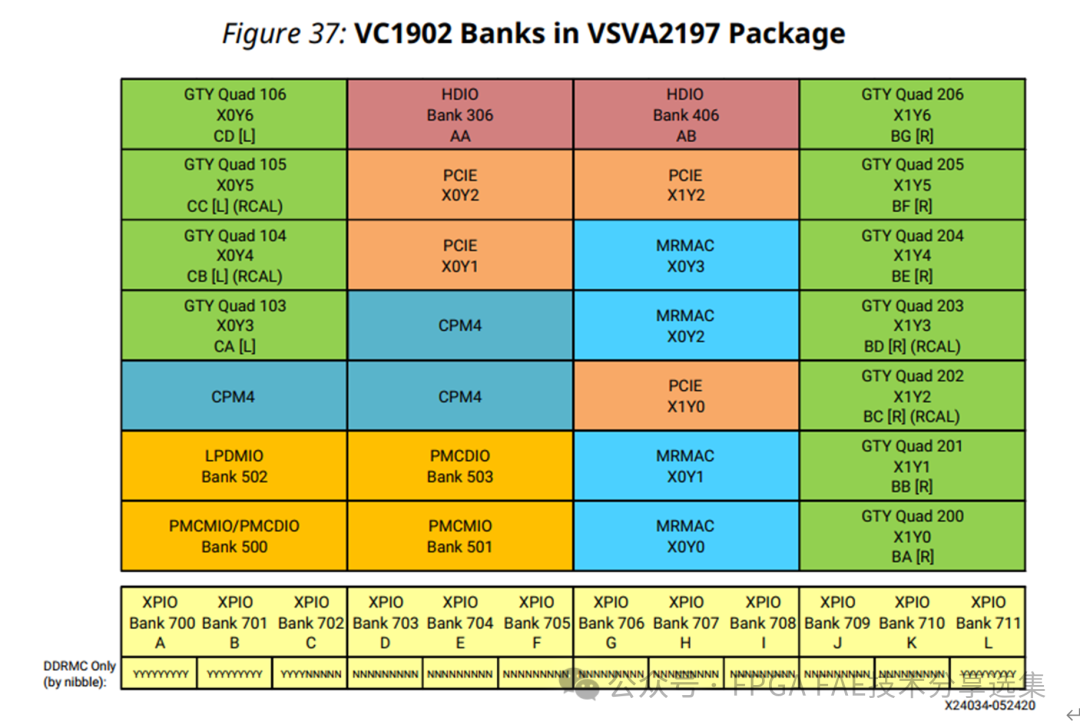

如下图,VCK190开发板7nm 器件XCVC1902-2MSEVSVA2197,包括两个HD IO bank306\bank406,十二个XP IO bank 70x。

图二 XCVC1902器件Bank分布

Spartan Ultrascale+器件引入XP5IO bank,新特性包括支持MIPI D-PHY 3200Mbps,支持LPDDR5 4200 Mb/s。Versal gen2器件引入X5IO bank,新特性包括支持MIPI D-PHY 4500Mbps,支持MIPI C-PHY 4500Mbps,支持LPDDR5 6400Mb/s。

图三 AMD FPGA器件User IO Bank支持

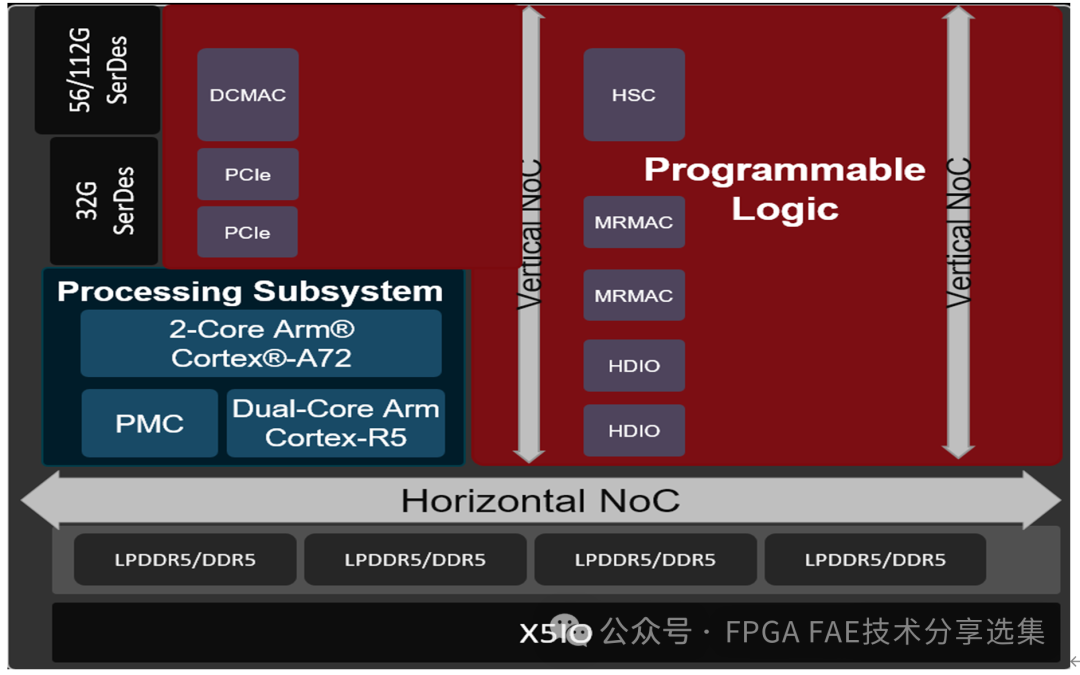

AMD Versal Gen2 X5IO简介

AMD Versal Gen2 X5IO bank在HP bank基础上面增加对LPDDR5\DDR5\MIPI C-PHY的支持。一个X5IO bank 包含64个User IO,X5PLL,CMPHY Octad,X5PHIO,支持的1.0V~1.2V范围的电平标准,分为两个x32 half bank。

图四 AMD Versal Gen2器件结构

图五 XPHY内部详细结构

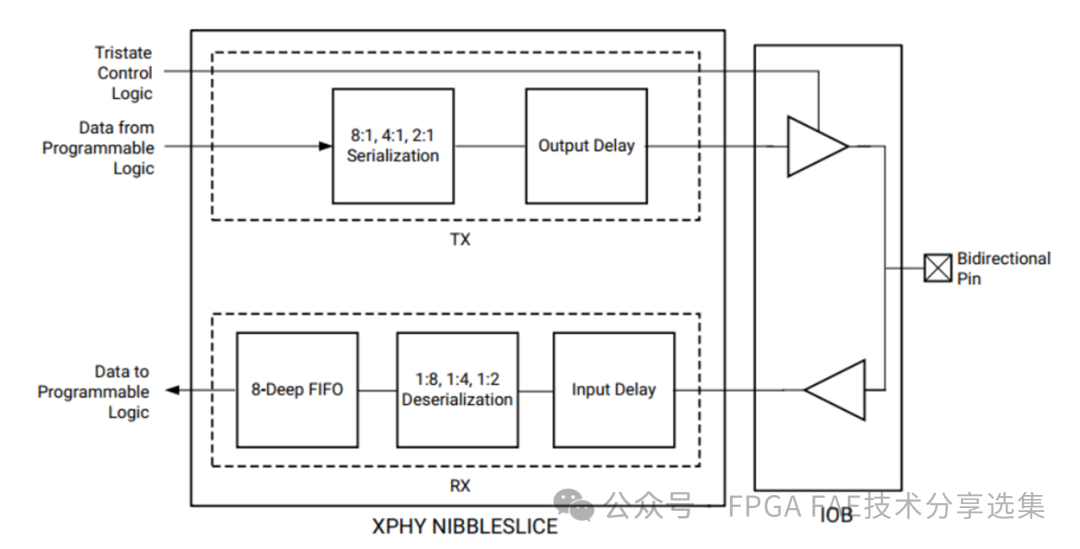

从图五XPHY内部详细结构可以看出,结构内部主要由一个8-Deep FIFO,用于输入x8 lane 同步。每组8 lane共用一个8-Deep FIFO,注意此FIFO非彼FIFO(Block RAM生成的逻辑内部36K bit FIFO),8-Deep FIFO就在XPHY 内部,可以消除8 lane之间的PCB不等长。原理图设计时候DDR controller x8 DQ要求在同一个Byte Group,MIPI X4 lane要求在一个Byte Group,主要原因就是一个Byte Group x8 lane 对应同一个8-Deep FIFO。User IO里面8-Deep FIFO同步技术性能非常强,LPDDR5 最高速率能达到6200Mb/s。

图五XPHY内部详细结构可以看出,右边主要由串化器&解串器,输入延迟组件&输出延迟组件组成。MIPI或者LVDS 接口一般有随路时钟+数据线组成,比如1050M bit/s的数据lane s速率 + 150M Hz的随路时钟,时钟信号传输速率不宜过高,抖动会比较大,一般数据输出的时候通过串化器把150Mbits x 7位宽的数据串化为1050M b/s,接收的时候把1050M bit/s解串为150M bit/s x7位宽的数据总线供FPGA内部逻辑处理。输入延迟组件(Input delay)&输出延迟(Output delay)组件主要用于消除PCB走线不等长,X5IO 最高支持1800MHz LVDS总线接口。Delay Controller只能管理同一个bank 的输入延迟组件(Input delay)&输出延迟(Output delay),需要使用IO delay组件的总线接口硬件设计的时候,要求在同一个bank,比如sensor 接入到FPGA最好同一组时钟数据线接入到同一bank。

MIPI C-PHY简介

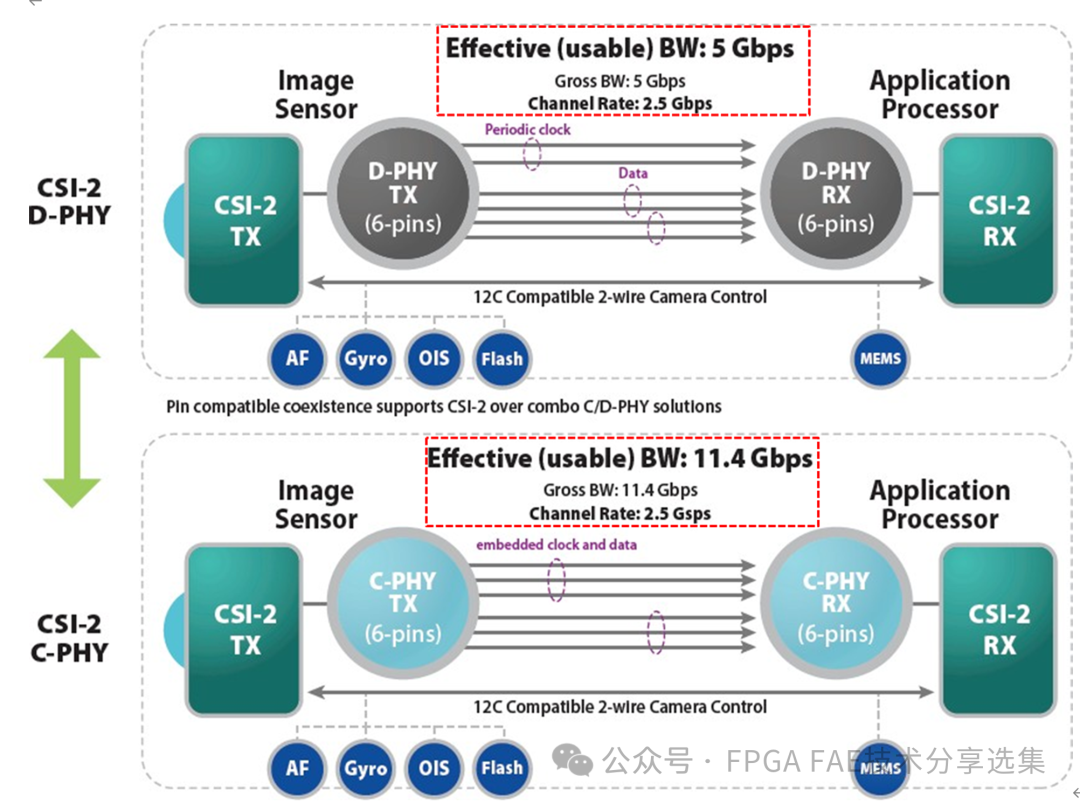

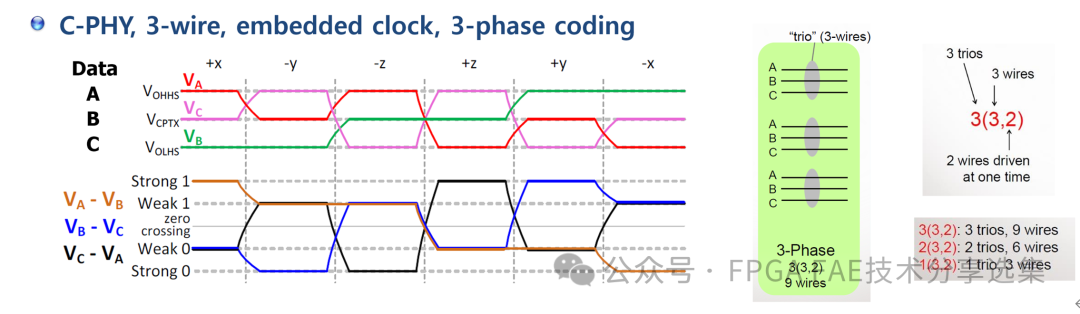

MIPI C-PHY是手机中的重要接口,它的速率比D-PHY还要高,其速率单位是symbol/s/lane,而D-PHY的速率单位是bit/s/lane,换算关系是1 Symbol = 2.28 bits。C-PHY和D-PHY在pin map上有个重要的区别:C-PHY没有单独的时钟通道,它的时钟隐藏在通信的时序之中。D-PHY是每条lane是一对差分线,而C-PHY每条lane是3条数据线,彼此差分。下图是使用3 lane的C-PHY接口链路示意图,一条lane包含3条信号线,3条信号线彼此做差分。C-PHY基于3-Phase symbol编码技术,通过three-wire trios传输2.28 bits/symbol,其目标速率是2.5Gsymbols/s。C-PHY与D-PHY有许多共同点,C-PHY的绝大部分特性都是从D-PHY改编而来的。C-PHY被设计成能够与D-PHY在同一个IC管脚上共存,从而可以开发出既支持C-PHY又支持D-PHY的双模器件。

图六 D-PHY VS C-PHY

MIPI C-PHY 通过带宽受限的通道提供高吞吐量,将显示器和摄像头连接到应用处理器。它为MIPI CSI-2和MIPI DSI-2生态系统提供PHY,使设计人员能够扩展实现支持各种更高分辨率的图像传感器和显示器,同时保持低功耗。同时它还可以应用于许多其他地方,例如汽车摄像头传感系统,防撞雷达,车载信息娱乐系统和仪表盘等。MIPI C-PHY是一种嵌入式时钟链路,可为链路内的重新分配通道提供极大的灵活性。C的真正含义是"C-PHYs may be used in channel-limited applications, hence the use of the character "C""。它还提供高速和低功耗模式之间的低延迟转换。MIPI C-PHY通过在双线通道上脱离传统的差分信号技术并引入大约2.28位/符号的三相符号编码来在三线通道上传输数据符号来实现这一点,其中每个通道包括嵌入式时钟。MIPI C-PHY可以与MIPI D-PHY在同一设备上引脚共存,因此设计人员可以开发双模设备。链路的操作和可用数据速率可以是不对称的,这使实现人员能够根据系统需求优化传输速率,支持双向和半双工操作。

C-PHY使用 3-Phase symbol encoding技术,每一个符号可以传输2.28bits数据。C-PHY复用了大部分D-PHY的标准,能和D-PHY在同一芯片中共存,但是其数据编码技术和D-PHY有本质的区别,其特性如下:

-

使用三根线一组传输,而不是之前使用的差分对;

-

采用5进制传输,效率高于D-PHY的二进制,效率为原来的2.27倍;

-

没有时钟信号,由于使用了三根线,并且时钟编码到每一个symbol中,而且在每一个symbol boundary都有电压的跳变,时钟恢复也比较简单。

图七 C-PHY电平

AMD Versal Prime 系列VM2152

Versal Prime VM2152 器件集成C\DPHY功能,具有高速 DDR 内存接口,支持 LPDDR5(高达 6400Mb/s)/DDR5(高达 5600Mb/s),112Gb/s 收发器以及增强的 DSP 功能 2(超过以前的Versal Prime 器件),轻松应对新一代通信、测量测试、存储以及其它各种市场应用所需的更高数据吞吐量。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?