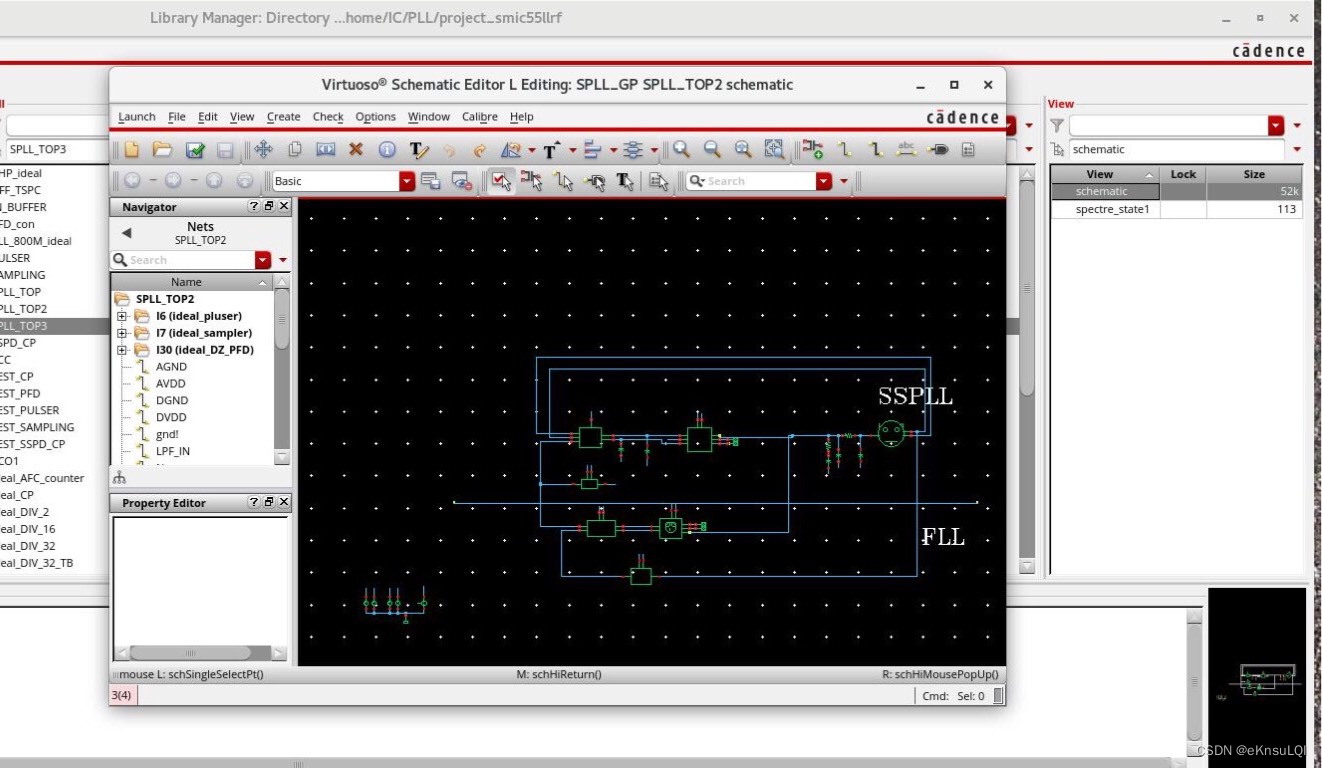

SSPLL亚采样锁相环,锁相环进阶

Verilog-A建模非实际电路,有仿真testbench,可以直接跑,非常适合新手入门

可以送Simmulink建模好的sspll

SSPLL亚采样锁相环是一种常见的时钟生成电路。锁相环(Phase-Locked Loop, PLL)是一种用于生成稳定时钟信号的电路,它由相位比较器、积分器、低通滤波器和控制电压源等组成。SSPLL是一种亚采样锁相环(Sub-Sampling PLL),它通过亚采样技术在输入信号的每个周期内只采样一次,大大降低了采样频率,从而减少了功耗和器件的要求。

Verilog-A是一种常用的模拟电路建模语言,它可以用于对电路进行精确的仿真分析,为设计者提供了快速、准确的电路行为描述。在SSPLL的设计过程中,Verilog-A的使用非常重要。设计者可以使用Verilog-A语言对SSPLL的各个组成部分进行建模,同时还可以编写仿真testbench进行验证。这样一来,设计者可以快速得到SSPLL的性能参数,例如锁定范围、抖动、功耗等,为后续的优化提供参考。

对于新手来说,Verilog-A建模非常适合作为入门学习的工具。相对于其他建模语言,Verilog-A语法简洁明了,易于理解和掌握。同时,Verilog-A提供了丰富的内置函数和模块,方便新手快速构建复杂的电路模型。通过编写Verilog-A模型并搭建仿真环境,新手可以全面了解SSPLL的工作原理和性能特点,为后续的设计工作打下坚实的基础。

除了Verilog-A建模,Simulink也是一种常见的建模工具。对于那些不熟悉Verilog-A语言的设计者来说,可以直接使用Simulink进行SSPLL的建模。Simulink提供了直观的图形界面,设计者只需要通过拖拽和连接模块来构建SSPLL的模型,无需编写代码。同时,Simulink还提供了丰富的信号处理和控制系统库,方便设计者快速搭建复杂的SSPLL模型。对于一些初学者来说,Simulink可以帮助他们更快地理解SSPLL的原理和构造,加速学习和设计的过程。

总结来说,SSPLL亚采样锁相环是一种常见的时钟生成电路,在数字系统中具有广泛的应用。Verilog-A建模和Simulink建模是针对SSPLL设计的两种常用方法。Verilog-A建模可以提供精确的电路行为描述,通过仿真testbench验证设计性能;Simulink建模则方便新手入门,通过直观的图形界面搭建SSPLL模型。无论是哪种建模方法,都可以帮助设计者更好地理解和设计SSPLL电路,为实际应用提供支持。

相关代码,程序地址:http://imgcs.cn/lanzoun/726503327440.html

484

484

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?