PCIe规范由PCISIG组织进行发布的,PCISIG其英文全称为:Peripheral Component Interconnect Special Interest Group(外围部件互连专业组),简称PCISIG。

该组织拥有并管理着开放式行业标准——PCI规范。随着行业的I/O需求的发展,该组织负责定义和实现新的行业标准I/O(输入/输出)规范。目前,全球共有900多家业界领先公司成为了PCI-SIG成员。

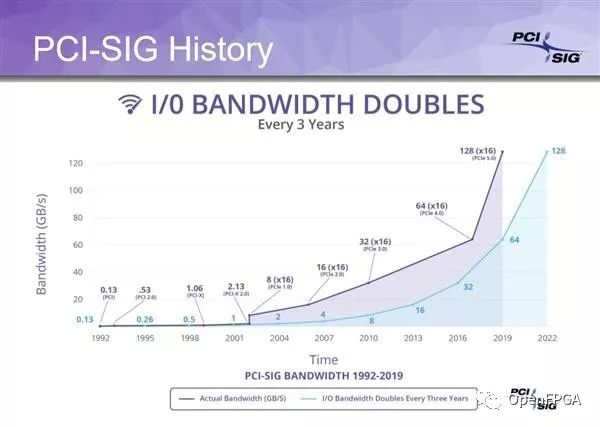

看下PCIe发展历程:

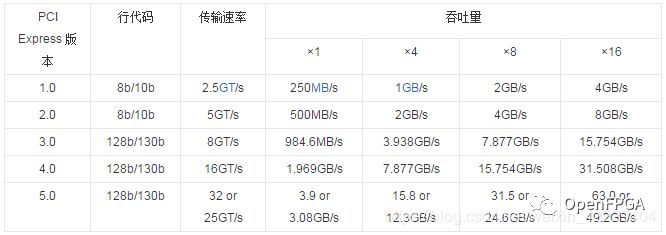

PCIE相关概念:

传输速率为每秒传输量GT/s,而不是每秒位数Gbps,因为传输量包括不提供额外吞吐量的开销位; 比如 PCIe 1.x和PCIe 2.x使用8b / 10b编码方案,导致占用了20% (= 2/10)的原始信道带宽。

GT/s —— Giga transation per second (千兆传输/秒),即每一秒内传输的次数。重点在于描述物理层通信协议的速率属性,可以不和链路宽度等关联。

Gbps —— Giga Bits Per Second (千兆位/秒)。GT/s 与Gbps 之间不存在成比例的换算关系。

PCIE带宽计算

PCIe 吞吐量(可用带宽)计算方法:

吞吐量 = 传输速率 * 编码方案

例如:PCI-e2.0 协议支持 5.0 GT/s,即每一条Lane 上支持每秒钟内传输 5G个Bit;但这并不意味着 PCIe 2.0协议的每一条Lane支持 5Gbps 的速率。

为什么这么说呢?因为PCIe 2.0 的物理层协议中使用的是 8b/10b 的编码方案。 即每传输8个Bit,需要发送10个Bit;这多出的2个Bit并不是对上层有意义的信息。

那么, PCIe 2.0协议的每一条Lane支持 5 * 8 / 10 = 4 Gbps = 500 MB/s 的速率。

以一个PCIe 2.0 x8的通道为例,x8的可用带宽为 4 * 8 = 32 Gbps = 4 GB/s。

同理,

PCI-e3.0 协议支持 8.0 GT/s, 即每一条Lane 上支持每秒钟内传输 8G个Bit。

而PCIe 3.0 的物理层协议中使用的是 128b/130b 的编码方案。 即每传输128个Bit,需要发送130个Bit。

那么, PCIe 3.0协议的每一条Lane支持 8 * 128 / 130 = 7.877 Gbps = 984.6 MB/s 的速率。

一个PCIe 3.0 x16的通道,x16 的可用带宽为 7.877 * 16 = 126.031 Gbps = 15.754 GB/s。

由此可计算出上表中的数据

目前,仅有Intel的企业级SLC固态盘Ruler SSD直接以PCIe 5.0规范做传输设计。

为应对各领域日益增长的超高速带宽需求,英特尔推出了全新的互联协议Compute EXpress Link(CXL),面向超极数据中心,高性能计算和AI等领域,可有效解决未来所遇到的负载瓶颈。

据了解,Compute Express Link(CXL)1.0协议能帮助CPU与GPU、FPGA或其他加速器之间实现高效高速互联,带来更高的带宽和更好的内存一致性。CXL基于PCIe 5.0基础上打造,采用常规PCI-Express接口,并向下兼容当前设备,不用通过专门接口也能实现很好兼容,大大简化服务器硬件设计难度,降低了整体系统成本。

具体性能表现未透露,不过已知PCIe 5.0理论带宽速率是PCIe gen 4.0两倍(单通道32Gbps),毋庸置疑CXL 1.0的到来势必会大大提升平台性能。

与此同时,英特尔还宣布与华为、思科、戴尔易安信、Facebook、阿里巴巴集团、谷歌、惠普以及微软等成立共同合作发展联盟,与联盟成员共享技术成果,并共同持续开发。

文档下载地址

链接: https://pan.baidu.com/s/1bllfs4Bivk8I8ZcjQSA6GA

提取码: zgi2

1565

1565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?