本文以K9F1208为例:

一:nandflash 原理以及介绍

NAND FLASH以页(page)为单位进行读写,以块(block)为单位进行擦除。

1.nand flash的引脚

I/O0~I/O7:数据输入输出,主要用于输入命令,地址,数据和读操作时候输出数据

CLE:命令锁存使能,当高电平有效和WE在上升沿时,命令将被锁存在命令寄存器中。

ALE:地址锁存使能,当ALE为高且we在上升沿时,地址将被锁存。

WP:写保护。

当写入命令或地址时,都需将CE(片选)和WE(写使能)信号拉低,数据在WE信号的上升沿被NAND FLASH锁存。ALE,CLE用来分辨锁存命令或者地址。

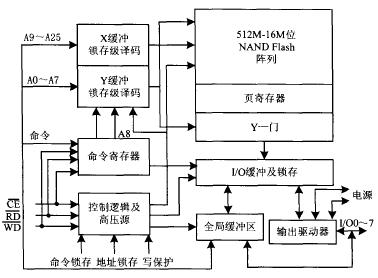

2:内部功能结构图:

X缓冲锁存:用于行(页)地址

y缓冲锁存:用于列地址

页寄存器:用于数据缓存,当读写某页的时,会将数据先读入/写入此寄存器,大小为528字节。当读数据时,先从NAND FLASH内存单元把数据读到页寄存器,外部通过访问NAND FLASH I/O端口获得页寄存器中数据(地址自动累加);当写数据时,外部通过NAND FLASH I/O端口输入的数据首先缓存在页寄存器,写命令发出后才写入到内存单元中

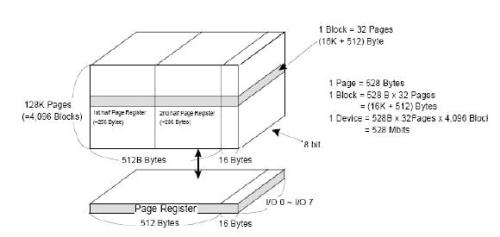

3.nandflash存储单元组织结构:

由图上可值知:每页(行)大小为512字节,外加16字节的额外空间。512B用于存放数据,16B用于存放其他信息(块好坏的标记、块的逻辑地址、页内数据的ECC校验和等)

4。nandflash操作

操作nand flash时,先传输命令,然后再传输地址,最后读写数据。

根据k9f1208的组织方式可以分四类地址: Column Address、halfpage pointer、Page Address 、Block Address。A[0:25]表示数据在64M空间中的地址。

Column Address:表示数据在半页中的地址,大小范围0~255,用A[0:7]表示;

halfpage pointer:表示半页在整页中的位置,即在0~255空间还是在256~511空间,用A[8]表示;A[8]=00,为上半页,=01为下半页

Page Address表示页在块中的地址,大小范围0~31,用A[13:9]表示;

Block Address表示块在flash中的位置,大小范围0~4095,A[25:14] 表示

4.1 read1:通过将00h、01h指令写入指令寄存器,接着写入3个地址(1个列地址,2个行地址)来启动。一旦页读指令被器件锁存,下面的页读操作就不需要再重复写入指令了。写入指令和地址后,处理器可以通过对信号线R/B的分析来判断该操作是否完成。

4.2 read2:发出命令字节50H,4个地址序列,等待R/B引脚为高电平,最后读取数据。此时读取的数据为512~527的数据。

4.3 复位指令:发出命令为FFH,终止当前操作,指令寄存器被清零,等待下一条的操作。

4.4 page program:写入必须在擦除之后,否则写入将出错.分为2个周期完成,发出80H后,紧接着是4个地址序列,然后向flash中发送数据。它们首先被写入器件内的页寄存器,然后发出10H命令启动内部写命令。内部写入操作开始后,器件自动进入“读状态寄存器”模式。在这一模式下,当RE和CE为低电平时,系统可以读取状态寄存器。可以通过检测R/B的输出,或读状态寄存器的状态位(I/O 6)来判断内部写入是否结束。在器件进行内部写入操作时,只有读状态寄存器指令和复位指令会被响应。当页写入操作完成,应该检测写状态位(I/O 0)的电平。

4.5 块擦出:命令字节为60H和D0H,此时地址为A14~A25有效。a9~a13被忽略。

二:s3c2440中的nandflash 控制寄存器:

1:相关寄存器:

NFCONF:配置寄存器:用来设置时序参数TACLS,TWRPH0,TWRPH1,数据位宽等

NFCONT:控制寄存器:用来设置使能或禁止nandflash控制器、控制引脚信号,初始化ECC

NFCMMD:命令寄存器:

NFADDR:地址寄存器:当写这个寄存器时,将向FLASH发送地址信号

NFDATA:数据寄存器:只用到低8位,读写此寄存器将启动对nandflash的读写数据操作

NFMECCD0/1:主数据区域ECC寄存器:

NFSECCD:空闲区域寄存器:

NFSTAT:操作状态寄存器:0:busy 1:ready

2:读写操作次序:

设置NFCONF,NFCONT,向NFCMMD寄存器中写入命令,向NFADDR中写入地址。

读写数据:通过寄存器NFSTAT检测nandflash的状态,在启动某个操作后,应该检测rb信号以确认该操作时候完成,时候成功。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?