在源代码中调用UINFO表示一定debug等级下的打印,消息等级3以及低等级只需要标记 "--debug" 就可以,更高等级需要 "--debugi<level>" 控制。单个文件的等级可以通过 "-debugi-<srcfile> <level>"来控制,例如:"--debug --debugi 5 --debugi-V3Width 9",则对于其他文件采用默认的等级5调试,而V3Width.cpp文件,调试等级是9。

debug测试

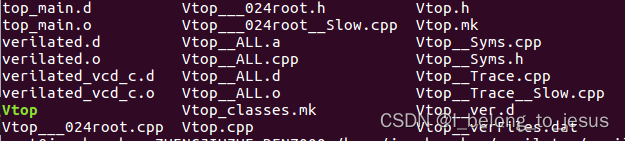

当运行时使用 "--debug"时,在obj_dir文件夹将会有两类主要的输出文件,.tree和.dot文件。我们以第一节的例子来测试,在不加"--debug"的情况下执行:

verilator -Wall top.v top_main.cpp --cc --trace --exe --buildobj_dir文件夹下内容如下

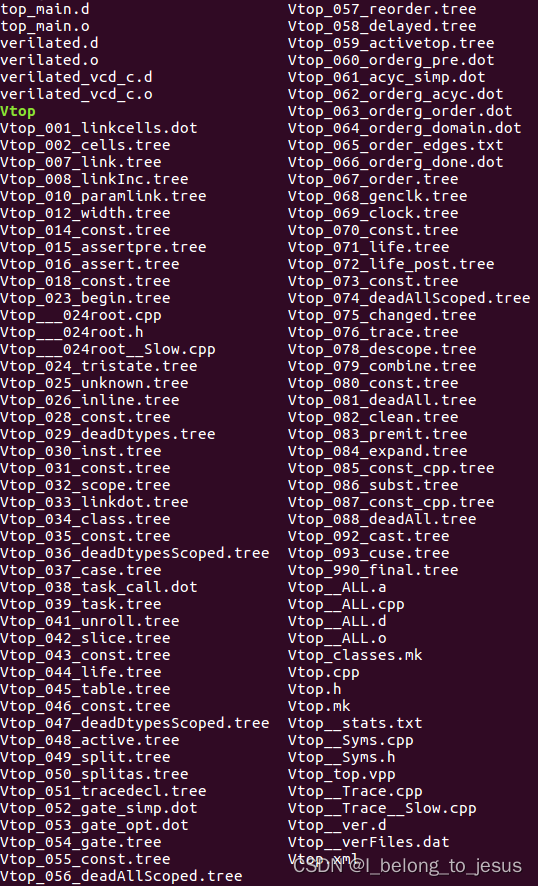

如果加上"--debug"

verilator -Wall top.v top_main.cpp --cc --trace --exe --build --debug,则

.dot文件

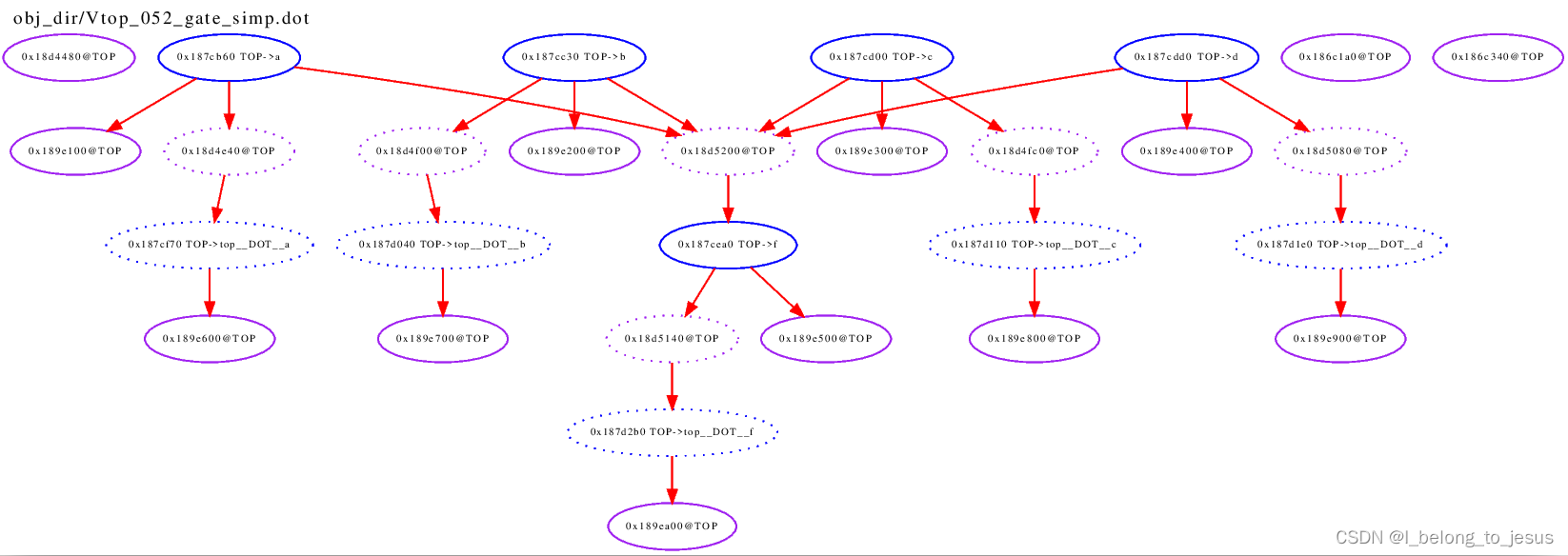

dot文件是内部图(internal graph)的dump(在计算机中,dump的中文意思为“转储”,一般指将数据导出、转存成文件或静态形式,即将动态(易失)的数据,保存为静态的数据(持久数据)),以Graphviz<https://www.graphviz.org>`__ dot 格式存储。 可以进一步将dot格式转为图片格式,例如.ps格式:

dot -Tps -o obj_dir/Vtop_052_gate_simp.ps obj_dir/Vtop_052_gate_simp.dot生成的Vtop_052_gate_simp.ps图片文件为:

对于交互图(interactive graph),可以使用工具

`xdot <https://github.com/jrfonseca/xdot.py>`__ 或者 `ZGRViewer

<http://zvtm.sourceforge.net/zgrviewer.html>`__。

.tree文件

树文件作为AST(抽象语法树)的dump,在每一个主要算法之间都会生成,例如:

NETLIST 0x90fb00 <e1> {a0ah}

1: MODULE 0x912b20 <e8822> {a8ah} top L2 [P]

*1:2: VAR 0x91a780 <e74#> {a22ah} @dt=0xa2e640(w32) out_wide [O] WIRE

1:2:1: BASICDTYPE 0xa2e640 <e2149> {e24ah} @dt=this(sw32) integer kwd=integer range=[31:0下面详细总结了上面的dump例子,每一个域都给出了更详细的解释:

+---------------+--------------------------------------------------------+

| ``1:2:`` | The hierarchy of the ``VAR`` is the ``op2p`` |

| | pointer under the ``MODULE``, which in turn is the |

| | ``op1p`` pointer under the ``NETLIST`` |

+---------------+--------------------------------------------------------+

| ``VAR`` | The AstNodeType (e.g. ``AstVar``). |

+---------------+--------------------------------------------------------+

| ``0x91a780`` | Address of this node. |

+---------------+--------------------------------------------------------+

| ``<e74>`` | The 74th edit to the netlist was the last |

| | modification to this node. |

+---------------+--------------------------------------------------------+

| ``{a22ah}`` | This node is related to the source filename |

| | "a", where "a" is the first file read, "z" the 26th, |

| | and "aa" the 27th. Then line 22 in that file, then |

| | column 8 (aa=0, az=25, ba=26, ...). |

+---------------+--------------------------------------------------------+

| ``@dt=0x...`` | The address of the data type this node contains. |

+---------------+--------------------------------------------------------+

| ``w32`` | The data-type width() is 32 bits. |

+---------------+--------------------------------------------------------+

| ``out_wide`` | The name() of the node, in this case the name of the |

| | variable. |

+---------------+--------------------------------------------------------+

| ``[O]`` | Flags which vary with the type of node, in this |

| | case it means the variable is an output. |

+---------------+--------------------------------------------------------+一些通用的dump(AstNode::dump()生成):

Tree Hierarchy

The dump lines begin with numbers and colons to indicate the child

node hierarchy. As noted above, ``AstNode`` has lists of items at the

same level in the AST, connected by the ``nextp()`` and ``prevp()``

pointers. These appear as nodes at the same level. For example after

inlining:

::

NETLIST 0x929c1c8 <e1> {a0} w0

1: MODULE 0x92bac80 <e3144> {e14} w0 TOP_t L1 [P]

1:1: CELLINLINE 0x92bab18 <e3686#> {e14} w0 v -> t

1:1: CELLINLINE 0x92bc1d8 <e3688#> {e24} w0 v__DOT__i_test_gen -> test_gen

...

1: MODULE 0x92b9bb0 <e503> {e47} w0 test_gen L3

...

AstNode type

The textual name of this node AST type (always in capitals). Many of

these correspond directly to Verilog entities (for example ``MODULE``

and ``TASK``), but others are internal to Verilator (for example

``NETLIST`` and ``BASICDTYPE``).

Address of the node

A hexadecimal address of the node in memory. Useful for examining

with the debugger. If the actual address values are not important,

then using the ``--dump-tree-addrids`` option will convert address

values to short identifiers of the form ``([A-Z]*)``, which is

hopefully easier for the reader to cross reference throughout the

dump.

Last edit number

Of the form ``<ennnn>`` or ``<ennnn#>`` , where ``nnnn`` is the

number of the last edit to modify this node. The trailing ``#``

indicates the node has been edited since the last tree dump (which

typically means in the last refinement or optimization pass). GDB can

watch for this, see << /Debugging >>.

Source file and line

Of the form ``{xxnnnn}``, where C{xx} is the filename letter (or

letters) and ``nnnn`` is the line number within that file. The first

file is ``a``, the 26th is ``z``, the 27th is ``aa`` and so on.

User pointers

Shows the value of the node's user1p...user5p, if non-NULL.

Data type

Many nodes have an explicit data type. "@dt=0x..." indicates the

address of the data type (AstNodeDType) this node uses.

If a data type is present and is numeric, it then prints the width of

the item. This field is a sequence of flag characters and width data

as follows:

- ``s`` if the node is signed.

- ``d`` if the node is a double (i.e a floating point entity).

- ``w`` always present, indicating this is the width field.

- ``u`` if the node is unsized.

- ``/nnnn`` if the node is unsized, where ``nnnn`` is the minimum

width.

Name of the entity represented by the node if it exists

For example for a ``VAR`` it is the name of the variable.

Many nodes follow these fields with additional node specific

information. Thus the ``VARREF`` node will print either ``[LV]`` or

``[RV]`` to indicate a left value or right value, followed by the node

of the variable being referred to. For example:

::

1:2:1:1: VARREF 0x92c2598 <e509> {e24} w0 clk [RV] <- VAR 0x92a2e90 <e79> {e18} w0 clk [I] INPUT

In general, examine the ``dump()`` method in ``V3AstNodes.cpp`` of the node

type in question to determine additional fields that may be printed.

The ``MODULE`` has a list of ``CELLINLINE`` nodes referred to by its

``op1p()`` pointer, connected by ``nextp()`` and ``prevp()`` pointers.

Similarly the ``NETLIST`` has a list of modules referred to by its

``op1p()`` pointer.

本文介绍了如何在Verilator源代码中通过`--debug`标志控制调试级别,着重讲解了.dot和.tree文件的生成及其在AST和交互图上的应用。通过实例演示了debug模式下obj_dir文件夹的内容变化,以及如何将dump信息转化为易于理解的图表。

本文介绍了如何在Verilator源代码中通过`--debug`标志控制调试级别,着重讲解了.dot和.tree文件的生成及其在AST和交互图上的应用。通过实例演示了debug模式下obj_dir文件夹的内容变化,以及如何将dump信息转化为易于理解的图表。

362

362

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?