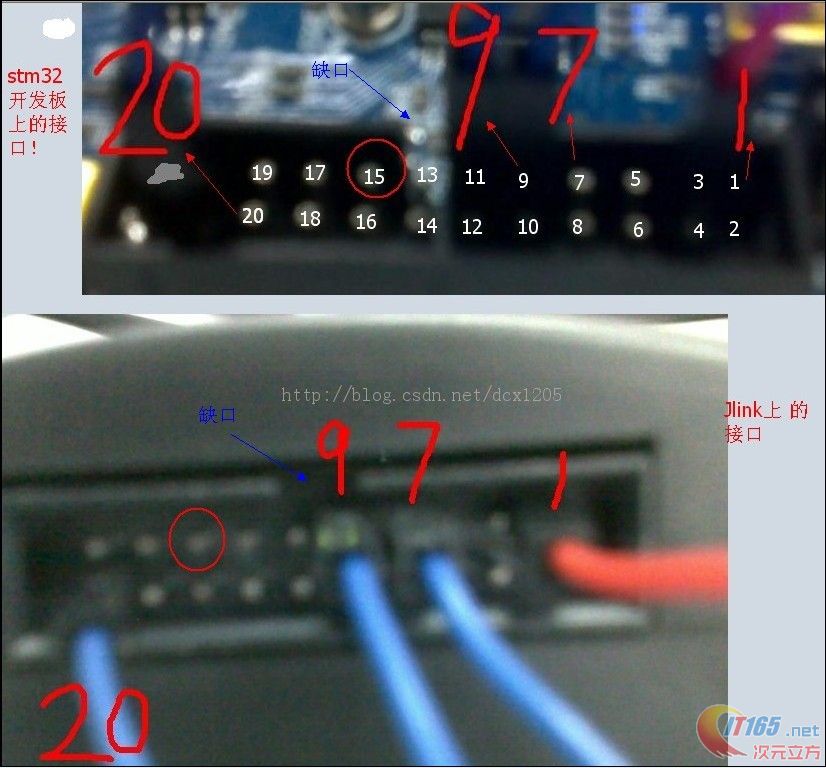

因为项目开发需要,采用SWD模式下载STM32,以前都是用JLINKv8 的JTAG模式,而且从未认真识别过JLINKv8各引脚。只知道SWD模式下和JTAG模式下共用两个引脚而已。只有明确了v8的各引脚定义才可以自己用杜邦线取其中的几个引脚作SWD模式的下载!!!

实际测试,当JATG正面拿在手里时,即缺口在上方。1、2引脚代表VDD。4、6、8、10、12、14、16、18、20引脚都为VSS。

3:JTRST 5:JTDI 7:JTMS 9:JTCK 11:NC 13:JTDO 15: RESET(通常接单片机的NRSET脚) 17/19:NC

一:当采用JTAG模式下载时,用到3、5、7、9和1:VDD及某个地引脚。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3014

3014

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?