**

1.1信号在PCB上传播速度原因

**

通常情况下我们对时序有要求的信号都要做等长处理,保证一组信号的长度大致相同。等长的目的是为了信号达到接收端的时间一致,需要关注的是时延不是等长长度。

长度相同并不代表着时延也相同。比如一段路程,两个汽车以不同的速度行驶,肯定到达的时间也不一样。问题的原因就是信号线在PCB的传播速度不同导致的。

影响PCB上信号的传播速度就是介电常数

。

信号线在表层时,一部分磁场穿过绿油和空气,导致有效介电常数减小,所以信号线在表层的传输速度快。

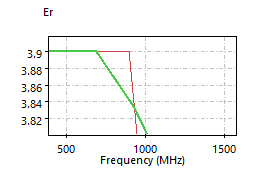

高频时,介电常数小,低频介电常数大些。下图是FR4板材介电常数跟频率的关系图。

1,.2仿真验证

建立传输线模型,分别仿真表层走线和内层走线

仿真结果显示,表层走线跟内层走线相差近80ps,FR4板材介电常数为4,根据上面的公式传输速度为6in/ns. 相差80ps相当于480mil。

我们在实际PCB板上提取S参数,看看情况:下面的三种情况分别模拟了BGA芯片三种出线情况,明显看到有时延。

这就是我们平时所说的,为什么要同组同层的原因。信号走线内层之间切换影响不大,但是表层内层之间切换时延较大。

对于那些需要时序要求的线,做扇孔的也要主要尽量保证扇出线的长度大致相同。

1727

1727

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?